完善資料讓更多小伙伴認識你,還能領取20積分哦,立即完善>

電子發燒友網技術文庫為您提供最新技術文章,最實用的電子技術文章,是您了解電子技術動態的最佳平臺。

在高速PCB數字電路系統中,傳輸線上阻抗不匹配會造成信號反射,并出現過沖、下沖和振鈴等信號畸變,而當傳輸線的時延TD大于信號上升時間RT的20%時,反射的影響就不能忽視了,不然將帶來信號完整性問題。減小反射的方法為;根據傳輸線的特性阻抗在其驅動端串聯電阻使源阻抗與傳輸線阻抗匹配,或者在接收端并聯電阻...

借助功能強大的Cadence公司SPEECTRAQuest仿真軟件,利用IBIS模型,對高速信號進行信號完整性仿真分析是一種高效可行的分析方法,可以發現信號完整性問題,根據仿真結果在信號完整性相關問題上做出優化的設計,從而達到提高設計質量,縮短設計周期的目的。...

PCB互連設計技術包括測試、仿真以及各種相關標準,其中測試是驗證各種仿真分析結果的方法和手段。優秀的測試方法和手段是保證PCB互連設計分析的必要條件,對于傳統的信號波形測試,主要應當關注的是探頭引線的長度,避免Pigtail引入不必要的噪聲。...

信號完整性主要指信號在信號線上傳輸的質量1當電路信號能以要求的時序( timing) 、持續時間和電壓幅值到達接收芯片的引腳時,該電路就有好的信號完整性。當信號不能正常響應或信號質量不能使系統長期穩定工作時,就出現了信號完整性問題。信號完整性問題主要表現為:延遲、反射、過沖、振鈴、串擾、時序、同步切...

選擇PCB板材必須在滿足設計需求和可量產性及成本中間取得平衡點。設計需求包含電氣和機構這兩部分。通常在設計非常高速的PCB板子(大于GHz 的頻率)時這材質問題會比較重要。例如,現在常用的FR-4 材質,在幾個GHz 的頻率時的介質損(dielectric loss)會對信號衰減有很大的影響,可能就...

本次設計中高速數據采集板的技術指標如下:a)垂直分辨率12bit;b)雙通道同時工作交替采樣,單通道采樣率為500MSPS;c)有效分辨率位數大于等于10bits;d)信噪比SNR》62dB。該采集板系統的主要器件有ADC芯片,時鐘芯片和通道上的模擬放大器和濾波器。...

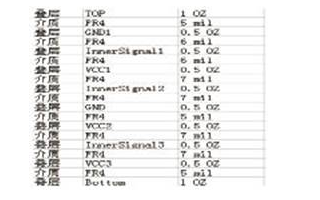

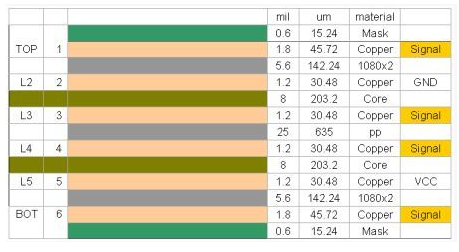

通常多層板最外面的兩個介質層都是浸潤層,在這兩層的外面使用單獨的銅箔層作為外層銅箔。外層銅箔和內層銅箔的原始厚度規格,一般有0.5OZ、1OZ、2OZ(1OZ約為35um或1.4mil)三種,但經過一系列表面處理后,外層銅箔的最終厚度一般會增加將近1OZ左右。內層銅箔即為芯板兩面的包銅,其最終厚度與...

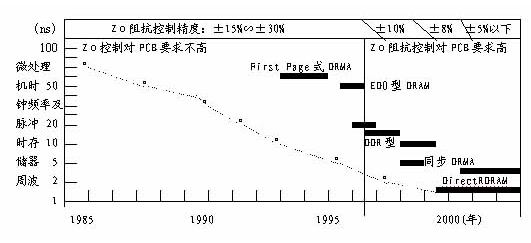

最初對PCB確立±10%的控制精度要求是由電路中800MHz頻率信號的Direc Rambus 型的DRAM模塊(RIMM)應用所提出的,這是為了保證計算機主機和交換機的內部電路實現更高速的動作。不僅搭載RIMM的計算機產品,而且很多的電子產品也需要基板上的電路能很好地與之匹配,一些客戶相應使用的P...

當系統工作在50MHz時,將產生傳輸線效應和信號的完整性問題;而當系統時鐘達到120MHz時,除非使用高速電路設計知識,否則基于傳統方法設計的PCB將無法工作。因此,高速電路設計技術已經成為電子系統設計師必須采取的設計手段。只有通過使用高速電路設計師的設計技術,才能實現設計過程的可控性。...

在現代接地概念中、對于線路工程師來說,該術語的含義通常是‘線路電壓的參考點’;對于系統設計師來說,它常常是機柜或機架;對電氣工程師來說,它是綠色安全地線或接到大地的意思。一個比較通用的定義是“接地是電流返回其源的低阻抗通道”。注意要求是”低阻抗”和“通路”。...

什么是地線?大家在教科書上學的地線定義是:地線是作為電路電位基準點的等電位體。這個定義是不符合實際情況的。實際地線上的電位并不是恒定的。如果用儀表測量一下地線上各點之間的電位,會發現地線上各點的電位可能相差很大。正是這些電位差才造成了電路工作的異常。電路是一個等電位體的定義僅是人們對地線電位的期望。...

RF工程設計方法必須能夠處理在較高頻段處通常會產生的較強電磁場效應。這些電磁場能在相鄰信號線或PCB線上感生信號,導致令討厭的串擾(干擾及總噪聲),并且會損害系統性能。回損主要是由阻抗失配造成,對信號產生的影響如加性噪聲和干擾產生的影響一樣。...

在protel99中添加庫的方法:在自己的ddb文件中(當前的項目文件或者另外專門為放這個庫而建一個)導入(import)你要添加的。lib文件,然后在原理圖編輯環境的 “browse liberary”框的“add/move”對話框中加入剛才已經加入的那個。ddb文件,選ok后你就可以找到添加進去...

總的來說,設計好一個高質量的高速PCB板,應該從信號完整性(SI---Signal Integrity)和電源完整性(PI---Power Integrity )兩個方面來考慮。盡管比較直接的結果是從信號完整性上表現出來的,但究其成因,我們絕不能忽略了電源完整性的設計。因為電源完整性直接影響最終PC...

信號質量可能受多方面的影響:信號通道中出現噪聲或其他雜亂信號、信號通道布線差、外部源的傳導或輻射、系統本身產生的噪聲。上述所有因素結合在一起會導致接收眼圖縮小。除電路板級問題外,信號完整性亦可能受到連接的源(傳輸端)及目的地(接收端)的影響。因此,應在整體系統級的信號完整性中考慮源及目的地的IC特點...

1).在通常條件下,所有的元件均應布置在印制電路的同一面上,只有在頂層元件過密時,才能將一些高度有限并且發熱量小的器件,如貼片電阻、貼片電容、貼IC等放在底層。 2).在保證電氣性能的前提下,元件應放置在柵格上且相互平行或垂直排列,以求整齊、美觀,一般情況下不允許元件重疊;元件排列要緊湊,輸入...

首先,要考慮PCB尺寸大小。PCB尺寸過大時,印制線條長,阻抗增加,抗噪聲能力下降,成本也增加;過小,則散熱不好,且鄰近線條易受干擾。在確定PCB尺寸后,再確定特殊元件的位置。最后,根據電路的功能單元,對電路的全部元器件進行布局。...

抑制干擾源就是盡可能的減小干擾源的du/dt,di/dt。這是抗干擾設計中最優先考慮和最重要的原則,常常會起到事半功倍的效果。減小干擾源的du/dt主要是通過在干擾源兩端并聯電容來實現。減小干擾源的 di/dt則是在干擾源回路串聯電感或電阻以及增加續流二極管來實現。...

EDA技術已經研發出一整套高速PCB和電路板級系統的設計分析工具和方法學,這些技術涵蓋高速電路設計分析的方方面面:靜態時序分析、信號完整性分析、EMI/EMC設計、地彈反射分析、功率分析以及高速布線器。同時還包括信號完整性驗證和Sign-Off,設計空間探測、互聯規劃、電氣規則約束的互聯綜合,以及專...

理想情況下的電源是沒有阻抗的,因此其不存在噪聲。但是,實際情況下的電源是具有一定阻抗的,并且阻抗是分布在整個電源上的,因此,噪聲也會疊加在電源上。所以應該盡可能減小電源的阻抗,最好有專門的電源層和接地層。在高頻電路設計中,電源以層的形式設計一般比以總線的形式設計要好,這樣回路總可以沿著阻抗最小的路徑...