高速度與低功耗一直是電路設計者永不停止追求的目標。在過去幾十年的時間里,人們一直通過器件特征尺寸的縮小實現電路性能的改善以及功耗的降低。但隨著尺寸向超深亞微米、納米尺度靠近,量子效應逐漸顯現并占據主導地位,一些諸如金屬互連、電流隧穿以及功耗等問題日益突出,將極大阻礙其向前發展的進程。

共振隧穿二極管(RTD)是一種基于電子共振隧穿通過雙勢壘結構的量子傳輸器件,屬于納米電子范疇。作為率先實用化以及當前發展最為成熟的納米電子器件,RTD基電路與傳統電路相比最主要的優點包括:一是它所具有的、多重穩態特性可以用來制作出十分緊湊的電路,具有簡化電路的功能;二是它的本征速度可進入吉赫范疇,實際器件開關時間達到1.5ps;三是在低功耗電路,尤其是存儲器應用方面與GaAs和CMOS技術相比都具有較明顯的優勢。

另外利用MOBILE電路所特有的自鎖存特性,并在其基礎上發展形成的新功能邏輯有力地推動了RTD基集成電路的發展,使其在數字電路、混合電路以及光電集成電路等方面應用上占據著越來越重要的地位。

1 RTD單片集成工藝

由于RTD屬于兩端器件,不能實現電流的調制,因此在形成電路時需要與三端器件相結合。下面就比較典型的RTD與III2V族化合物半導體器件高電子遷移率晶體管(HEMT),異質結雙極晶體管(HBT)與硅互補金屬氧化物半導體(CMOS)器件的工藝集成進行分別介紹。1.1 RTD與HEMT的集成在實際電路應用中與RTD集成最多的器件就是HEMT,其所形成的電路不僅保持了高頻率、低噪聲和低功耗的特點,而且大大簡化了電路結構,減小了芯片面積。RTD器件主要制作在HEMT的源區或漏區,這樣易形成串聯或并聯的形式,可以簡化工藝,提高集成度。材料結構是在半絕緣的GaAs或InP襯底上,采用分子束外延(MBE)的方法依次生長HEMT層結構,中間阻擋層和RTD結構,這樣排列的主要目的是為防止HEMT結構下出現摻雜層而影響器件的高頻性能。工藝流程可簡單的歸納為:RTD臺面的形成-器件隔離-HEMT源漏電極的形成-柵槽的腐蝕及柵電極制作-電極互連等步驟。

引入中間阻擋層的目的有兩個:一是起到阻擋停止的作用,這同時要求腐蝕液對兩種材料具有高的腐蝕選擇比。二是可以起到提高表面均勻性的目的,后者對HEMT器件的一致性以及大規模電路的集成起著更為重要的作用。除此集成技術之外,C.L.Chen等人[2]提出了RTD與HEMT的平面集成技術。它引入離子注入技術與自對準技術取代傳統的深臺面腐蝕技術,從而實現RTD與HEMT的平面集成。這種方法的主要優點是均勻性得到提高,適合大批量的生產。同時由于兩個器件位于同一平面,易于后道金屬互連工藝的實現。主要的缺點是額外的注入工藝使得復雜程度增加,增加了成本,而且芯片面積也較前者有所增加。

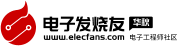

圖1(a)是一個以InP為襯底的RTD2HEMT結構示意圖[3]。RTD與HEMT相串聯形成一個三端的器件單元,通過HEMT柵極輸入電平的高低來調節整個單元電流的大小,其最大值僅由RTD的峰值電流決定,而與柵壓無關。具體工作原理是當HEMT的源漏電流小于RTD的峰值電流時,電路不滿足發生共振隧穿的條件,源漏電流表現為HEMT的飽和輸出特性曲線。而隨著柵壓的增加當源漏電流大于RTD峰值電流時,共振隧穿發生,輸出電流表現為具有負阻特性的RTD曲線。此時如進一步增加柵壓,RTD將扮演了一個電流限制器件的作用,輸出的峰值電流并不發生改變,如圖1(b)所示。

圖1 RTD2HDMT結構圖及輸出I2V曲線

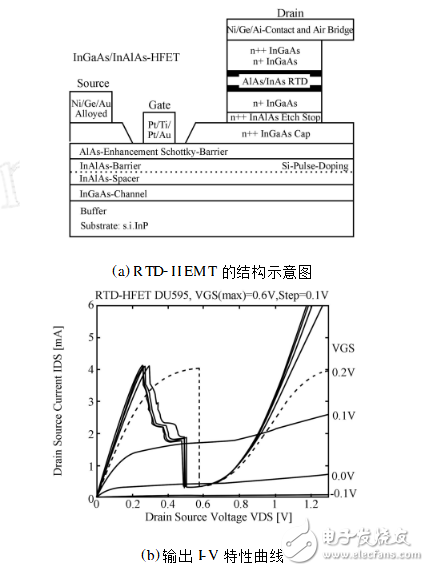

圖2是Raytheon公司在3inInP襯底上制作的集成500個RTD的大規模高速混合信號電路,它很好地將RTD器件的不一致性控制在3%以內。電路采用0.25μm的RTD2HEMT技術,采用三層金屬互連工藝,共十塊掩模板制作出了RTD,HEMT,肖特基二極管,電阻以及電容等元件,實現包括十階2.5GHz的移位寄存器,6.5GHz的時鐘發生器,多值到二進制的轉換器等多種功能邏輯。圖2(b)所示空氣橋的引入既起到互連電極的基本作用,又可以降低RTD的寄生電容,消除邊緣效應,獲得良好的高頻特性,適用于超高速電路的制作

圖2 RTD與HEMT集成電路的掃描電鏡俯視圖及剖面圖

1.2 RTD與HBT集成

與HEMT不同,HBT屬于受電流調控的增強型器件。RTD與HBT的集成[526],相對普通HBT工藝,增加了兩步:一是RTD臺面的刻蝕。RTD以外的區域先刻蝕到InP阻擋層,然后刻蝕到HBT發射極帽層,從這點開始,進行HBT工藝,HBT發射極金屬同時作為HBT發射極接觸和RTD頂部接觸。發射極和RTD頂部接觸被刻蝕,沉積HBT基極金屬,基極金屬同時接觸HBT基極層和RTD底層。二是最后器件的平面化和互連。在HBT集成電路工藝中,聚酰亞胺涂覆于晶片,刻蝕出發射極金屬。在RTD與HBT集成工藝中,由于器件的頂部接觸是非平面的,開發了兩步的聚酰亞胺反刻工藝。第一次反刻止于HBT發射極金屬暴露之前,這時只暴露出RTD的頂部接觸。第一次平面化刻蝕以后,RTD臺面由光刻膠掩蔽,用O2/Ar等離子體繼續反刻,直至暴露出HBT發射極接觸。二次反刻以后,RTD與HBT頂部接觸被清除干凈,以便與第二層金屬接觸。

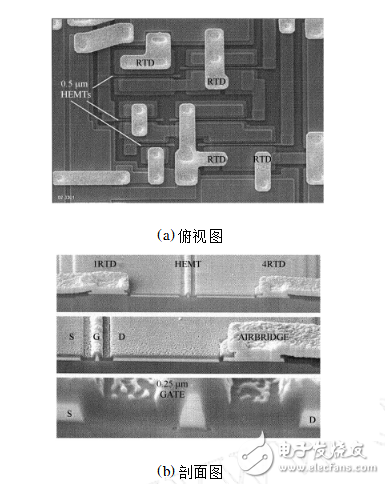

圖3(a)是采用TCAD模擬的RTD與HBT互連的剖面圖,采用第二層金屬將HBT的收集區與RTD的下電極相連。圖3(b)是已實現的RTD2HBT集成電路圖片,該電路包含有六個不同面積的RTD,HBT發射區面積為2×10μm2,另外該電路還集成了薄膜電阻,電容以及螺旋電感等多種元件。

目前已實現的RTD2HBT電路包括反相器,邏輯門,全加器,多值計數器,多路復用器等。

圖 3RTD與HBT互連示意圖及IC圖片

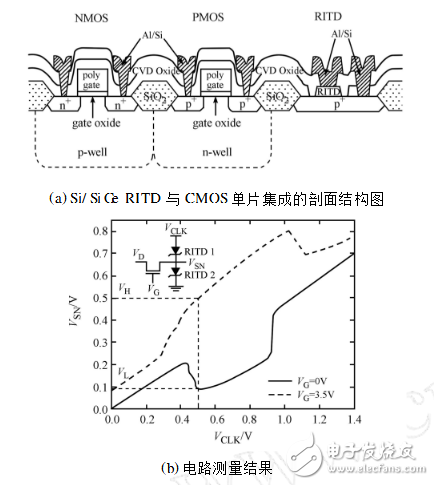

1.3 RTD與CMOS集成

實現納米電子器件RTD與當前工業主流CMOS工藝的集成一直是人們追求的目標。早期由于RTD主要制作在III2V族化合物的襯底上,Bergman等人[7]提出了在III-V族化合物(GaAs或InP)的襯底上制備RTD,在硅襯底上制備CMOS器件電路,然后通過金屬鍵合將二者結合起來的方法。但這種方法不適應大規模電路的集成,額外的鍵合工藝增加了成本,引入的寄生參量同時降低了電路的性能。隨著材料生長技術的發展,特別是1998年Rommel[8]采用低溫分子束外延(LT-MBE)的方法制作出第一個在室溫下工作的硅基RTD以來,大量研究工作的展開使器件性能得到了極大的改善。目前已報道的Si/SiGe共振帶間隧穿二極管(RITD)最高峰谷電流比(PVCR)值達到6.0[9],峰值電流密度最高可達151kA/cm2[10],滿足超高速數字集成電路的應用要求,而且峰值電流密度還可根據隔離層厚度的不同進行選擇。最近已實現Si/SiGeRITD與CMOS的集成[11],如圖4所示。電路采用兩個RTD管串聯形成一個鎖存器,通過一個NMOS管注入電流,實現整個單元單-雙穩態邏輯轉換的功能。該邏輯門在0.5V偏壓下的電壓擺幅為84%,整個邏輯單元可保證實現高密度嵌入式存儲器電路在較低電壓下運行。

圖4 Si/SiGeRITD與CMOS剖面結構圖及測量結果

? ? ? ? ? ? ? ?

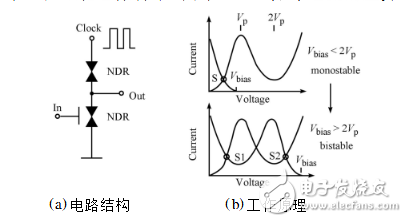

2 RTD基電路

RTD基電路大部分都是基于MOBILE[12]的,或在其基礎上進行改進的。MOBILE即單-雙穩態邏輯單元,該電路具有邊沿觸發和自鎖存兩大功能。MOBILE的基本結構是一對串聯的RTD構成,一個FET管與驅動RTD管并聯作為輸入,如圖5(a)所示。工作原理是利用RTD的負阻特性,驅動電路產生單穩-雙穩態轉變。當輸入時鐘為低電平時,負載線只有一個交點,呈現單穩態。當時鐘為高電平時(大于兩倍的RTD峰值電壓VP),負載線有兩個交點,呈現出雙穩態的特性,如圖5(b)所示。在雙穩態條件下,兩個RTD管峰電流的差異

圖5 MOBILE電路結構及工作原理

決定電路的輸出狀態,即MOBILE邏輯單元是電流調制工作。MOBILE電路的提出,對RTD基數字集成電路的發展起到了極大的推動作用。

利用1.1所述的RTD-HEMT串聯結構的輸出特性,實現的改進MOBILE反相器如圖6(a)所示。這里可以將MOBILE理解為一個受電流控制的邏輯電路與一個上升沿觸發的鎖存器的結合。當時鐘電壓VCLK小于電路轉換電壓VSW時,輸出為單穩態;當VCLK與VSW相等時,為亞穩態;當VCLK大于VSW時,為雙穩態。通過比較流過T1,D1管的電流和與D2電流的大小決定輸出電平狀態:當前者小于后者時,D1管截至呈高阻態,輸出高電平,反之輸出低電平。線性閾值門(LTG)作為MOBILE的改進及延伸,可以實現任意的線性布爾運算,增強了并行處理的能力,其電路圖如圖6(b)所示。LTG是一個多輸入的門電路,通過計算n個輸入xi的權代數和與閾值θ相比較確定輸出電平y的值。權xi的絕對值僅由RTD的面積決定,當管子位于圖6(b)所示的上拉網絡時,權值為正,反之取負值。

圖6 RTD2HEMT的單2雙穩態轉換及線性閾值邏輯門電路輸出電平y用公式表示為:

y=sign(∑n1wixi-θ)=sign(x1+x2-x3-x4-θ)(1)

當x1+x2Εx3-+x4+θ時,y=1,反之y=0。其中,xi根據輸入的高低電平取1或0。LTG提供了一個并行計算的方案,可起到減少器件數和電路邏輯深度的作用。以此為基本單元的電路可有效地實現復雜的邏輯功能。在此基礎上建立的電路邏輯功能不易受輸入電壓波動的影響,因此具有魯棒性好,抗噪聲能力強的優點,適用于超大規模的RTD基電路的集成與制作。

RTD基的集成電路在全加器、時鐘量化器、分頻器、移位寄存器、延遲觸發器、可編程邏輯門等許多方面都得到實現。RTD基電路的設計根據不同的應用,對器件的性能參數會有不同的要求。例如無論是作存儲還是作邏輯電路用,為了獲得足夠的噪聲容限都要求RTD具有很高的峰谷電流比(PVCR)值。而就高速邏輯的應用而言,由于峰值電流密度決定RTD的充電時間,則更希望RTD具有較高的峰值電流。做低功耗存儲器應用時,則要求RTD具有較低的電流密度。下面就兩類最典型的電路:超高速(以ADC/DAC為例)電路和低功耗(TSRAM為代表)進行分析與討論。

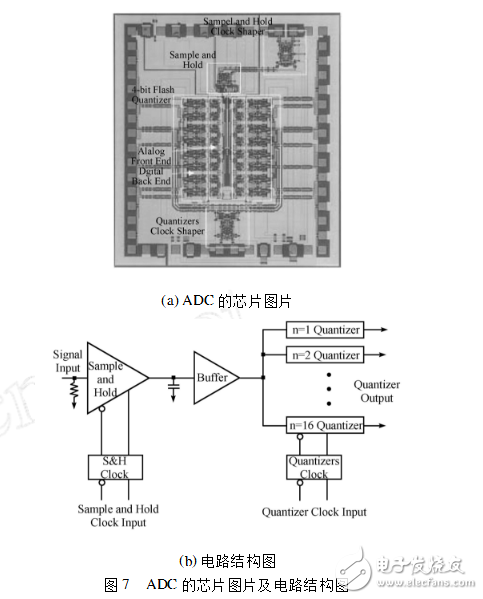

2.1 ADC/DAC電路

超高速的模數/數模轉換器(ADC/DAC)在當前的大規模集成電路中占有重要的地位。超過1Gbitps轉換率的ADC可實現不需要選擇模擬通訊波道的數字接收機。對于X波段來說,要求ADC的采樣率達到20Gbitps。傳統的比較器一般使用再生反饋來實現在一個單時鐘循環的有效數字輸出。高速度和高敏感度必須通過緊湊的電路版圖以及使用高速的晶體管來完成。Broekaert[13]等人采用單片集成RTD-HEMT的技術,實現了4比特2Gbitps的閃存共振隧穿模數轉換器(FlashADC)電路。與傳統晶體管電路相比,減少了元件數量,降低了功耗,提高了工作速度。整個芯片面積為1.9×2.1mm2,由64個RTD,225個HEMT,以及肖特基二極管,電阻和電容等總計450余個元件構成。ADC由一個采樣保持電路,緩沖器,16個時鐘比較器以及兩個片上時鐘產生器構成。16個量化器的閾值由RTD的面積決定。整個ADC的芯片如圖7(a)所示,電路結構圖如圖7(b)所示。

ADC電路中的核心部分-時鐘比較器的電路圖8所示,它由13個HEMT,4個RTD以及9個肖特基二極管組成。四個RTD都屬于模擬地(AGND)的部分,與數字地(GND)相分離。輸入的HEMT和RTD轉變輸入電壓為電流,大小與負載RTD管(RTD-L)的電流相當。源端RTD(RTD-S)從不導通,起到一個與RTD-L相匹配的電阻的作用。RTD的非線性使比較器實現自鎖存的功能,避免了電路再生反饋的需要。因此,RTD基的比較器非常適用于高速的運行。

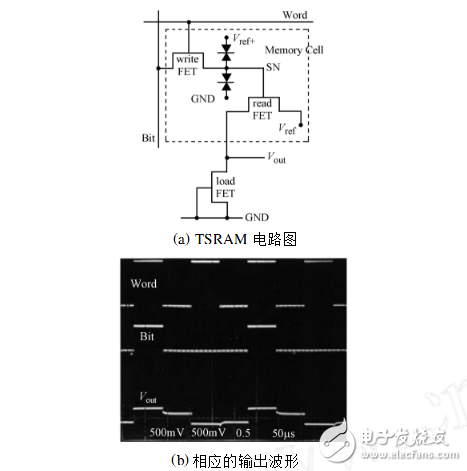

2.2 TSRAM電路

在RTD基低功耗電路的應用中,存儲器占據著重要的地位。HEMT由于在低的漏電流下的截至頻率很高,因此在存貯器中具有高速低功耗尋址的優勢。低功耗的化合物半導體存儲器可以實現高速的數據處理功能。在InP的襯底上制備的僅采用兩個HEMT管以及兩個RTD管,50nW的待機功耗的隧穿靜態隨機存儲器[14215]如圖9所示。它采用一對峰值電流密度小于1A/cm2,與晶體管的漏電流相當的低電流密度RTD管。如圖9(a)所示電路,Vref為1.0V,Vref+在兩態時取0.45V。由兩個RTD以鎖存器的形式在存儲節點SN處形成兩個穩定的電壓值,并與讀HEMT(readFET)的柵極相連使之驅動位線(Bitline)同時不影響SN處的電荷。當字電壓為低電平時,根據兩個FET柵漏電流的大小決定節點SN電平的高低。當RTD鎖存電壓Vref+取0.45V時,當字線(Wordline)為低電平時,SN根據以前寫入位線的電平鎖存于上述兩個穩定的電壓水平之一。在0.45V的偏壓下,兩個穩定的電平值近似為0.08V和0.36V,如圖9(b)所示。在此偏壓下存儲器單元的待命功耗少于50nW,比傳統GaAs靜態存儲器相比,靜態功耗降低了近兩百倍。還可通過增加集成的RTD數量可實現100nW的三態存儲器單元。另外,隨著硅基RTD的發展,通過與成熟的CMOS電路相結合,可應用實現硅基RTD低功耗存儲器。

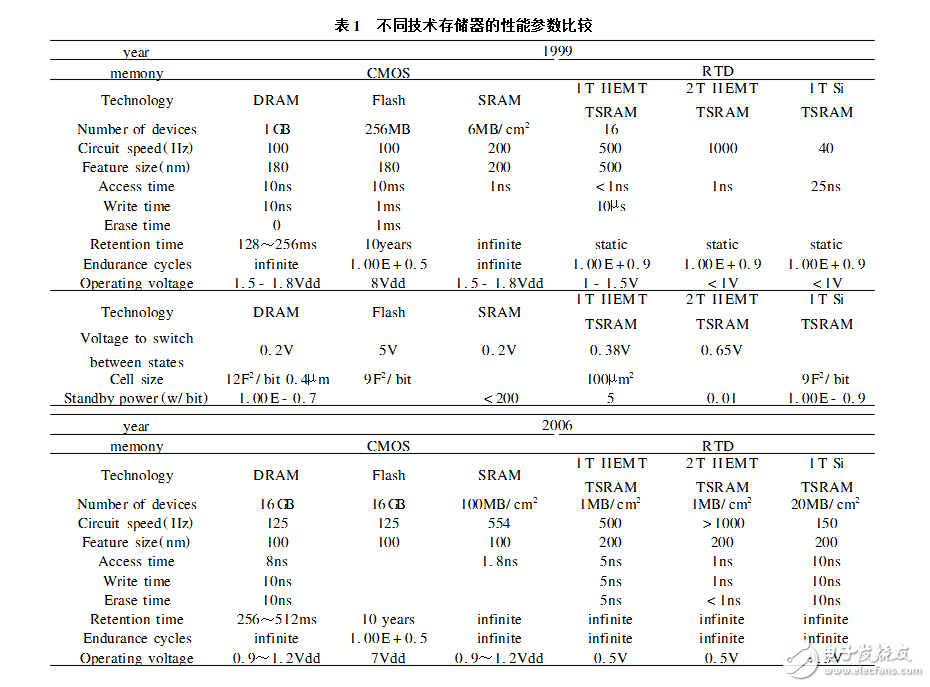

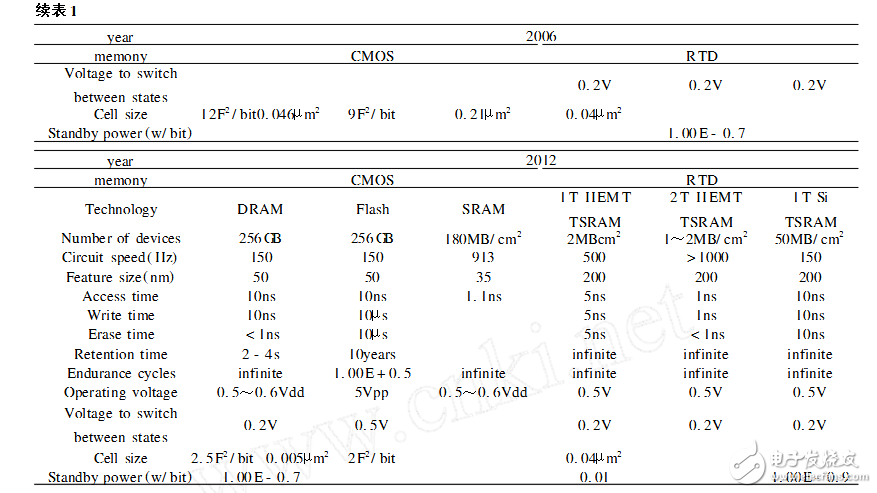

表1是不同技術存儲器在1998年的性能與2006年、2012年的預測性能比較。可以看出RTD基存儲器無論在電路速度,訪問/寫入/擦除時間,還是在功耗、壽命等方面,與CMOS存儲器相比都具有明顯的優勢,而且技術發展對特征尺寸的要求也不如CMOS那樣苛刻。

3 面臨的難點及挑戰

RTD基電路雖然具備上述的眾多優點,而且器件性能在重復性,線性,一致性,可靠性等各方面已經得到了長足的改進,但仍存在著一些不成熟、不完善的地方沒有解決,因此阻礙了其電路大規模批量化的生產。RTD基電路產業化所面臨的主要挑戰還是由于RTD器件隧穿電流隨勢壘厚度呈指數規律變化,因此器件特性對勢阱和勢壘厚度的變化極度敏感。在目前階段整個片上的勢壘、勢阱厚度的漲落仍然比較大,尚無法實現很大規模的集成。

它的另一問題是與采用的材料體系有關。對于III-V族化合物而言,由于具有較低的肖特基勢壘,HEMT不易制作成增強型器件。而對HBT來說,雖然為增強型,但由于其具有很大的跨導,不易調節控制降在RTD兩端的電壓。刻蝕工藝方面,由于干法刻蝕所用的氣體對化合物半導體材料的選擇比都不是很高,因此主要還是依靠濕法腐蝕,這樣不利于器件尺寸精度的提高與芯片均勻性的改善。采用SiO2/Si/SiO2結構的RTD無疑是人們所期待的,由于與CMOS工藝完全兼容,可以很容易地與CMOS電路集成在一起。而且由于它的對稱性結構,增加了電路設計的自由度。但是,要求在兩層SiO2勢壘中生長出一層厚度可精確控制的單晶硅層增大了工藝技術上的難度,造成目前已實現的器件性能還不是很高,發展速度也較Si/SiGeRITD緩慢,需要某些關鍵技術上的突破。

在目前比較關注的Si/SiGeRITD與CMOS集成的問題上,RITD放置的最好位置是在MOS管的源、漏電極上,這樣做具有便于集成等優點[16]。考慮到溫度對器件的影響,RITD結構的生長順序選擇在CMOS前線工藝退火后,后線金屬工藝前完成。但由于外延層晶格質量的退化以及離子注入工藝殘留下的損傷,相同結構的RITD在p+硅襯底和p+離子注入區,在周圍有、無其他圖形的情況下展現出不同的PVCR值與峰值電流密度,這樣降低了設計的自由度。同時,溫濕度對RTD性能的影響與電路中其他集成器件的兼容性問題,尤其在惡劣的空間環境工作時,也是需要考慮和改進的方面。

4 總 結

RTD器件高速度,低功耗,簡化電路的特性已為人們所熟知。在RTD基集成電路的應用方面,RTD與III-V族半導體器件(HEMT,HBT)無論從材料生長,工藝制作,還是電路實現等各方面都比較成熟。形成的電路不僅保持了原始電路高頻率、低噪聲和低功耗的特點,而且通過簡化電路結構,減小了芯片面積,提高了集成度。隨著硅基RTD的問世及發展,與CMOS電路的集成逐漸成為研究的熱點,首個基于Si/SiGeRITD與CMOS的集成電路亦已實現。在電路設計上,MOBILE以其所特有的雙穩態以及自鎖存的特性,成為RTD基集成電路的發展基礎。

在實際電路的應用上,高速的ADC/DAC以及低功耗的存儲器電路成為其最主要的應用方向。這方面的研究成果最終可應用于高速微電子、光電集成模塊和系統之中,以解決大于40Gbit/s高比特率光電轉換的瓶頸。

在商業和軍事應用等方面都具有著重要的作用。在推向產業化的進程中RTD基電路也面臨著包括材料、工藝集成等諸多方面的問題與挑戰,一定程度上影響了其大規模集成化的進程,需要在材料工藝以及新技術方面的改進與突破加以解決。通過討論分析,提出基于硅基RTD與線性閾值門(LTG)邏輯相結合是未來納米級超大規模集成電路的最佳發展方向。