AD9850概要

AD9850是AD公司生產的最高時鐘為125MHz、采用先進的CMOS技術的直接頻率合成器,主要由可編程DDS系統、高性能數模變換器(DAC)和高速比較器3部分構成,能實現全數字編程控制的頻率合成。

AD9850內部結構

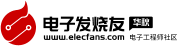

AD9850的芯片功能框圖如圖2所示。

AD9850芯片內包括高速DDS.10位DAC.頻率/相位數據寄存器。數據輸入寄存器。比較器等,在125MHz參考時鐘下,AD9850經過高速的DDS核心芯片能產生一個32位頻率調整控制字可使AD9850的輸出頻率達0.0291Hz;并能提供了5bits的相位控制位,它能使輸出相位以180°.90°.45°.22.5°.11.25°或是它們任意組合的增量改變.AD9850的電路結構允許產生頻率值是參考時鐘的一半的輸出,并且輸出的頻率能用數控方式以每秒產生23000000個新頻率的速度變化.AD9850芯片內的比較器構成能接收經外部低通濾波后的DAC轉換輸出,可以產生一個低抖動的方波輸出的裝置,因此AD9850用作時鐘發生器十分方便。頻率/相位數據寄存器。數據輸入寄存器在外部的頻率更新時鐘和字加載時鐘的控制下進行頻率控制字的輸入和更新,使芯片輸出所要求的頻率和相位.

AD9850的工作原理

AD9850內含可編程DDS系統和高速比較器,可實現全數字編程控制的頻率合成。

可編程DDS系統由相位累加器和正弦查表組成,其相位累加器由一個加法器和一個N位的相位寄存器組成,N一般為24~32;實質上是一個可變模的計數器,即DDS相位增量的個數在計數器收到每一個時鐘脈沖時被存儲起來,當計數器溢出時,它就回到初態并使用相位累加器輸出到相鄰值。頻率控制字能設置計數器的模,它決定了相位增量的大小。相位增量在每個時鐘到來時便在相位累加器中相加,相位增量越大,則累加器溢出的速度越快,產生的輸出頻率越高。

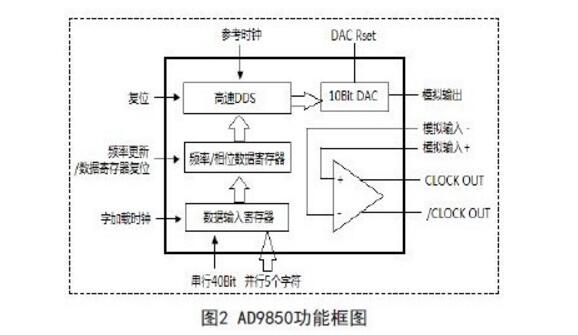

AD9850采用32位的相位累加器,AD9850利用改進的,獨有的算法,把14bits已截斷的相位累加器的輸出轉變成適當的余弦值,經片內高速的10bitDAC轉換器,可得到模擬正弦波。這個獨特的算法使用一個簡化了的ROM表和DSP技術等功能,有助于縮小AD9850的體積和功耗。輸入。輸出。參考時鐘和頻率控制字的關系如下:

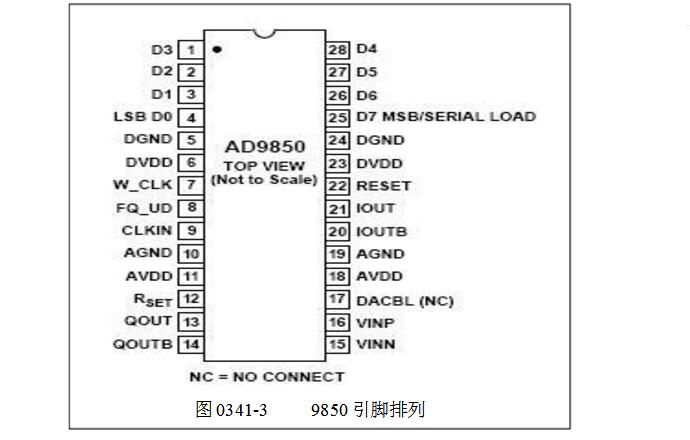

AD9850引腳及功能

AD9850的控制字與控制時序

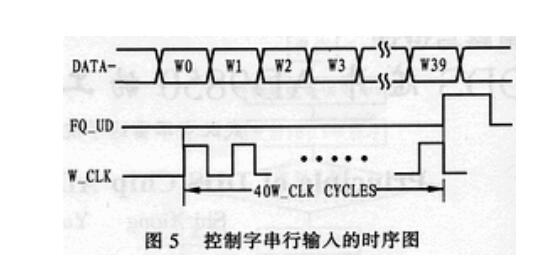

AD9850有40位控制字,32位用于頻率控制,5位用于相位控制。1位用于電源休眠(Powerdown)控制,2位用于選擇工作方式。這40位控制字可通過并行方式或串行方式輸入到AD9850,圖4是控制字并行輸入的控制時序圖,在并行裝入方式中,通過8位總線A0…D7將可數據輸入到寄存器,在重復5次之后再在FQ-UD上升沿把40位數據從輸入寄存器裝入到頻率/相位數據寄存器(更新DDS輸出頻率和相位),同時把地址指針復位到第一個輸入寄存器。接著在W-CLK的上升沿裝入8位數據,并把指針指向下一個輸入寄存器,連續5個W-CLK上升沿后,W-CLK的邊沿就不再起作用,直到復位信號或FQ-UD上升沿把地址指針復位到第一個寄存器。在串行輸入方式,W-CLK上升沿把25引腳的一位數據串行移入,當移動40位后,用一個FQ-UD脈沖即可更新輸出頻率和相位。圖5是相應的控制字串行輸入的控制時序圖。

AD9850的復位(RESET)信號為高電平有效,且脈沖寬度不小于5個參考時鐘周期。AD9850的參考時鐘頻率一般遠高于單片機的時鐘頻率,因此AD9850的復位(RESET)端可與單片機的復位端直接相連。

值得一提的是:用于選擇工作方式的兩個控制位,無論并行還是串行最好都寫成00,并行時的10、01和串行時的10、01、11都是工廠測試用的保留控制字,不慎使用可能導致難以預料的后果。

ad9850應用電路一

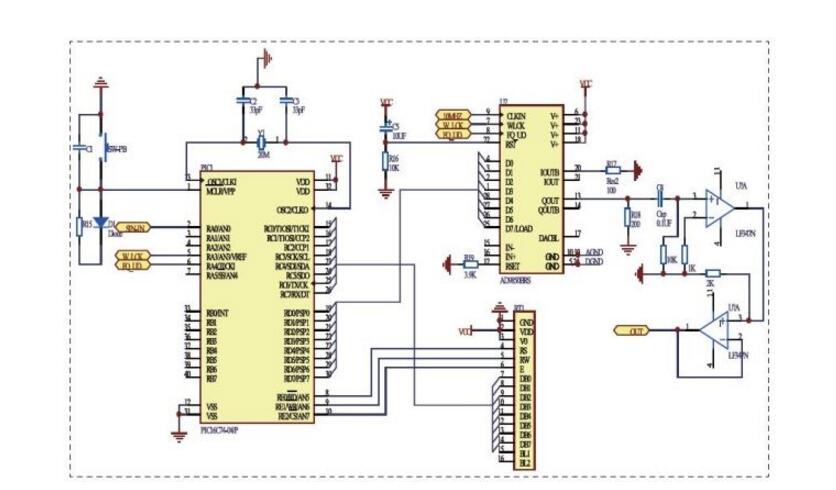

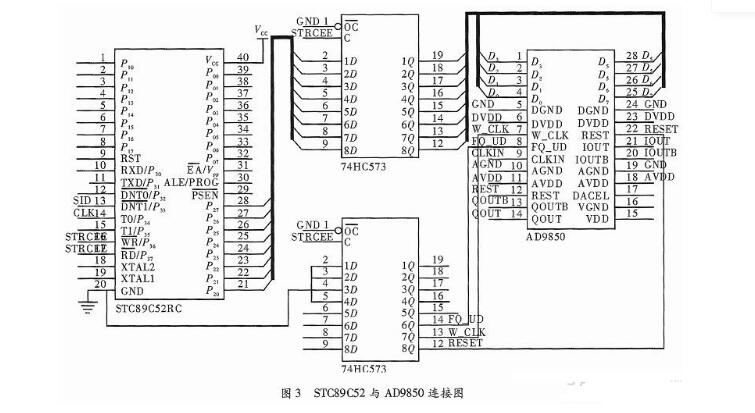

AD9850的40位頻率/相位控制字可通過并行或串行兩種方式送入器件。選用并行傳輸方式,充分發揮芯片AD9850的高速性能。在并行方式下連續輸入 5次數據,每次輸入8位(1 Byte),將40位頻率/相位控制字送入器件。系統中,單片機通過數據鎖存器和控制鎖存器來實現對AD9850模塊的控制,數據鎖存器打開時,控制鎖存器關閉,此時傳輸數據;控制鎖存器打開時,數據鎖存器關閉,此時根據AD9850的時序對W_CLK、FQ_UD、RESET執行相應的操作。單片機 89C52控制AD9850工作連線圖,如圖3所示。

ad9850應用電路二

總線方式并行接口占用的單片機資源較少,而且本設計中信號發生器只是作為單片機控制模塊的外圍擴展模塊之一,因此AD9850工作在控制字并行輸入方式。此時,AD9850僅作為一擴展芯片只占用一個地址。其原理圖如圖4所示。

ad9850應用電路三

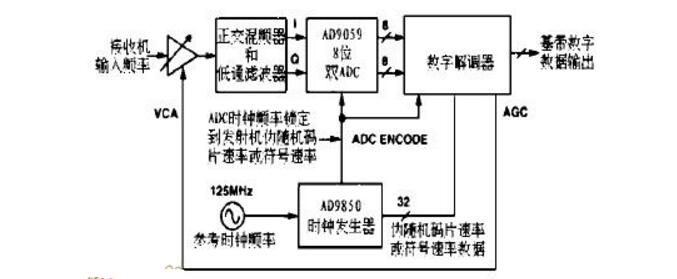

AD9850 時鐘發生器在擴頻接收器中的應用

ad9850應用電路四

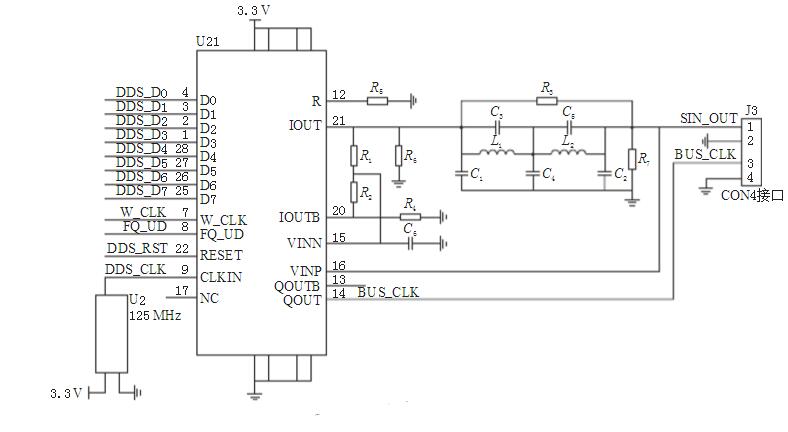

AD9850是美國AD公司生產的高集成度的DDS合成芯片。它采用32位相位累加器,截斷成14位,輸入正弦查詢表,查詢表輸出截斷成10位,輸入到DAC。DAC輸出兩個互補的模擬電流,接到濾波器上。但是AD9850直接產生的信號幅度只有2V左右,而且是單極性的。而測試的時候需要的是雙極性的正弦信號,因此DDS輸出的信號還要經過隔直和放大。AD9850輸出的信號經過RC高通濾波器,將直流分量濾除,輸出交流信號,再經放大器放大,電壓跟隨,輸出幅度適當、帶載能力較強的信號源。電路如圖所示。