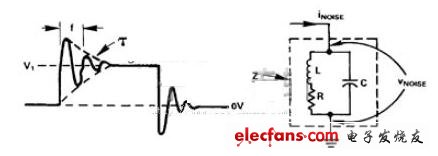

● 恒定電阻R與線路串聯。電壓變化V1是R與電流階躍I1的

乘積。

●振蕩自然頻率f1取決于串聯的L和并入的C,f = 1/(2πLC)。

●阻尼時間常數T由L/R決定。

?

圖5. 欠阻尼R-L-C電路的波形。

容性耦合噪聲

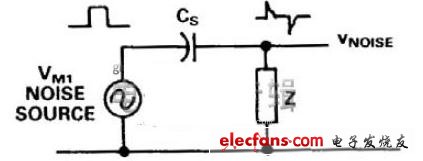

噪聲源至另一電路的容性耦合也會產生噪聲。此類噪聲常見于具有快速升降時間或高頻成分的信號靠近高阻抗電路的情況。雜散電容將信號快速沿耦合至相鄰電路,如圖6的電路模型所示。阻抗Z的性質決定響應波形。表1列出了典型電容。

?

圖6. 雜散電容將噪聲耦合至高阻抗電路。

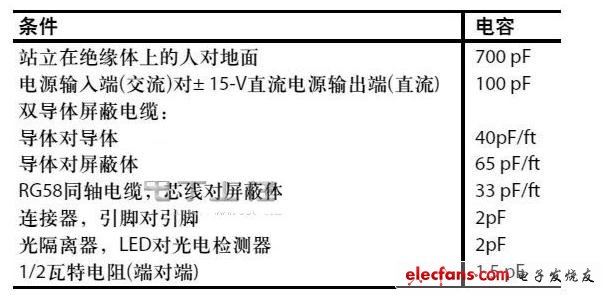

表1. 典型電容。

?

容性拾取發生的方式、形狀和大小有多種。下面是幾個示例:

●TTL數字信號產生快速沿,典型上升時間為10納秒,電壓擺幅為5 V。如果Z是1兆歐電阻,即使0.1pF也會產生5 V尖峰和100納秒的衰減時間常數。

●兩根相鄰導線間可能產生串擾。例如,如果兩根導線是10英尺(3米)長度的電纜,電容為40 pF/英尺,則總電容為400 pF。如果在一個導體上施加1 kHz的10 V測試電壓,當Z是10 k電阻時,1 kHz的250 mV電壓將耦合至相鄰導線。

●通過公共阻抗在交流電力線上產生的噪聲將耦合至其他電路。常見情況是瞬變通過電源變壓器的繞組間電容耦合。

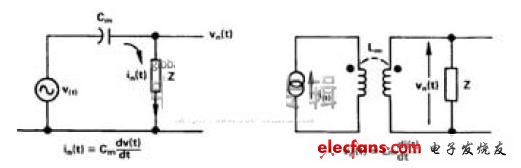

令人驚奇的是,小小的電容竟能導致嚴重問題。例如,考慮高抗擾度CMOS邏輯用于工業電路中的情況,電路中存在2500 V、1.5 MHz噪聲瞬變(IEEE標準472-1974)。假設CMOS輸入與噪聲源之間僅有0.1 pF的雜散電容,如圖7所示。計算出的噪聲電壓為2.4 V,穩態下,50 V的初始瞬變將導致邏輯運算錯誤,甚至更壞的情況!

?

圖7. 高壓瞬變從測試發生器耦合至邏輯。

磁耦合噪聲

電纜載送電流、分配交流電源時,以及機器、電源變壓器、風扇等附近均可發現強磁場。磁耦合電路與容性耦合電路間存在類似的關系,如圖8和表2所示。

● 噪聲為磁耦合時,電壓噪聲(Vn)表現為與接收機電路串聯;而在容性情況下,接收機與地電壓間產生的電壓噪聲是噪聲電流in在Z中造成的電壓。

●降低接收機阻抗Z可減少容性耦合噪聲。磁耦合電路則不同;降低Z不會顯著減少電壓噪聲。

?

圖8. 磁噪聲耦合與容性噪聲耦合的比較。

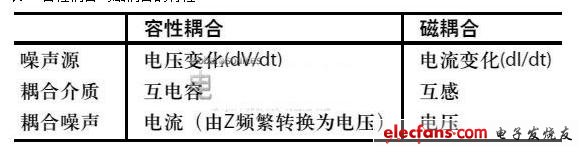

表2. 容性耦合與磁耦合的特性。

?

此類比可幫助我們考量容性耦合噪聲與磁耦合噪聲間的差異。

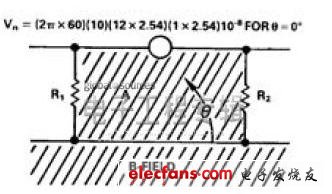

磁場在閉合環路(單匝)內的感應電壓Vn由下式給出:

Vn = 2πfBA cosθ×10-8 (1)

單位為伏特,其中f是正弦變化通量密度的頻率,B是通量密度的均方根值(高斯),A是閉合環路面積(cm2),θ是B與面積A的角度。

例如,考慮圖9所示電路。它顯示的是兩個一英尺導體的電壓計算,導體相隔1英寸,置于10高斯60 Hz磁場內(對于風扇、電源布線、變壓器很典型)導線內最大感應電壓為3 mV。

?

上面公式說明,噪聲電壓可通過降低B、A或cosθ來減少。要降低B項,可增加與磁場源的距離,在磁場由流經導線對附近的電流引起的情況下,也可絞繞導線,通過交替方向將凈磁場降至零。

電子發燒友App

電子發燒友App

評論