本文采用一種基于比例積分(PI)控制算法的環(huán)路濾波器應(yīng)用于帶寬自適應(yīng)的全數(shù)字鎖相環(huán),建立了該鎖相環(huán)的數(shù)學模型

2010-10-14 10:03:25 1271

1271

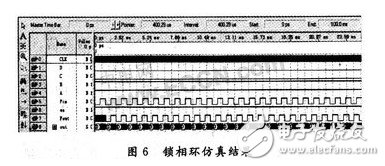

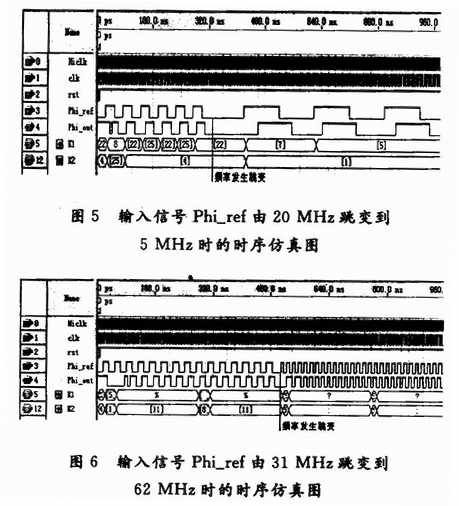

本文在說明全數(shù)字鎖相環(huán)的基礎(chǔ)上,提出了一種利用FPGA設(shè)計一階全數(shù)字鎖相環(huán)的方法,并給出了關(guān)鍵部件的RTL可綜合代碼,并結(jié)合本設(shè)計的一些仿真波形詳細描述了數(shù)字鎖相環(huán)的工作過程,最后對一些有關(guān)

2018-10-25 09:17:13 8237

8237 介紹了鎖相環(huán)路的基本原理,分析了集成鎖相環(huán)芯片ADF4106的工作特性,給出了集成鎖相環(huán)芯片ADF4106的一個應(yīng)用實例,為高頻頻率合成器的設(shè)計提供了很好的思路。 關(guān)鍵詞:ADF4106,鎖相環(huán),頻率合成器,環(huán)路濾波器

2019-07-04 07:01:10

本文設(shè)計了一種寬頻率范圍的CMOS鎖相環(huán)(PLL)電路,通過提高電荷泵電路的電流鏡鏡像精度和增加開關(guān)噪聲抵消電路,有效地改善了傳統(tǒng)電路中由于電流失配、電荷共享、時鐘饋通等導(dǎo)致的相位偏差問題。設(shè)計了

2019-07-08 07:37:37

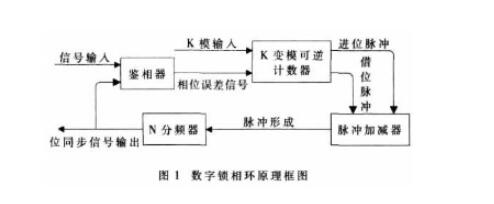

全數(shù)字鎖相環(huán)的設(shè)計及分析 1 引 言 鎖相環(huán)是一種能使輸出信號在頻率和相位上與輸入信號同步的電路,即系統(tǒng)進入鎖定狀態(tài)(或同步狀態(tài))后,震蕩器的輸出信號與系統(tǒng)輸入信號之間相差為零,或者保持為常數(shù)

2010-03-16 10:56:10

本帖最后由 gk320830 于 2015-3-9 20:38 編輯

最近在用adf 4001做一個鎖相環(huán),環(huán)路配置好后發(fā)現(xiàn)鎖定不了,電荷泵cp 輸出一直在掃描,檢查芯片內(nèi)部的配置,也沒發(fā)現(xiàn)什么問題,分頻輸出也是正常的,哪位高手用過這個芯片,幫我分析分析吧,期待中。。。

2010-09-14 08:52:16

本文按照數(shù)字鎖相環(huán)設(shè)計的步驟,采用手把手的方式講述設(shè)計過程和原理,旨在給數(shù)字鎖相環(huán)初次設(shè)計者提供一個思路,縮短開發(fā)的時間。 有關(guān)數(shù)字鎖相環(huán)的帖子不斷出現(xiàn),但大多沒有講述其原理。翻開有關(guān)鎖相環(huán)的書總是

2012-01-12 15:29:12

數(shù)字鎖相環(huán)設(shè)計源程序PLL是數(shù)字鎖相環(huán)設(shè)計源程序, 其中, Fi是輸入頻率(接收數(shù)據(jù)), Fo(Q5)是本地輸出頻率.目的是從輸入數(shù)據(jù)中提取時鐘信號(Q5), 其頻率與數(shù)據(jù)速率一致, 時鐘上升沿鎖定在數(shù)據(jù)的上升和下降沿上;頂層文件是PLL.GDF

2009-12-18 10:37:37

而已,設(shè)計出來的鎖相環(huán)肯定很精確。但是,在物理控制器中,還有一種很簡單的設(shè)計方法,也就是我們的項目曾經(jīng)使用的鎖相方法,直接采集A相電壓,然后判斷A相電壓的過零點,如果出現(xiàn)過零點,那么就記錄下該時刻

2015-01-04 22:57:15

電荷泵鎖相環(huán)的基本原理是什么?電荷泵鎖相環(huán)的噪聲模型與相位噪聲特性是什么?電荷泵鎖相環(huán)的相位噪聲與環(huán)路帶寬關(guān)系是什么?

2021-06-07 06:57:53

本帖最后由 zhihuizhou 于 2011-12-21 17:43 編輯

鎖相環(huán)PLL原理與應(yīng)用 第一部分:鎖相環(huán)基本原理 一、鎖相環(huán)基本組成 二、鑒相器(PD) 三

2011-12-21 17:35:00

鎖相環(huán)路是一種反饋控制電路,簡稱鎖相環(huán)(PLL,Phase-Locked Loop)。鎖相環(huán)的特點是:利用外部輸入的參考信號控制環(huán)路內(nèi)部振蕩信號的頻率和相位。因鎖相環(huán)可以實現(xiàn)輸出信號頻率對輸入信號

2022-01-11 06:34:28

如題,AD9957的鎖相環(huán)一直失鎖,不用鎖相環(huán)輸出點頻信號時正常的,用了鎖相環(huán)后,PLL_LOCK信號一直為低,sync_clk輸出信號也不是穩(wěn)定的周期信號,環(huán)路濾波器的值有點誤差,因為現(xiàn)有的器件沒有那么精確的電容電阻值,問下鎖相環(huán)的控制除了控制CFR3之外還有別的要注意的么?

2018-12-10 09:30:24

該文章是完全原創(chuàng),用最簡潔的語言講清楚FPGA實現(xiàn)負反饋的精要。震撼!FPGA實現(xiàn)負反饋控制純數(shù)字鎖相環(huán)!.zip (225.26 KB )

2019-04-30 04:50:41

LabVIEW鎖相環(huán)(PLL) 鎖相環(huán)是一種反饋電路,其作用是使得電路上的時鐘和某一外部時鐘的相位同步。PLL通過比較外部信號的相位和由壓控晶振(VCXO)的相位來實現(xiàn)同步的,在比較的過程中,鎖相環(huán)

2022-05-31 19:58:27

在使用K60的過程中發(fā)現(xiàn)自己pllinit()不清楚,才發(fā)覺自己鎖相環(huán)的概念還不懂,so,趕緊補補……鎖相環(huán)(PLL: Phase-locked loops)是一種利用反饋(Feedback)控制

2021-11-04 08:57:18

PLL(鎖相環(huán))電路原理是什么?

2022-01-21 07:03:37

`可編程鎖相環(huán)(PLL)解決方案有多種尺寸和類型可供選擇。 PLL以整數(shù)N或小數(shù)N形式提供同時根據(jù)帶寬利用無源或有源環(huán)路濾波器。 可以通過3線串行接口對其進行快速編程同時提供非常低的雜散抑制和較小

2021-04-03 17:00:58

概述:SC9257是杭州士蘭微電子生產(chǎn)的一款數(shù)字調(diào)諧系統(tǒng)鎖相環(huán)(PLL FOR DTS)。該SC9257是鎖相環(huán)(PLL)的LSI數(shù)字調(diào)諧系統(tǒng)(DTS)與內(nèi)置的2模數(shù)預(yù)分頻器。所有功能都通過3根串行

2021-05-18 07:27:48

鎖相環(huán)SFS12000C-LF鎖相環(huán)SFS12500C-LF鎖相環(huán)SFS12800C-LF鎖相環(huán)SFS14000H-LF鎖相環(huán)SFS15000C-LF鎖相環(huán)深圳市立年電子科技有限公司 --射頻微波一站式采購產(chǎn)臺聯(lián)系人:王先生 ***QQ330538935`

2021-04-03 17:05:46

有沒有大神有用Verilog代碼寫的數(shù)字鎖相環(huán)程序呀,求 。謝謝

2017-07-05 22:54:56

鎖相環(huán)路是一種反饋控制電路,簡稱鎖相環(huán)(PLL)。許多電子設(shè)備要正常工作,通常需要外部的輸入信號與內(nèi)部的振蕩信號同步,利用鎖相環(huán)路就可以實現(xiàn)這個目的。鎖相環(huán)通常由鑒相器(PD)、環(huán)路濾波器(LF

2019-03-17 06:00:00

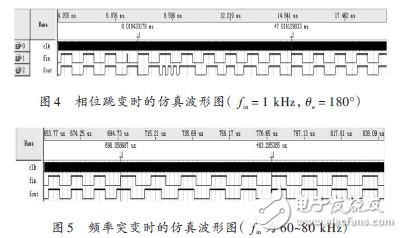

今天主要介紹鎖相環(huán),下面分兩部分來介紹。第一部分先了解鎖相環(huán)基本組成和工作原理,第二部分介紹了一種采用VERILOG硬件描述語言設(shè)計DPLL的方案。

2019-06-21 06:27:44

摘要:數(shù)字三相鎖相環(huán)中含有大量乘法運算和三角函數(shù)運算,占用大量的硬件邏輯資源。為此,提出一種數(shù)字三相鎖相環(huán)的優(yōu)化實現(xiàn)方案,利用乘法模塊復(fù)用和CORDIC算法實現(xiàn)三角函數(shù)運算,并用Vetilog

2019-06-27 07:02:23

本文設(shè)計了一種多環(huán)鎖相頻率合成器。多環(huán)鎖相環(huán)路有直接數(shù)字頻率合成(DDS)環(huán)路和鎖相頻率合成環(huán)路(PLL)組成。充分利用兩個不同環(huán)路的優(yōu)點,既保證了高的輸出頻率,又得到了較高的頻率分辨率。【關(guān)鍵詞

2010-05-13 09:09:53

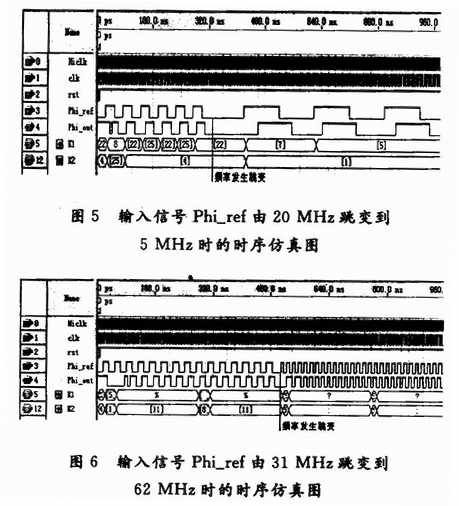

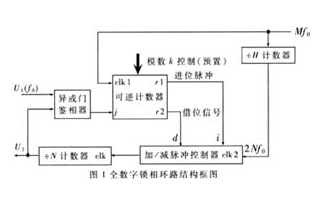

隨著集成電路技術(shù)的不斷進步,數(shù)字化應(yīng)用逐漸普及,在數(shù)字通信、電力系統(tǒng)自動化等方面越來越多地運用了數(shù)字鎖相環(huán)。它的好處在于免去了模擬器件的繁瑣,而且成本低、易實現(xiàn)、省資源。本文綜合以上考慮,在一片F(xiàn)PGA中以Quartus II為平臺用VHDL實現(xiàn)了一個全數(shù)字鎖相環(huán)功能模塊,構(gòu)成了片內(nèi)鎖相環(huán)。

2019-10-10 06:12:52

DLL架構(gòu)和工作原理是什么?如何設(shè)計一種新延時鎖相環(huán)架構(gòu)OSDLL?

2021-05-07 06:17:59

鎖相環(huán)系統(tǒng)是什么工作原理?傳統(tǒng)電荷泵電路存在的不理想因素有哪些?設(shè)計一種高性能CMOS電荷泵鎖相環(huán)電路

2021-04-09 06:38:45

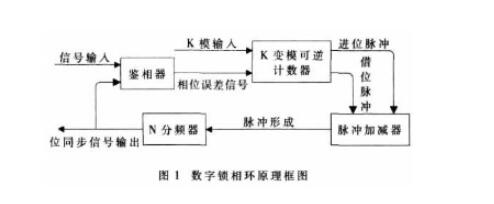

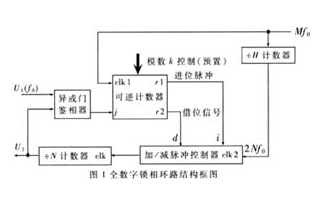

全數(shù)字鎖相環(huán)由那幾部分組成?數(shù)字鎖相環(huán)的原理是什么?如何采用VHDL實現(xiàn)全數(shù)字鎖相環(huán)電路的設(shè)計?

2021-05-07 06:14:44

控制用微處理器的主要性能有哪些?處理器在調(diào)頻(FM)調(diào)諧器中的應(yīng)用是什么?數(shù)字調(diào)諧系統(tǒng)有哪些性質(zhì)?怎樣去設(shè)計一種基于PLL(鎖相環(huán))合成器的數(shù)字調(diào)諧系統(tǒng)?

2021-08-17 07:03:36

模擬鎖相環(huán)與數(shù)字鎖相環(huán)的主要區(qū)別在哪里?

2023-04-24 10:48:52

經(jīng)典數(shù)字鎖相環(huán)路結(jié)構(gòu)及工作原理是什么?改進的數(shù)字鎖相環(huán)結(jié)構(gòu)及工作原理是什么怎樣對改進的數(shù)字鎖相環(huán)進行仿真?

2021-04-20 06:47:12

求一種新型WCDMA直放站PA的設(shè)計方案

2021-05-26 06:14:52

求一種新型系統(tǒng)級可編程芯片的設(shè)計方案

2021-05-06 07:44:32

求一種基于FPGA的鎖相環(huán)位同步提取電路的設(shè)計方案。

2021-04-29 06:52:21

求一種DSP+CPLD新型的智能儀器的設(shè)計方案

2021-05-08 07:54:25

數(shù)字鎖相環(huán)頻率合成系統(tǒng)的工作原理CPU控制數(shù)字鎖相環(huán)頻率合成系統(tǒng)FPGA實現(xiàn)

2021-04-09 06:20:37

本文主要研究了一種基于FPGA、自頂向下、模塊化、用于提取位同步時鐘的全數(shù)字鎖相環(huán)設(shè)計方法。

2021-05-06 08:00:46

本文介紹了電荷泵鎖相環(huán)電路鎖定檢測的基本原理,通過分析影響鎖相環(huán)數(shù)字鎖定電路的關(guān)鍵因子,推導(dǎo)出相位誤差的計算公式。并以CDCE72010 為例子,通過實驗驗證了不合理的電路設(shè)計或外圍電路參數(shù)是如何影響電荷泵鎖相環(huán)芯片數(shù)字鎖定指示的準確性。

2021-04-20 06:00:37

數(shù)字鎖相環(huán)的參考信號可以是正弦信號嗎

2018-08-18 06:55:49

怎么設(shè)計一種無鎖相環(huán)的交流電壓全周期過零檢測電路?無鎖相環(huán)電壓全周期過零檢測電路原理是什么?如何設(shè)置交流電壓全周期過零檢測電路系統(tǒng)仿真參數(shù)?

2021-04-14 06:41:47

怎么設(shè)計一種用于多路輸出時鐘緩沖器中的鎖相環(huán)?鎖相環(huán)主要結(jié)構(gòu)包括哪些?

2021-04-20 06:27:26

怎樣去設(shè)計一種自適應(yīng)軟件鎖相環(huán)?如何對自適應(yīng)軟件鎖相環(huán)進行測試?

2021-06-08 07:07:17

怎樣去設(shè)計一種COMS集成鎖相環(huán)電路?

2021-06-22 07:37:23

軟件鎖相環(huán)的基本模型軟件鎖相環(huán)的數(shù)學模型多速率條件下的軟件鎖相環(huán)軟件鎖相環(huán)的DSP實現(xiàn)

2021-04-21 07:22:49

您好! 請問ADI是否這樣的鎖相環(huán)芯片,在外參考輸入時鐘不關(guān)的情況下,開關(guān)鎖相環(huán)芯片,鎖相環(huán)輸出時鐘相位保持一致,也就是說只要輸入?yún)⒖疾蛔儯_關(guān)鎖相環(huán)芯片,輸出時鐘相位保持不變,若變,變化范圍是多大, 若無此類鎖相環(huán)芯片,請問ADI是否有此類問題的解決方案。 十分感謝!!

2018-08-31 11:00:43

我剛接觸鎖相環(huán)沒多長時間,最近想使用ADF4106搭建一個雙環(huán)鎖相環(huán),我閱讀的資料都沒有說主環(huán)路環(huán)路濾波器參數(shù)計算問題,我想咨詢專家ADIsimPLL是否可以仿真計算雙環(huán)鎖相環(huán),如果可以具體怎么考慮,如果可以告訴我一些主環(huán)路環(huán)路帶寬的知識就更好了.

2019-03-07 10:34:03

本帖最后由 gk320830 于 2015-3-7 16:40 編輯

高速數(shù)字鎖相環(huán)的原理及應(yīng)用

2012-08-17 10:47:04

本文針對一款應(yīng)用于大規(guī)模集成電路的CMOS高頻鎖相環(huán)時鐘發(fā)生器,提出了一種可行的測試方案,重點講述了鎖相環(huán)的輸出頻率和鎖定時間參數(shù)的測試,給出了具體的測試電路和測試方法。對于應(yīng)用在大規(guī)模電路系統(tǒng)中的鎖相環(huán)模塊,該測試方案既可用于鎖相環(huán)的性能評測,也可用于鎖相環(huán)的生產(chǎn)測試。

2021-04-21 06:28:15

智能全數(shù)字鎖相環(huán)的設(shè)計

摘要: 在FPGA片內(nèi)實現(xiàn)全數(shù)字

2008-08-14 22:12:51 56

56 Crystek Corporation 的 CPLL66-4160-4380 是一種鎖相環(huán),工作頻率為 4160 至 4380 MHz。它是一個完整的 PLL/合成器,只需要一個外部頻率

2022-11-25 14:48:16

智能全數(shù)字鎖相環(huán)的設(shè)計:在FPGA片內(nèi)實現(xiàn)全數(shù)字鎖相環(huán)用途極廣。本文在集成數(shù)字鎖相環(huán)74297的基礎(chǔ)上進行改進,設(shè)計了鎖相狀態(tài)檢測電路,配合CPU對環(huán)路濾波參數(shù)進行動態(tài)智能配

2009-06-25 23:32:57 72

72 基于FPGA的全數(shù)字鎖相環(huán)設(shè)計:

2009-06-26 17:30:59 141

141 介紹了應(yīng)用VHDL技術(shù)設(shè)計嵌入式全數(shù)字鎖相環(huán)路的方法。詳細敘述了其工作原理和設(shè)計思路,并用可編程邏輯器件FPCA予以實現(xiàn)。

2009-07-21 16:46:41 0

0 本文在介紹了經(jīng)典全數(shù)字鎖相環(huán)(all digital PLL, ADPLL)的基礎(chǔ)上,提出了具有捕獲鎖定未知輸入信號頻率功能的ADPLL,使用方便,應(yīng)用廣泛。本文詳盡的描述了系統(tǒng)的工作原理和關(guān)

2009-08-29 10:07:08 43

43 該文簡要討論了環(huán)路性能(建立時間,相位噪聲和雜散信號)和環(huán)路參數(shù)(帶寬,相位裕度等)的相互關(guān)系。提出并分析了一種自適應(yīng)的具有快速建立時間的鎖相環(huán)結(jié)構(gòu)及其關(guān)鍵模塊(鑒相

2010-04-23 08:33:53 20

20 鎖相環(huán)被廣泛應(yīng)用于電力系統(tǒng)的測量和控制中。介紹了一種新型的基于比例積分控制邏輯的全數(shù)字鎖相環(huán)。通過對其數(shù)學模型的分析,闡述了該鎖相環(huán)的各項性能指標與設(shè)計參數(shù)的

2010-07-02 16:54:10 30

30 本文在分析商用全數(shù)字鎖相環(huán)的常用技術(shù)和低頻信號的特點后,提出一種適用于低頻信號的基于CPLD的鎖相環(huán)實現(xiàn)方法。

2010-08-06 14:39:19 118

118 介紹了應(yīng)用VHDL技術(shù)設(shè)計嵌入式全數(shù)字鎖相環(huán)路的方法。詳細描

2010-09-19 10:09:14 68

68

利用鎖相環(huán)進行載波跟蹤是獲取本地載波的一種重要方法,針對鎖相環(huán)的噪聲性能和跟蹤速度不能同時達到最優(yōu)的限制,在鎖相環(huán)PLL中引入自適應(yīng)模塊,根據(jù)環(huán)路所處

2010-11-25 17:19:33 29

29 摘要: 在FPGA片內(nèi)實現(xiàn)全數(shù)字鎖相環(huán)用途極廣。本文在集成數(shù)字鎖相環(huán)74297的基礎(chǔ)上進行改進,設(shè)計了鎖相狀態(tài)檢測電路,配合CPU對環(huán)路濾波參數(shù)進行動態(tài)智

2009-06-20 12:39:32 1408

1408

針對擴頻通信系統(tǒng)的載波同步,提出一套完善的數(shù)字鎖相環(huán)設(shè)計方案. 該方案利用新穎的可控根法完成1~3階模擬鎖相環(huán)(APLL)環(huán)路參數(shù)設(shè)計,并實現(xiàn)從模擬域到數(shù)字域的轉(zhuǎn)換,得到的數(shù)字鎖相

2011-08-26 16:10:38 122

122 針對傳統(tǒng)的全數(shù)字鎖相環(huán)只能鎖定已知信號和鎖頻范圍較小的問題, 提出了一種自動變模控制的寬頻帶全數(shù)字鎖相環(huán)。對比分析了各類全數(shù)字鎖相環(huán)鎖頻、鎖相的工作機理, 提出了一種新

2011-09-14 15:22:22 79

79 研究了一種利用corid 算法的矢量及旋轉(zhuǎn)模式對載波同步中相位偏移進行估計并校正的方法.設(shè)計并實現(xiàn)了基于corid 算法的數(shù)字鎖相環(huán).通過仿真驗證了設(shè)計的有效性和高效性.

2012-02-09 16:48:30 18

18 一種基于bang_bang鑒頻鑒相器的全數(shù)字鎖相環(huán)設(shè)計_陳原聰

2017-01-07 20:49:27 11

11 為了能夠有效地治理諧波,提高電力系統(tǒng)中諧波信息的檢測精度,提出了自適應(yīng)鎖相環(huán)的分次諧波檢測優(yōu)化算法。首先,研究了改進自適應(yīng)鎖相環(huán)的設(shè)計方法,并且構(gòu)造了相應(yīng)的數(shù)學模型;其次,設(shè)計了分次諧波檢測優(yōu)化算法

2017-10-30 16:16:15 11

11 隨著集成電路技術(shù)的不斷進步,數(shù)字化應(yīng)用逐漸普及,在數(shù)字通信、電力系統(tǒng)自動化等方面越來越多地運用了數(shù)字鎖相環(huán)。它的好處在于免去了模擬器件的繁瑣,而且成本低、易實現(xiàn)、省資源。本文綜合以上考慮,在一片F(xiàn)PGA中以Quartus II為平臺用VHDL實現(xiàn)了一個全數(shù)字鎖相環(huán)功能模塊,構(gòu)成了片內(nèi)鎖相環(huán)。

2020-07-16 09:16:08 2465

2465

技術(shù)的發(fā)展,不僅能夠制成頻率較高的單片集成鎖相環(huán)路,而且可以把整個系統(tǒng)集成到一個芯片上去,實現(xiàn)所謂片上系統(tǒng)SOC(System on a chip)。因此,可以把全數(shù)字鎖相環(huán)路作為一個功能模塊嵌入SOC,構(gòu)成片內(nèi)鎖相環(huán)。下面介紹采用VHDL技術(shù)設(shè)計DPLL的一種方案。

2020-07-23 16:23:25 1087

1087

本文提出了一種適用范圍廣泛的全數(shù)字鎖相環(huán)(ADPLL)實現(xiàn)方法.在鎖相環(huán)輸入頻率未知的情況下,實現(xiàn)鎖相鎖頻功能。本文從全數(shù)字鎖相環(huán)的基本實現(xiàn)方式入手.進行改進,并使用VH DL語言建模,使用FPGA進行驗證。

2021-01-26 15:03:00 65

65 本文提出了一種適用范圍廣泛的全數(shù)字鎖相環(huán)(ADPLL)實現(xiàn)方法.在鎖相環(huán)輸入頻率未知的情況下,實現(xiàn)鎖相鎖頻功能。本文從全數(shù)字鎖相環(huán)的基本實現(xiàn)方式入手.進行改進,并使用VH DL語言建模,使用FPGA進行驗證。

2021-01-26 15:03:00 18

18 為了提高全數(shù)字鎖相環(huán)的系統(tǒng)運行速度、降低系統(tǒng)功耗,同時提高鎖相系統(tǒng)的動態(tài)性能與穩(wěn)態(tài)性能,提出一種基于流

2021-04-01 11:53:12 1740

1740

基于FPGA的高性能全數(shù)字鎖相環(huán)

2021-06-08 11:09:01 45

45 電子發(fā)燒友網(wǎng)站提供《基于VHDL的全數(shù)字鎖相環(huán)的設(shè)計.pdf》資料免費下載

2023-11-10 09:47:34 0

0 V CO 輸出本地參考頻率。由于V CO 采用模擬電路, 這將帶來元件 飽和、直流漂移、非線性等問題。因此, 全數(shù)字鎖相環(huán)得到了越來越廣泛的應(yīng)用。

本文介紹一種 DD S(D irect D igital Syn thesizer) 與 PLL (Phase L ocked L oop ) 技術(shù)

2023-11-09 08:31:40 1

1

電子發(fā)燒友App

電子發(fā)燒友App

評論