鎖相環仿真,可以參考一下!

2012-08-13 09:11:17

問一下大家,labview的鎖相環怎么設計,我不知道怎么設計NCO,計算頻率控制字的時候需要系統時鐘頻率,但是這個不知道怎么弄,大家有知道的嗎,幫一下忙,謝謝!

2017-06-20 10:36:08

鎖相環鎖定與失鎖的標志是什么?

2023-04-24 10:12:07

要實現鎖相環的基本原理及工作狀態,如何編寫程序呢?

2014-06-11 21:33:38

請問鎖相環仿真用什么軟件好,我們需要用到ADF4110VOC選擇MAX2606

2016-06-27 15:57:53

鎖相環在鎖定狀態時,vco輸出波形相對輸入波形是否有相位移動?

2023-04-24 11:34:10

1、電力系統中的鎖相環與其他領域鎖相環的區別鎖相環這個概念很早就聽說過,但是一直不明白是什么意思,在很多地方都能遇到,搞不懂鎖相環的時候,就去百度搜一下,結果發下百度上給的結果更看不懂,后來經人點撥

2015-01-04 22:57:15

我用msp430和adf4106加一個vco 和環路濾波做了一個鎖相環,但頻率漂到其他地方了!請大神解決

2016-01-20 15:07:57

聽說鎖相環可以倍頻,倍頻時輸入輸出頻率都不一樣,如何鎖相呢?

2023-04-24 10:14:34

不僅包括整數分頻,小數分頻VCO外置產品,還包括集成了VCO的產品,從而大大簡化您的設計,降低系統成本。 整數分頻PLL小數分頻PLL單環PLL雙環PLL集成VCO的PLL快速鎖定PLL高電壓電荷泵PLL附件鎖相環常見問題解答.pdf518.7 KB

2018-10-31 15:08:45

保證環路所要求的性能, 增加系統的穩定性。壓控振蕩器受濾波器輸出的電壓控制, 使得壓控振蕩器的頻率向輸入信號的頻率靠攏, 也就是使差拍頻率越來越低, 直至消除頻率差而鎖定。鎖相環在開始工作時, 通常輸入

2022-06-22 19:16:46

鎖相環未鎖定前,兩個頻率不同,如何表示環路的瞬時頻差和瞬時相差?

2023-04-24 11:31:07

我有一個鎖相環電路的pcb板和proteus仿真電路。

2023-10-04 07:58:55

本帖最后由 gk320830 于 2015-3-7 20:18 編輯

鎖相環的原理,特性與分析所謂鎖相環路,實際是指自動相位控制電路(APC),它是利用兩個電信號的相位誤差,通過環路自身調整作用,實現頻率準確跟蹤的系統,稱該系統為鎖相環路,簡稱環路,通常用PLL 表示。

2008-08-15 13:18:46

電荷泵鎖相環的基本原理是什么?電荷泵鎖相環的噪聲模型與相位噪聲特性是什么?電荷泵鎖相環的相位噪聲與環路帶寬關系是什么?

2021-06-07 06:57:53

本帖最后由 zhihuizhou 于 2011-12-21 17:43 編輯

鎖相環PLL原理與應用 第一部分:鎖相環基本原理 一、鎖相環基本組成 二、鑒相器(PD) 三

2011-12-21 17:35:00

那個對講機的鎖相環的程序怎么寫?是基于STM32單片機的,鎖相環芯片使用的是LMX2337

2014-04-09 08:18:49

當鎖相環達到鎖定狀態時,VCO輸出頻率與參考頻率相等(假設沒有分頻),那么它們的相位是不是相等呢?還是保持恒定的相位差呢?如果是相位相等,那么是怎么使它們的初相相等的呢?如果是保持恒定的相位差,那么

2023-04-24 11:32:51

本人在進在做鎖相環的仿真,進行頻率跟蹤的用的,可是怎么做都放不出波形,可有會仿真鎖相環的?

2014-06-23 11:14:38

鎖相環使兩個波型相位相同, 當上電時有時兩個波相位相同,有時不同是什么原因?急需要答案

2016-03-16 20:57:29

頻率合成器的主要性能指標鎖相環頻率合成器原理鎖相環頻率合成器捕捉過程的分析與仿真

2021-04-22 06:27:35

[size=10.5000pt]最近正在測試貴公司的AD9510-VCO/PCBZ的開發板,但在測試中發現鎖相環時鐘無法鎖定,現將具體的配置參數發于您,請給與指導,看是否是配置錯誤導致鎖相環無法鎖定

2018-09-29 15:22:33

10110111,reg10配置為11100000。鎖定指示一直不能拉高,鎖相環無法鎖定,芯片不工作。檢查了參考時鐘,共模電壓為400mv,vpp為900mv,時鐘質量沒有問題。

2023-12-04 08:29:29

各位達人們,現在正在使用9910產生點頻信號,現在出現了點問題,求助~~若使用1.0G外部時鐘 配置寄存器可以產生210M點頻信號,然后將時鐘換為40M后倍頻系數25倍,發現鎖相環不能鎖定,但是將

2018-11-07 08:59:52

如題,AD9957的鎖相環一直失鎖,不用鎖相環輸出點頻信號時正常的,用了鎖相環后,PLL_LOCK信號一直為低,sync_clk輸出信號也不是穩定的周期信號,環路濾波器的值有點誤差,因為現有的器件沒有那么精確的電容電阻值,問下鎖相環的控制除了控制CFR3之外還有別的要注意的么?

2018-12-10 09:30:24

原理圖如下:該電路共做過兩版電路板,第一次的直接配置后成功輸出,但第二版在對VCO電感位置進行移動后鎖相環無法鎖定。定義輸出為920.125MHz,實際輸出為915MHz。MUXOUT設定的鎖相環

2018-09-04 11:36:37

求一ADF5355_鎖相環相關資料,最好中文版,詳細點

2017-03-06 23:32:13

大家好,我現在在使用ADRF6850的過程中,出現鎖相環無法鎖定頻率的情況,我現在要出一個434MHz的頻率的LO,從LOMON腳去看的話,是有波形輸出的,但是波形的頻率不固定。一直在緩慢的飄。我

2019-01-10 11:51:11

新版AD公司鎖相環仿真軟件

2013-07-20 21:44:03

鎖相有何意義?CD4046的工作原理是什么?CD4046鎖相環有什么應用?

2021-05-27 07:07:38

求助,CD4046鎖相環的參數要怎么設計呀?我設計的時候是根據datasheet設計的,可是用protues仿真的時候,在中心頻率也入不了鎖,引腳1輸出總是一高一低,然后把輸入信號的電壓調大后,不管

2020-10-11 13:02:47

跪求哪位大神曾經實際驗證TI自帶軟件鎖相環的正確性(單相‘三相皆可)并最終用示波器拍圖驗證成功的???最好示波器圖是白底,而且是那種帶有U盤可以拷貝圖片示波器出來的圖形。急求!急求!急求!

2017-05-28 18:09:34

LabVIEW鎖相環(PLL) 鎖相環是一種反饋電路,其作用是使得電路上的時鐘和某一外部時鐘的相位同步。PLL通過比較外部信號的相位和由壓控晶振(VCXO)的相位來實現同步的,在比較的過程中,鎖相環

2022-05-31 19:58:27

在使用K60的過程中發現自己pllinit()不清楚,才發覺自己鎖相環的概念還不懂,so,趕緊補補……鎖相環(PLL: Phase-locked loops)是一種利用反饋(Feedback)控制

2021-11-04 08:57:18

PLL(鎖相環)電路原理是什么?

2022-01-21 07:03:37

`可編程鎖相環(PLL)解決方案有多種尺寸和類型可供選擇。 PLL以整數N或小數N形式提供同時根據帶寬利用無源或有源環路濾波器。 可以通過3線串行接口對其進行快速編程同時提供非常低的雜散抑制和較小

2021-04-03 17:00:58

信號源的任何應用的理想選擇,并且利用微帶或陶瓷諧振器拓撲結構可提供出色的相位噪聲性能。測試儀器雷達系統SFS10500H-LF鎖相環SFS10625H-LF鎖相環SFS10640H-LF鎖相環

2021-04-03 17:05:46

labview虛擬鎖相環的跟蹤鎖定時間過長,請問有什么辦法可以解決這個問題

2011-05-17 19:03:34

的例子中,osc_ok 位和 pll_ok 位未設置,但 rf_ok 位已設置。這怎么可能?rf_ok 位應在場斜升完成時設置。osc_ok 位未設置的原因可能是什么?以及如何鎖定鎖相環?

2022-12-21 07:12:03

采用后向Euler數值積分法實現二階鎖相環的一個仿真模型,對二階鎖相環進行仿真,那位大俠做過?可以參考下原代碼不?

2012-05-28 17:21:05

應用中的疑問:1、傳輸線為2~5米,產生的附加抖動易引起鎖相環失鎖嗎?鎖相環對輸入信號的抖動范圍有要求嗎?為保證輸出的200MHz時鐘穩定,鎖相環對輸入的時鐘信號有什么具體的要求?2、在鎖定的狀態下,若

2018-09-18 11:14:35

全數字鎖相環的設計及分析 1 引 言 鎖相環是一種能使輸出信號在頻率和相位上與輸入信號同步的電路,即系統進入鎖定狀態(或同步狀態)后,震蕩器的輸出信號與系統輸入信號之間相差為零,或者保持為常數

2010-03-16 10:56:10

=rgb(0, 66, 118) !important] 鎖相環電路主要用于分頻倍頻,頻率合成,解碼… 該電路利用VOC的鎖定工作,有良好的特性及抗干擾性能。 鑒相器是個相位比較裝置。它把輸入信號

2019-03-17 06:00:00

本人在使用ADF4372芯片時,運用RF16輸出口,鎖相環正常鎖定,但是輸出幅度只有-28dbm,這是為什么,請求解答謝謝。沒有在VDDX1加7.4nH電感。

2024-01-03 07:39:15

有沒有大神有用Verilog代碼寫的數字鎖相環程序呀,求 。謝謝

2017-07-05 22:54:56

小弟需要對正弦信號進行鎖相,就是鎖相環的輸入輸出都是正弦信號,有合適的芯片嗎?最好給點資料,小弟急需!!還有芯片要可以外接倍頻單元。在此謝過了!!!

2011-03-13 09:46:00

請問可以用鎖相環來制作DDS嗎?并且用單片機控制

2016-06-28 17:51:01

一、內容繼續無霍爾的學習,根據原理及仿真,了解相關原理和實現方法。二、知識點1.基于鎖相環的轉子位置估計反正切函數的轉子位置估算由于是根據估算的擴展反電動勢進行計算的,但是由于滑模控制在滑動模態下

2021-08-27 06:54:13

HDL硬件描述語言對優化前后的算法進行了編碼實現。仿真和實驗結果表明,優化后的數字三相鎖相環大大節省了FPGA的資源,并能快速、準確地鎖定相位,具有良好的性能。關鍵詞:FPGA;三相鎖相環;乘法復用;CORDIC

2019-06-27 07:02:23

全數字鎖相環由那幾部分組成?數字鎖相環的原理是什么?如何采用VHDL實現全數字鎖相環電路的設計?

2021-05-07 06:14:44

本帖最后由 gk320830 于 2015-3-9 20:38 編輯

最近在用adf 4001做一個鎖相環,環路配置好后發現鎖定不了,電荷泵cp 輸出一直在掃描,檢查芯片內部的配置,也沒發現什么問題,分頻輸出也是正常的,哪位高手用過這個芯片,幫我分析分析吧,期待中。。。

2010-09-14 08:52:16

本文按照數字鎖相環設計的步驟,采用手把手的方式講述設計過程和原理,旨在給數字鎖相環初次設計者提供一個思路,縮短開發的時間。 有關數字鎖相環的帖子不斷出現,但大多沒有講述其原理。翻開有關鎖相環的書總是

2012-01-12 15:29:12

數字鎖相環設計源程序PLL是數字鎖相環設計源程序, 其中, Fi是輸入頻率(接收數據), Fo(Q5)是本地輸出頻率.目的是從輸入數據中提取時鐘信號(Q5), 其頻率與數據速率一致, 時鐘上升沿鎖定在數據的上升和下降沿上;頂層文件是PLL.GDF

2009-12-18 10:37:37

fpga中的用鎖相環產生時鐘信號相比于用計數器進行分頻有哪些優點,看fpga中鎖相環的結構,其前期的輸入信號和后期的輸出信號不也是通過計數器進行分頻實現的嗎

2014-10-06 10:46:05

模擬鎖相環與數字鎖相環的主要區別在哪里?

2023-04-24 10:48:52

經典數字鎖相環路結構及工作原理是什么?改進的數字鎖相環結構及工作原理是什么怎樣對改進的數字鎖相環進行仿真?

2021-04-20 06:47:12

大家好,我的課題是要用FPGA做一個高精度鎖相環。這個數字鎖相環的工作原理為:正弦模擬信號通過低通濾波器后,經過模數轉換器(ADC)轉化為數字信號,與NCO(數控振蕩器) 的輸出信號相乘后濾波,從而

2016-08-15 11:31:56

本文介紹了電荷泵鎖相環電路鎖定檢測的基本原理,通過分析影響鎖相環數字鎖定電路的關鍵因子,推導出相位誤差的計算公式。并以CDCE72010 為例子,通過實驗驗證了不合理的電路設計或外圍電路參數是如何影響電荷泵鎖相環芯片數字鎖定指示的準確性。

2021-04-20 06:00:37

請問一下鎖相環無法鎖定怎么辦?

2023-04-24 10:09:02

軟件鎖相環的基本模型軟件鎖相環的數學模型多速率條件下的軟件鎖相環軟件鎖相環的DSP實現

2021-04-21 07:22:49

數字鎖相環可以用于鎖定正弦信號嗎?

2019-02-18 07:38:23

請問各位工程師,有沒有能快速鎖定的鎖相環推薦啊,最好是集成VCO的,謝謝啦!

2018-08-15 06:41:29

我剛接觸鎖相環沒多長時間,最近想使用ADF4106搭建一個雙環鎖相環,我閱讀的資料都沒有說主環路環路濾波器參數計算問題,我想咨詢專家ADIsimPLL是否可以仿真計算雙環鎖相環,如果可以具體怎么考慮,如果可以告訴我一些主環路環路帶寬的知識就更好了.

2019-03-07 10:34:03

音頻鎖相環相關資料集很多好資料哦! [hide]音頻鎖相環相關資料等.rar[/hide]

2009-12-04 11:43:03

本帖最后由 gk320830 于 2015-3-7 16:40 編輯

高速數字鎖相環的原理及應用

2012-08-17 10:47:04

本文針對一款應用于大規模集成電路的CMOS高頻鎖相環時鐘發生器,提出了一種可行的測試方案,重點講述了鎖相環的輸出頻率和鎖定時間參數的測試,給出了具體的測試電路和測試方法。對于應用在大規模電路系統中的鎖相環模塊,該測試方案既可用于鎖相環的性能評測,也可用于鎖相環的生產測試。

2021-04-21 06:28:15

本文對電荷泵型鎖相環(CPPLL)結構里傳統的固定電荷泵電流模式進行了改進,有效減少了鎖相環系統的鎖定時間。本文提出的PLL設計,在0.6μm標準CMOS工藝、3.3V工作電壓下,使用應用

2010-08-03 16:10:33 21

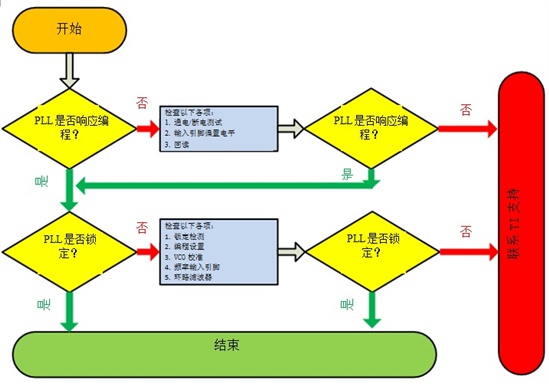

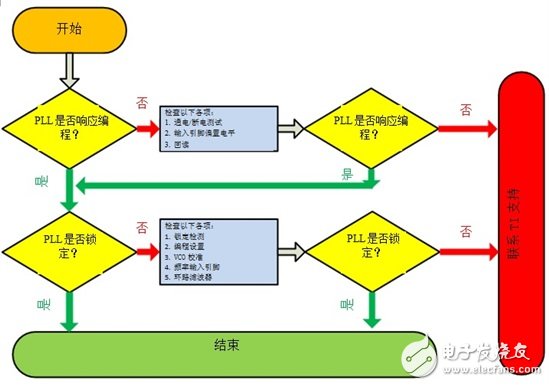

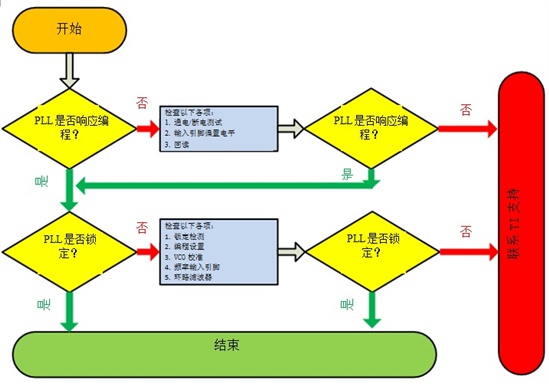

21 在嘗試將鎖相環(PLL)鎖定時,你是否碰到過麻煩?草率的判斷會延長調試過程,調試過程變得更加單調乏味。根據以

2017-10-16 11:49:30 5147

5147

在嘗試將鎖相環(PLL)鎖定時,你是否碰到過麻煩?草率的判斷會延長調試過程,調試過程變得更加單調乏味。根據以下驗證通行與建立鎖定的程序,調試過程可以變得非常簡單。

第1步:驗證通信

第一步是驗證

2021-11-26 16:32:38 5146

5146

如何解決鎖相環無法鎖定

2022-11-02 08:16:21 3

3 軟件鎖相環在頻率突變時鎖不住 鎖相環無法鎖定怎么辦?? 鎖相環(PLL)是一種用于在電路中生成穩定頻率的技術。它是在1960年代開發的,并被廣泛應用于通信、雷達、衛星技術等領域中。鎖相環的主要作用

2023-10-13 17:39:58 723

723 當鎖相環無法鎖定時,該怎么處理的呢?如何解決鎖相環無法鎖定? 鎖相環作為一種常見的電路設計,具有廣泛的應用領域。然而,在一些情況下,由于種種原因,鎖相環可能無法正常鎖定,這時需要進行一系列的測試

2023-10-30 10:16:33 971

971 鎖相環鎖定時間取決于哪些因素?如何加速鎖定? 鎖相環(PLL)是一種常見的電路,用于穩定頻率。PLL中的關鍵是相鎖。相鎖發揮著將輸入頻率與參考頻率調整到相等的重要作用。在鎖相環設計中,鎖定

2023-10-30 10:51:18 899

899 鎖相環鎖定后一定不存在頻差嗎? 鎖相環是一種常用的控制系統,用于將輸入信號與參考信號之間的相位誤差維持在一個可接受的范圍內。它通過調節輸出信號的相位和頻率來實現這個目標。然而,鎖相環鎖定后并不能完全

2024-01-31 15:25:05 167

167

電子發燒友App

電子發燒友App

評論