LTC6247的典型應用 -180MHz,1mA功率高效雙軌到軌I / O運算放大器。 LTC6246 / LTC6247 / LTC6248是單/雙/四路低功耗,高速單位增益穩(wěn)定軌到軌輸入/輸出運算放大器

2019-06-10 09:35:48

LTC6248的典型應用 -180MHz,1mA高功效四路軌到軌I / O運算放大器。 LTC6246 / LTC6247 / LTC6248是單/雙/四路低功耗,高速單位增益穩(wěn)定軌到軌輸入/輸出運算放大器

2020-06-05 11:01:48

單、雙和四路低壓(2.7伏至5.5伏)具有軌對軌輸出擺動的運算放大器。LMV324S設備,它是標準的變體LMV324設備,包括一個省電關(guān)機功能,當放大器不需要。通道1和通道2一起關(guān)閉,通道3和通道4也

2020-10-12 16:57:30

DN254-LT1806:325MHz低噪聲軌到軌SOT-23運算放大器可節(jié)省電路板空間

2019-07-26 12:24:35

任何給定的單元,都存在一個使輸入電流為零的輸入電壓(假設沒有顯著的封裝或者電路版圖的泄漏)。事實上,使用軌到軌運算放大器時,通常可以在輸入端使用自偏置(圖2),同時輸出將漂移到對應零輸入偏置電流點的電壓

2018-09-21 15:39:02

概述:LTC6084采用8引腳MSOP和10引腳DFN封裝。是雙通道、低成本、低失調(diào)、軌至軌輸入/輸出、單位增益穩(wěn)定的 CMOS 運算放大器,具有1pA的輸入偏置電流。

2021-04-12 06:40:23

LTC6241是一款雙通道和四通道低噪聲、低失調(diào)、軌至軌輸出、具穩(wěn)定單位增益的 CMOS 運算放大器,它們具有 1pA 的輸入偏置電流。在單通道器件 LTC6240 上,最大輸入偏置電流保證為 1pA。

2021-04-12 07:31:00

本文主要討論CMOS低電壓運算放大器輸入級所面臨的問題和解決的方法。

2021-04-22 06:26:08

性能。市面上很少能見到兼具所有這些特性的運算放大器。 但是,您可以使用兩個單獨的放大器來構(gòu)建這種放大器,形成復合放大器。將兩個運算放大器組合在一起,就能將各自的優(yōu)勢特性集成于一體。這樣,與具有相同增益的單個

2020-06-03 07:30:20

)。運算放大器的輸出電壓信號是施加到其兩個單獨輸入的信號之間的差。換句話說,運算放大器的輸出信號是兩個輸入信號之間的差,因為運算放大器的輸入級實際上是一個差分放大器,如下所示。差動放大器下面的電路顯示了

2020-12-25 09:05:21

普通放大器如果要用5V供電,最多也只能輸出3.8v左右,如果要輸出接近5V,可以采用8V供電;而軌到軌放大器用5V供電,可以輸出接近5V;如果我要做一個差分放大器,輸出是0-5V,那么,我是用普通放大器提供供電的方法就可以了?

2017-03-07 08:20:28

DN89- 軌到軌放大器的應用

2019-06-14 11:13:30

運算放大器的“軌至軌輸入/輸出”是滿電源幅度輸出的意思,一般的運放輸出的電壓幅度是達不到電源電壓的,會有1V左右的壓差。輸出的最大幅度就能達到多少,還有是它的差分輸入電壓也能達到電源電壓。這類運放

2020-07-23 09:11:32

LTC1152的典型應用是高性能,低功耗零漂移運算放大器,具有輸入級,可與電源軌共用模式,輸出級可提供軌到軌擺動,即使在重負載下也是如此

2020-04-08 09:57:22

本帖最后由 gk320830 于 2015-3-4 16:18 編輯

軌對軌運算放大器的工作原理及優(yōu)勢

2014-06-23 11:12:34

訂購指南典型性能圖操作理論OP179/OP279是模擬設備擴展的單電源設備系列的最新產(chǎn)品,專為多媒體和電信市場設計。它是一個高輸出電流驅(qū)動,軌對軌輸入/輸出運算放大器,由單個+5V電源供電。它也適用于

2020-09-27 17:36:37

概述:LT1880是一款軌至軌輸出、微微安輸入電流、精準運算放大器,它在采用 SOT-23 封裝的情況下提供了高準確度輸入性能和軌至軌輸出擺幅。輸入失調(diào)電壓被修整至低于 150μV,而且低漂移性能在整個工作溫度范圍...

2021-04-08 06:49:29

概述:LT6230是單通道低噪聲、軌至軌輸出、單位增益穩(wěn)定的運算放大器,具有 1.1nV/√Hz 的噪聲電壓,且每個放大器僅吸收 3.5mA 的電源電流。這些放大器將非常低的噪聲和電源電流與一個 215MHz 的增益...

2021-04-09 06:32:50

概述:LT6235是一款四路低噪聲、軌至軌輸出、單位增益穩(wěn)定的運算放大器,它們具有 1.9nV/√Hz 的噪聲電壓,每個放大器僅吸收 1.2mA 的電源電流。

2021-04-12 06:47:43

概述:LTC6240是一款單通道、雙通道和四通道低噪聲、低失調(diào)、軌至軌輸出、具穩(wěn)定單位增益的 CMOS 運算放大器,它們具有 1pA 的輸入偏置電流。在單通道器件 LTC6240 上,最大輸入偏置電流保證為 1pA。

2021-04-09 06:24:28

運算放大器是一個非常通用的裝置,其可以以各種不同的電子電路和應用中使用,從電壓放大器,向過濾器,對信號調(diào)節(jié)器。但是,基于任何通用運算放大器的一種非常簡單且極為有用的運算放大器電路就是Astable

2021-01-09 20:47:24

。工作溫度范圍從-45℃到125℃。低噪聲運放GS863X/872X系列器件是一款低噪聲、低電壓運算放大器,適用于多種應用。GS863X系列具有6MHz單位增益帶寬、4.2V/μS壓擺率,以及良好的電壓

2020-04-27 10:35:17

的一種方法是在比較器周圍提供正反饋。顧名思義,正反饋是一種通過兩個電阻設置的分壓器將同相輸出信號的一部分或一部分反饋到運算放大器的同相輸入的技術(shù)。與他們的比例成正比。在運算放大器比較器周圍使用正反饋意味著

2022-07-11 22:13:27

該運算放大器比較器比較與另一模擬電壓電平一個模擬電壓電平,或一些預先設定的基準電壓,V REF,并且產(chǎn)生基于該電壓比較的輸出信號。換句話說,運算放大器電壓比較器比較兩個電壓輸入的幅度,并確定哪個

2022-05-04 23:36:42

LM358和LM393的表現(xiàn)一如預期。 雙極性軌到軌運算放大器所有雙極性軌到軌輸出運算放大器的電源電流都大于一個 或兩個比較器電路中的“最大”運放電源電流。驅(qū)動輸出 級的方法有多種,將輸出驅(qū)動到一個或另一

2018-08-29 11:55:18

顯示了一個軌至軌運算放大器。它工作時,輸入電壓可以等于甚至略微大于兩個電源電壓軌,如圖 3 所示。軌至軌輸出意味著,輸出電壓可以非常接近于軌,但通常在電源軌的 10mV 到 100mV 范圍內(nèi)。一

2018-09-26 11:30:17

運算放大器

所有雙極性軌到軌輸出運算放大器的電源電流都大于一個 或兩個比較器電路中的“最大”運放電源電流。驅(qū)動輸出 級的方法有多種,將輸出驅(qū)動到一個或另一個供電軌時, 某些方法會導致電源電流升高。由于

2023-11-21 06:22:21

軌到軌運算放大器所有雙極性軌到軌輸出運算放大器的電源電流都大于一個或兩個比較器電路中的“最大”運放電源電流。驅(qū)動輸出級的方法有多種,將輸出驅(qū)動到一個或另一個供電軌時,某些方法會導致電源電流升高。由于

2018-10-15 10:38:16

雙極性軌到軌輸出運算放大器的電源電流都大于一個或兩個比較器電路中的“最大”運放電源電流。驅(qū)動輸出級的方法有多種,將輸出驅(qū)動到一個或另一個供電軌時,某些方法會導致電源電流升高。由于不熟悉其它制造商產(chǎn)品

2018-10-12 16:40:50

運算放大器的自發(fā)熱降至最低。該附加放大器通常稱為緩沖器,因為其電壓增益通常為1。有一些運算放大器能夠提供大輸出電流。例如AD8534,這是一種四通道器件,四個部分的輸出電流均為250 mA。注意,如果同時

2014-08-13 15:34:22

放大器通常稱為緩沖器,因為其電壓增益通常為1。有一些運算放大器能夠提供大輸出電流。例如AD8534,這是一種四通道器件,四個部分的輸出電流均為250 mA。注意,如果同時從四個部分輸出250 mA電流

2018-09-21 14:50:51

,我們所列出的輸出擺動會不同于表A。例如,表B的輸出擺動表明了輸入過大的輸出電壓。在我們運算放大器開發(fā)組,它被戲稱為“沖撞規(guī)格”,意思是輸入過大,一路沖撞到軌。 兩種規(guī)格都有用,具體取決于你應用的要求。關(guān)鍵是理解并小心解讀各種規(guī)格。

2019-09-27 14:05:58

概述:AD8628是ANALOG DEVICES公司生產(chǎn)的一款零漂移,單電源,超低失調(diào) 輸入/輸出運算放大器。它為寬帶寬、自穩(wěn)零放大器,具有軌到軌輸入和輸出擺幅以及低噪聲特性。它分別為5腳TSOT和8腳SOIC封裝。典型工作電壓2.7 V至5 V單電源(±1.35 V至±2.5 V雙電源)供電。

2021-05-18 07:38:20

概述:AD8629是ANALOG DEVICES公司生產(chǎn)的一款零漂移,單電源,超低失調(diào) 輸入/輸出運算放大器。它為寬帶寬、自穩(wěn)零放大器,具有軌到軌輸入和輸出擺幅以及低噪聲特性。雙列8腳SOIC封裝。典型工作電壓2.7 V至5 V單電源(±1.35 V至±2.5 V雙電源)供電。

2021-05-18 08:06:56

概述:AD8630是ANALOG DEVICES公司生產(chǎn)的一款零漂移,單電源,超低失調(diào) 輸入/輸出運算放大器。它為寬帶寬、自穩(wěn)零放大器,具有軌到軌輸入和輸出擺幅以及低噪聲特性。雙列12腳TSSOP封裝。典型工作電壓2.7 V至5 V單電源(±1.35 V至±2.5 V雙電源)供電。

2021-05-18 07:47:00

應用程序信息 介紹 EL8186是一種具有啟用功能的軌對軌輸入和輸出微功率單電源運算放大器。該裝置實現(xiàn)了軌到軌的輸入和輸出操作,消除了傳統(tǒng)的軌對軌輸入和輸出運算放大器帶來的問題。 軌間

2020-07-16 14:53:59

LT1368的典型應用 - 雙精度軌到軌輸入和輸出運算放大器。 LT1366 / LT1367 / LT1368 / LT1369是雙通道和四通道雙極性運算放大器,將軌到軌輸入和輸出操作與精密規(guī)格相結(jié)合

2020-04-09 06:56:41

LT1806的典型應用 -325MHz,單路,軌到軌輸入和輸出,低失真,低噪聲精密運算放大器。 LT1806 / LT1807是單/雙路低噪聲軌到軌輸入和輸出單位增益穩(wěn)定運算放大器,具有325MHz增益帶寬積,140V / us壓擺率和85mA輸出電流

2020-06-04 16:19:04

NJU77903DL3H 高耐圧大輸出的軌至軌輸入輸出CMOS運算放大器JRC此文章來源于融創(chuàng)芯城(www.digiic.com)—— 半導體電子領(lǐng)域共享平臺概要NJU77903是能獲得大輸出并有

2021-12-09 15:47:07

pA(典型值)?高速度:功率帶寬:1MHz應用?便攜式設備?電池供電設備?煙霧報警器?一氧化碳探測器?醫(yī)療器械說明OPA2348是一種單電源低功耗CMOS運算放大器。OPA2348具有1MHz的擴展帶寬

2020-09-25 17:36:03

運算放大器表現(xiàn)良好,純電容負載高達約300pF。增加增益可以提高放大器驅(qū)動負載的能力。在單位增益配置中改進電容負載驅(qū)動的一種方法是在反饋回路中插入一個50Ω到100Ω的電阻器,如圖3所示。這減少了大電容性

2020-09-27 17:38:18

降低。有關(guān)使用軌對軌輸入運算放大器進行設計的更多信息,請參見圖3,使用軌對軌輸入運算放大器的設計優(yōu)化。軌對軌輸入運算放大器的優(yōu)化設計在大多數(shù)應用中,操作僅在一個差分對的范圍內(nèi)。然而,有些應用可以

2020-09-25 17:40:49

的軟件包,請參閱數(shù)據(jù)表末尾的訂購附錄。典型特征除非另有說明,否則所有規(guī)格在TA=25°C,VS=5 V,RL=1 kΩ時連接至VS/2。詳細說明概述OPA350系列軌對軌CMOS運算放大器是針對低電壓、單

2020-09-09 16:43:17

運算放大器的絕佳選擇。圖33顯示了OP162的簡化等效示意圖。在設備的輸入端使用PNP差分對。發(fā)射極的交叉連接降低了輸入級的跨導,提高了器件的轉(zhuǎn)換速率。通過交叉連接發(fā)射極來降低跨導還有另一個優(yōu)點,它提供了

2020-09-14 17:09:23

DN221-SOT-23微功率,軌到軌運算放大器,輸入高于正電源

2019-07-30 12:54:03

LV906x 10 MHz,RRIO,CMOS運算放大器德州儀器(TI)的TLV906x是10 MHz,軌到軌輸入和輸出(RRIO),1.8 V至5.5 V運算放大器,可為具有挑戰(zhàn)性的系統(tǒng)提供高性能

2018-08-27 09:34:12

可能會超出邏輯供電軌,很可能會破壞邏輯電路,引起短路后還可能會破壞運算放大器。有三種邏輯電路必須考慮,即ECL、TTL和CMOS——ECL是一種極快的電流導引邏輯系列。基于上述原因,當應用中涉及ECL

2018-10-31 22:32:44

及三家主要模擬器件競爭廠商各獲得了一個雙極性運算放大器和一個CMOS運算放大器。為了進行比較,試驗中還包括歷史悠久的雙通道運算放大器LM358(非軌到軌輸出)和雙通道比較器LM393。使用三個電路,測量

2018-08-08 17:12:17

為什么說單電源運算放大器不能真正實現(xiàn)輸出的軌對軌擺動?單電源運算放大器處于線性工作的輸出范圍是多少?

2021-04-08 07:00:44

LT1677是一款低噪聲軌到軌輸入和輸出運算放大器,工作電壓范圍很寬(3V至±15V)

2020-03-23 09:47:30

DN171- 利用LT1466L微功率軌到軌運算放大器實現(xiàn)最大化動態(tài)范圍

2019-06-25 10:19:12

LTC6246的典型應用 -180MHz,1mA功率高效單軌至軌I / O運算放大器。 LTC6246 / LTC6247 / LTC6248是單/雙/四路低功耗,高速單位增益穩(wěn)定軌到軌輸入/輸出運算放大器

2020-06-04 10:56:14

的軌至軌運算放大器 (op amp) 必須具有一個真正跨越最小失真電源的晶體管設計。在許多應用電路中,這種要求都是沒有商量余地的。

2019-08-20 08:07:29

概述CN958內(nèi)部包括一個運算放大器和一個基準電壓源,適合于2.5V到5.5V單電源工作。CN958內(nèi)部的運算放大器具有頻率補償電路,在單位增益應用時也能保持穩(wěn)定。其輸出級采用特別設計,即使在帶有

2016-03-26 11:41:34

電壓源。ZC951適合于2.5V到5.5V單電源工作。ZC951內(nèi)部的運算放大器具有頻率補償電路,在單位增益應用時也能保持穩(wěn)定。其輸出級采用特別設計,即使在帶有負載時只消耗很少的電流。運算放大器的輸入

2014-02-27 14:38:57

儀表伺服放大器執(zhí)行機構(gòu)驅(qū)動傳感器調(diào)節(jié)器電源控制一般說明軌對軌輸出擺動與直流精度相結(jié)合是OP495四和OP295雙CBCMOS運算放大器的關(guān)鍵特性。通過采用雙極性前端,實現(xiàn)了比CMOS設計更低的噪聲和更高的精度

2020-09-11 17:05:52

LT1678的典型應用 - 雙/四路低噪聲,軌到軌,精密運算放大器。 LT 1678 / LT1679是雙/四路軌到軌運算放大器

2020-06-18 13:00:00

LT1366的典型應用 - 雙精度軌到軌輸入和輸出運算放大器。 LT1366 / LT1367 / LT1368 / LT1369是雙通道和四通道雙極性運算放大器,將軌到軌輸入和輸出操作與精密規(guī)格相結(jié)合

2020-04-03 09:59:24

LT6004的典型應用 - 雙通道1.6V,1 uA精密軌到軌輸入和輸出運算放大器。 LT6003 / LT6004 / LT6005是單/雙/四運放,旨在最大限度地延長便攜式應用的電池壽命和性能

2020-03-11 09:53:41

LT6005的典型應用 - 四路1.6V,1 uA精密軌到軌輸入和輸出運算放大器。 LT6003 / LT6004 / LT6005是單/雙/四運放,旨在最大限度地延長便攜式應用的電池壽命和性能

2020-03-11 09:53:41

LT6002的典型應用 - 四路1.8V,13 uA精密軌到軌運算放大器。 LT 6000 / LT6001 / LT6002是單通道,雙通道和四通道精密軌到軌輸入和輸出運算放大器。該器件旨在最大限度地延長永遠在線應用中的電池壽命,可在低至1.8V的電源下工作,同時僅消耗13uA的靜態(tài)電流

2020-03-10 09:59:36

LT1367的典型應用 - 四路精密軌到軌輸入和輸出運算放大器。 LT1366 / LT1367 / LT1368 / LT1369是雙通道和四通道雙極性運算放大器,將軌到軌輸入和輸出操作與精密規(guī)格相結(jié)合

2020-04-03 09:59:24

概述:LTC6242是一款四通道低噪聲、低失調(diào)、軌至軌輸出、具穩(wěn)定單位增益的 CMOS 運算放大器,它們具有 1pA 的輸入偏置電流。在單通道器件 LTC6240 上,最大輸入偏置電流保證為 1pA。

2021-04-12 08:08:52

描述 運算放大器在信號調(diào)整電路和測量系統(tǒng)中已使用了數(shù)十年。具有從負到正電源軌輸出的運算放大器通常稱為軌至軌輸出 (RRO) 運算放大器。這些器件在便攜式系統(tǒng)中的使用越來越多,用于驅(qū)動模數(shù)轉(zhuǎn)換器

2018-08-02 07:54:38

本文設計了一種用于耳機驅(qū)動的CMOS功率放大器,該放大器采用0.35μm雙層多晶硅工藝實現(xiàn),驅(qū)動32Ω的電阻負載。該設計采用三級放大兩級密勒補償?shù)碾娐方Y(jié)構(gòu),通過提高增益帶寬來提高音頻放大器的性能。

2021-04-23 06:31:27

微調(diào),因為輸入級的失調(diào)電壓匹配十分出色,一般為1至3 mV,失調(diào)溫度系數(shù)為5至15μV/°C。在微調(diào)后,可實現(xiàn)低于20 μV的輸入失調(diào)電壓。采用自穩(wěn)零架構(gòu)的運算放大器可提供低于5 μV的失調(diào)電壓,但我

2021-11-25 07:00:00

請問如何采用集成電荷泵的軌到軌放大器改善輸入偏置精度?

2021-04-20 06:41:35

不符合預測模式,人們必須根據(jù)數(shù)據(jù)手冊進行估算。我們可以使用更簡單的公式 其中,K可從運算放大器數(shù)據(jù)手冊的失真曲線中找到。附加一點,許多運算放大器都是使用軌到軌輸入級。大多數(shù)放大器通過兩個獨立的輸入級都能實現(xiàn)此

2020-04-17 07:00:00

。暫時偏離到放大器電源軌之外會有損壞輸入的風險,而暫時飽和或壓擺受限會有造成輸出失真的風險。任何一種狀況都可能導致負反饋暫時丟失和不可預測的瞬態(tài)行為,甚至可能因為某些運算放大器架構(gòu)中的相位反轉(zhuǎn)而閂鎖

2021-09-13 09:25:33

描述運算放大器在信號調(diào)整電路和測量系統(tǒng)中已使用了數(shù)十年。具有從負到正電源軌輸出的運算放大器通常稱為軌至軌輸出 (RRO) 運算放大器。這些器件在便攜式系統(tǒng)中的使用越來越多,用于驅(qū)動模數(shù)轉(zhuǎn)換器

2022-09-14 09:39:34

V范圍內(nèi)時,將其用作比較器有時是可行的,特別是如果增加一些正遲滯來避免振蕩并加快不確定區(qū)域的過渡。但隨著軌到軌輸出運算放大器的出現(xiàn),問題開始變得嚴重。參考文獻(1)對輸入和輸出級做了很好的闡釋。歷史

2019-10-12 07:00:00

放大器可在更大溫度范圍內(nèi)提供最低漂移,但其內(nèi)部結(jié)構(gòu)可對其使用帶來一定限制。另一種方法是選擇一款經(jīng)過精確微調(diào)的器件。如欲進一步了解這種良好微調(diào)運算放大器的效果,敬請查看最新發(fā)布的 OPA192。該器件

2018-09-13 10:08:21

為了讓IoT里不可缺少的傳感器器件更加省電,新日本無線特別推出了軌到軌輸入輸出運算放大器NJU77552。此運算放大器有1.7MHz帶寬、1回路50μA的超低消耗電流、高EMI抑制性能等特點,并且已經(jīng)進入量產(chǎn)階段。

2020-08-03 07:49:16

拓撲,支持放大接近V–軌的信號。類似地,有些應用要求運放能在V–到V+的輸入范圍內(nèi)保持高精度。這稱為軌到軌輸入(RRI)運算放大器,此類運放通常有兩個差分對,一個軌一對。ADA4661是RRI運放的經(jīng)典

2018-10-30 14:47:30

求一種低壓低功耗CMOS電流反饋運算放大器設計方案

2021-04-25 08:27:09

本文設計的帶共模反饋的兩級高增益運算放大器結(jié)構(gòu)分兩級,第一級為套筒式運算放大器,用以達到高增益的目的;第二級采用共源級電路結(jié)構(gòu),以增大輸出擺幅。另外還引入了共模反饋以提高共模抑制比。

2021-04-14 06:55:14

本文設計的帶共模反饋的兩級高增益運算放大器結(jié)構(gòu)分兩級,第一級為套筒式運算放大器,用以達到高增益的目的;第二級采用共源級電路結(jié)構(gòu),以增大輸出擺幅。另外還引入了共模反饋以提高共模抑制比。該方案不僅

2021-04-22 06:08:31

MS8117S/MS8127是瑞盟科技的一款單/雙通道運算放大器,具有低功耗,軌到軌輸入輸出,低的輸入失調(diào)電壓和低的電流噪聲。具體表現(xiàn)在可工作在幅度為1.8V到5V的單電源或者雙電源條件,低功耗

2021-11-30 11:03:28

參考運放的datasheet。但如果是兩級運算放大器電路呢,此時總的建立時間又該如何估算?同樣以ADA4897組成兩級運算放大電路為例說明,級聯(lián)后總的0.01%建立時間該是多少?可能的答案:(1)總

2018-11-13 15:08:15

時間可以參考運放的datasheet。

但如果是兩級運算放大器電路呢,此時總的建立時間又該如何估算?

同樣以ADA4897組成兩級運算放大電路為例說明,級聯(lián)后總的0.01%建立時間該是多少?

可能

2023-11-27 06:54:56

怎么一種可編程寬帶運算放大器?如何實現(xiàn)可編程寬帶運算放大器的軟件設計?

2021-04-21 06:15:27

本文設計了一種在12位精度、80MHz采樣率的ADC中負責采樣保持的核心電路—運算跨導放大器 (OTA)。

2021-04-14 06:06:56

CMOS運算放大器結(jié)構(gòu)具有哪些特點?如何去設計CMOS運算放大器?怎樣對CMOS運算放大器進行仿真測試?

2021-04-21 07:21:39

%包括芯片上精密電阻,提供固定增益,誤差低至+/-0.35%一種精密的運算放大器具有低失調(diào)電壓和低失調(diào)過溫漂移。精度通過采用自動調(diào)零技術(shù)來實現(xiàn),這種技術(shù)中,次級放大器抵消主放大器的偏移。結(jié)果是大幅減少

2018-10-22 08:57:48

軌運放最大輸入電流限制?3-2 有的沒有最大輸入電流限制4-運算放大器的軌到軌什么意思運放的軌至軌輸入是指運放的輸入端信號電壓能夠達到電源的兩個軌,并保持不失真,如上例...

2022-01-13 08:15:29

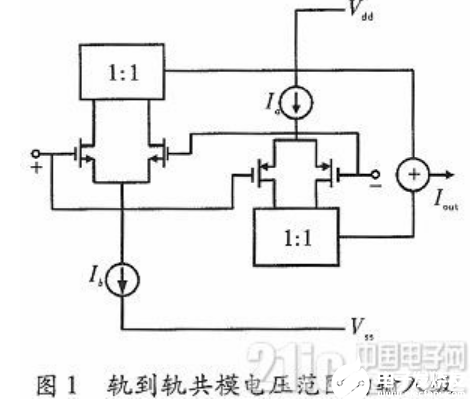

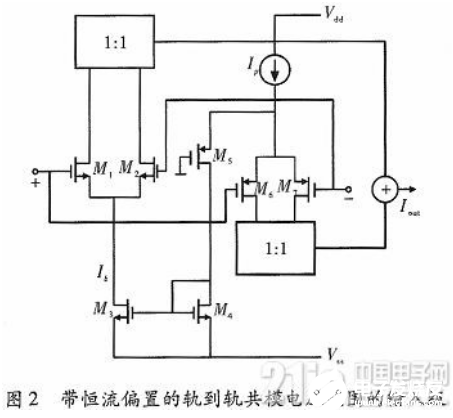

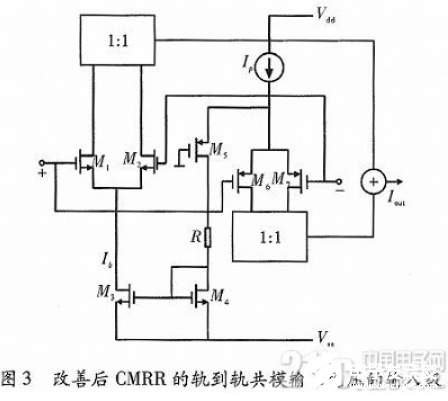

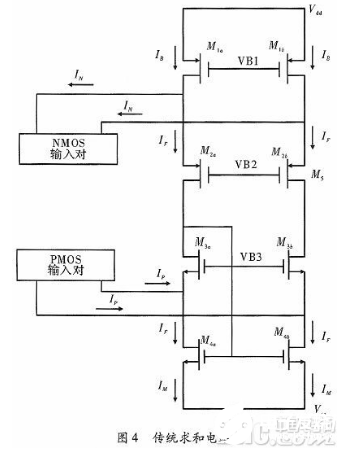

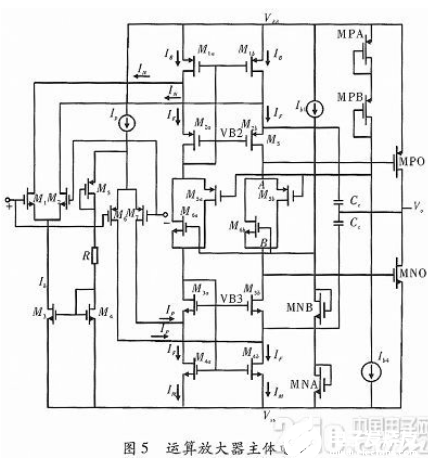

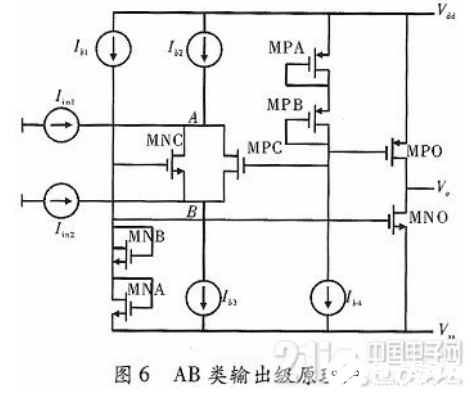

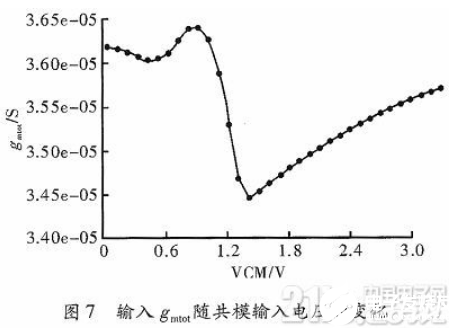

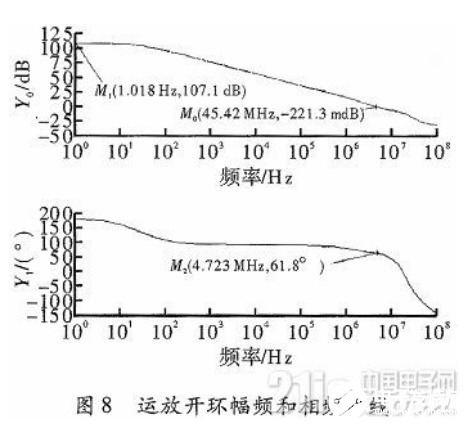

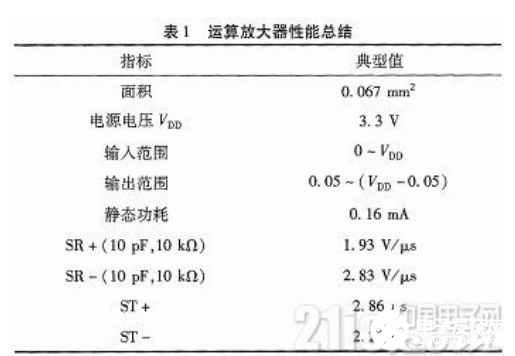

對軌輸入/輸出運算放大器.不同于傳統(tǒng)的實現(xiàn)恒定跨導的技術(shù),在電路設計實現(xiàn)上通過一個簡單的檢測電路,使互補差分對在整個共模輸入電壓變化范圍內(nèi)交替工作,實現(xiàn)了跨導恒定.同時為了得到較高的轉(zhuǎn)換速率,加入了轉(zhuǎn)換

2010-04-22 11:34:49

消費電子等諸多領(lǐng)域。替代型號選型表:型號封裝描述兼容型號 MS8051/SSOP8/ SOT23-5250MHz、軌到軌輸出CMOS運算放大器 AD8051 MS8052/MSOP8

2021-06-04 10:15:36

CMOS兩級運算放大器調(diào)零電路性能分析

運算放大器的高速性能主要靠兩個重要的參數(shù)來衡量,即大信號響應時間和小信號響應時間。大信號響應時間由擺率決定,小信號

2009-10-30 11:59:48 4520

4520 CMOS運算放大器的基本分類1、單級差分運算放大器(電流鏡做負載的差分放大器)2、套筒式共源共柵CMOS運算放大器(單級)3、折疊共源共柵CMOS運算放大器(單級)4、兩級CMOS運算放大器

5、Rail-to-Rail CMOS運算放大器6、Chopper CMOS運算放大器 運放的概念、組成與電路結(jié)構(gòu)

2018-11-07 10:10:57 89

89

電子發(fā)燒友App

電子發(fā)燒友App

評論