本應用筆記描述了采樣時鐘抖動(時間間隔誤差或“TIE抖動”)如何影響Δ數模轉換器(DAC)的性能。新的見解解釋了在這些器件中分別指定低頻(< 2x 通帶頻率)和高頻或寬帶(> 2x 通帶頻率)抖動容限的重要性。本文還提供了一個簡單的高度抖動周期跳躍采樣時鐘的應用示例,并描述了一種生成適當寬帶抖動時鐘的方法。然后,本文將Maxim的音頻DAC抖動容限與競爭對手的音頻DAC進行比較。Maxim具有極高的抖動容限,可實現非常簡單、低成本的采樣時鐘實現。

高性能音頻數模轉換器(DAC)傳統上需要一個非常干凈的采樣主時鐘(MCLK),以避免音頻質量下降。時鐘源通常直接來自晶體振蕩器,其產生的抖動通常小于100ps。在某些系統中,音頻過采樣頻率(通常是3.072MHz或2.8224MHz的倍數)不是晶體振蕩器參考頻率的方便部分。雖然這些系統可以實現小數N分頻PLL來創建所需的音頻MCLK頻率,但這種基于PLL的頻率基準通常具有多個參考頻率雜散和大量的低頻抖動。此外,這些基于PLL的頻率基準通常無法在不超過所需引腳數、面積或功耗目標的情況下使抖動足夠低。然而,有一個解決這一困境的辦法。可以容忍高抖動的音頻DAC允許在此類系統中使用更簡單的采樣時鐘基準。

了解抖動容限

高抖動容限很重要,因為它:

在存在抖動的情況下最大限度地提高音頻信號質量

通過使用更簡單的抖動時鐘源降低系統復雜性或物料清單 (BOM)

無需高頻 MCLK,從而降低功耗和電磁干擾 (EMI)

目前沒有評估抖動容限的標準方法。音頻精度 2700 (AP2700) 音頻分析儀可以產生時鐘抖動,但它產生的大部分是低頻抖動(主要低于奈奎斯特音頻采樣率),如圖 1 所示。

圖1.AP5 產生的 2700ns “寬帶”抖動頻譜。

抖動容限測試設置

使用兩個不同的抖動時鐘源來比較多個DAC的抖動靈敏度。第一個抖動時鐘是來自12MHz基準的288.25MHz周期跳躍時鐘。這在11kHz以上產生~40ns的抖動,在0kHz以下產生~37.40ns的抖動。該 時鐘 是 使用 NI PXI-5421? 100MHz 任意 波形 發生 器 (ARB) 創建 的, 該 發生 器 提供 所需 的 時鐘 模式。

第二個抖動時鐘是使用相同的ARB創建的寬帶白色抖動時鐘。ARB產生一個6.144MHz的正弦波,并增加白噪聲,然后通過MAX999比較器饋送,產生具有大量寬帶抖動的方波時鐘。

使用LeCroy WaveRunner? 104MXI-A 1GHz示波器使用時間間隔誤差(TIE)抖動測量來測量抖動。上升沿和下降沿在兩個測試文件中都會抖動。

為此評估創建的寬帶抖動時鐘具有真正的寬帶(白色)抖動頻譜,適用于評估對寬帶抖動的靈敏度。參見圖 2、3 和 4。這種真正的白色抖動頻譜不太可能在實際應用中找到;但是,這是一個很好的抖動容限測試,因為它將揭示任何特定頻率范圍內的抖動敏感性。

圖2.用于此分析的寬帶 5.9ns RMS 白抖動頻譜。

圖3.5.9ns寬帶抖動直方圖。

圖4.示波器捕獲3.072MHz時鐘,具有5.9ns寬帶白抖動。

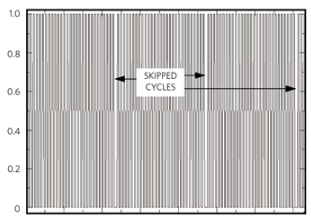

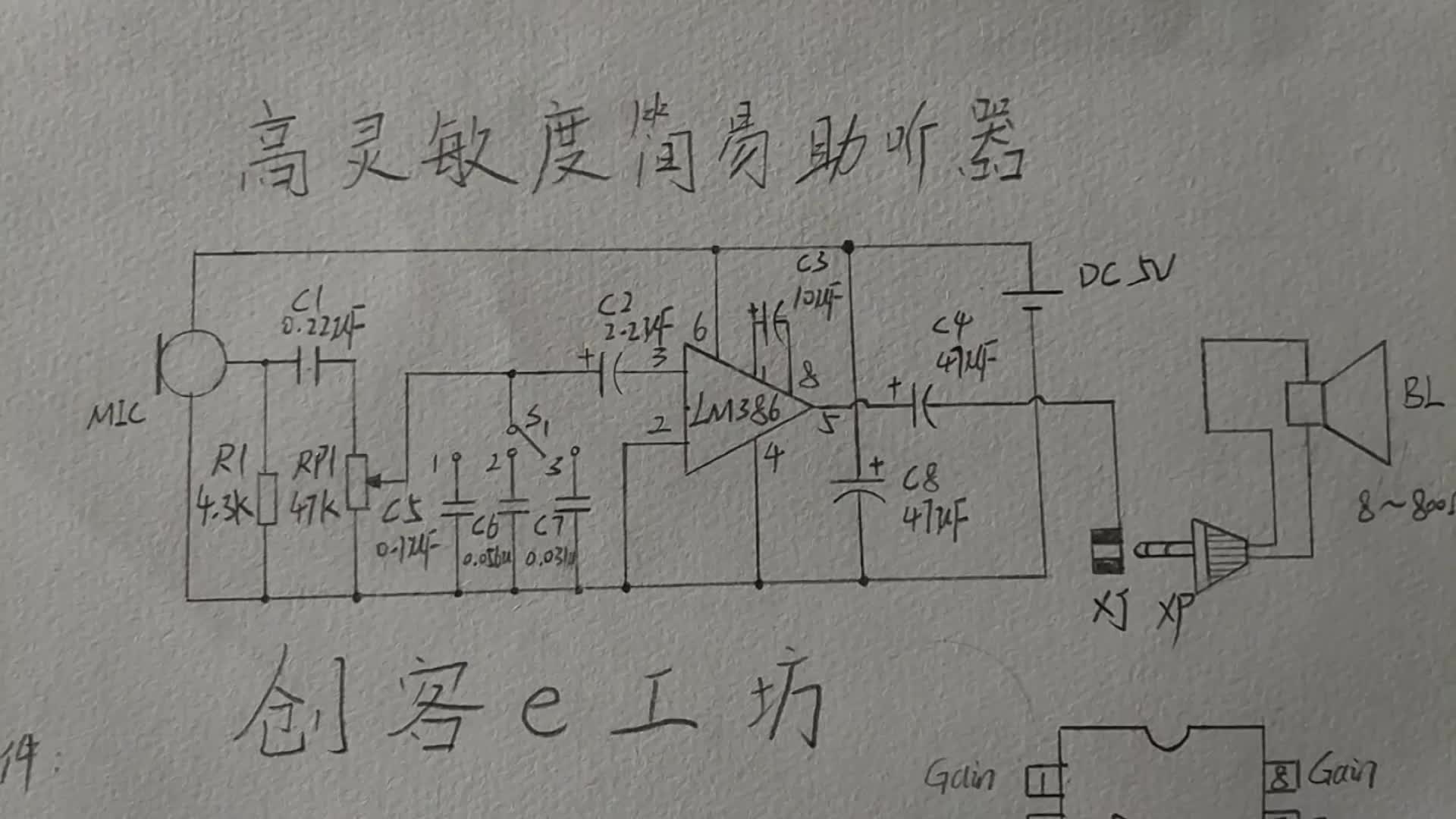

本研究使用的跳周期時鐘如圖5所示,該時鐘的抖動頻譜如圖6和圖7所示。該周期跳躍時鐘測試表明,DAC可以容忍非常容易生成、極其抖動的時鐘,而無需PLL。只需少量邏輯即可跳過任何頻率基準的時鐘周期,以生成任何(較低頻率)采樣時鐘。這種類型的時鐘生成不需要濾波或反饋環路。

圖5.12.288MHz MCLK與周期跳躍的25MHz時鐘的瞬態圖。

圖6.從12MHz參考時鐘周期跳過的288.25MHz MCLK抖動頻譜。

圖7.周期跳躍時鐘的低頻抖動頻譜。

Maxim的幾個器件,包括音頻編解碼器(MAX98089和MAX98096)和MAX98355/MAX98356功率放大器,都受益于高抖動容限DAC。 這些器件的額定值可在 0 至 5kHz 頻段內承受高達 0.40ns 的抖動,在 12kHz 頻段上可承受 40ns 的抖動。有了這個抖動量,這些器件將顯示以下抖動引起的性能限制(不包括電路噪聲):

-108dB THD+N,1kHz 滿量程音調

-96.5dB THD+N,6kHz滿量程音調

-87dB THD+N,20kHz 滿量程音調

105dB 動態范圍和信噪比 (SNR)

THD+N性能結果僅受低頻抖動(<40kHz)的影響。而動態范圍和信噪比僅受高頻抖動(> 40kHz)的影響。

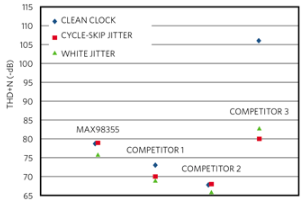

圖8、9、10和11顯示了Maxim MAX98355功率放大器使用高抖動時鐘源測量的音頻性能與一組競爭DAC的比較。除競爭對手 2 外,所有這些競爭部件都聲稱它們對時鐘抖動不敏感,但沒有提供抖動容限規格。

抖動容限測試結果

圖8.動態范圍下降,11.5ns RMS周期跳躍時鐘抖動。

注意,MAX98355的動態范圍不會隨著周期跳躍的抖動時鐘而降低。因此,MAX98355在時鐘抖動時的性能比“120dB DAC”高出20dB以上。

圖9.寬帶白抖動導致動態范圍下降。

競爭對手 3 的 5.5ns 和 9.3ns 抖動性能以及競爭對手 5 的 9.2ns 抖動性能是外推的,因為該器件在這些抖動電平下實際上無法正常工作;它們開始下降位,實際測量的動態范圍低于該圖所示。

圖 10.1kHz THD+N 性能隨時鐘抖動而下降。

圖 11.20kHz THD+N 性能隨時鐘抖動而下降。

結論

本應用筆記介紹了一種測試音頻DAC抖動容限的方法。音頻DAC對低頻和高頻頻段抖動的響應不同,因此有助于分別指定抖動頻譜這兩個頻段的容差。容忍高抖動的DAC允許更簡單的采樣時鐘實現,而不會降低音頻質量。

審核編輯:郭婷

電子發燒友App

電子發燒友App

評論