在Allegro 16.6中默認是2層板的,那怎樣設置單層板呢?

2012-12-20 09:37:24

安裝完Allegro后,Allegro可以正常使用,但capture無法打開,提示This application has quit unexpectedly,重裝了好幾次,都不行,求助大神

2016-03-09 15:21:21

Allegro中建立異形焊盤Allegro中可以建立異形焊盤.異形PAD是通過畫Shape來實現的.在PADS中建立異形PAD,需要借助一個PAD和Shape相結合(Associate),即可建立

2019-01-19 11:24:13

Cadence、OrCAD、Capture的結合,為當前高速、高密度、多層的復雜 PCB 設計布線提供了最完美解決方案。Allegro擁有完善的Constraint設定,用戶只須按要求設定好布線規則,在

2019-04-28 17:24:42

也使用。采用花形,是因為金屬化中工藝的要求。在allegro里又叫Flash Pad,是指過孔或元件引腳與銅箔的一種連接方式。其目的有幾個,一是為了避免由于元件引腳與大面積銅箔直接相連,而使焊接

2011-11-24 16:35:22

小弟是PCB制版新手,剛開始自學 Cadence沒有多久。我用的是Cadence 16.3. 用Orcad Capture CIS 制作原理圖。練習時,從朋友那拷來了15.7版本的原理圖,然后自己在

2010-06-17 03:43:50

allegro16_5中文教程

2014-07-06 15:07:59

allegro中analysis菜單下使用workflow manager,點擊start analysis后顯示implement analysis failed或者coupling analysis failed?

2022-03-07 22:02:42

pad、anti pad三種,那么當我導入網表之后(原理圖中定義了該引腳和哪層相連),是不是由allegro自動決定,我的這個元件的引腳與地層相連還是與電源層相連,而相連的那層用的就是themal

2012-05-02 13:33:50

怎樣在allegro16.5中查看沒有定義的焊盤是否被添加了信號?如何避免?急急急!

2016-08-19 19:14:11

求助各位大神,capture原理圖(dsn)怎么導入altuim 9中,在altuim 9中使用 File→import wizard,next→然后選擇 orcad ,再選擇**.DSN文件,再就報錯啦{:4:}大家有沒有高招,在線等.....{:13:}

2012-12-13 17:27:17

介紹在ALLEGRO中如何加入中文,這種方法也可以在ALLEGRO PSD中使用。<br/></p><p>&

2009-10-30 11:43:59

忽略掉這些,不用管這些錯誤,直接點擊OK按鈕即可; Xnet是什么含義,如何在Allegro軟件中添加Xnet? 圖5-113 SI Design Audit示意圖 第三步,在PCB界面

2020-09-07 17:57:50

程序功能:在allegro中實現陰字體。 通常情況下,我們只能在allegro中添加陽字體文字。在某些特殊的場合,我們希望能夠在板上的銅皮或者絲印中增加陰字體文字。在allegro本身沒有提供該功能

2019-07-02 21:42:39

大家好。請教個問題呢。在allegro中怎么畫 彈簧天線的封裝

2015-01-28 11:50:39

對話框,如圖1。圖1在對話框中確定User Units選擇Mils,阿Accuracy選擇0,其他根據你的尺寸自行定義。設置完成選擇OK按鈕,使配置生效。◆設置動態鋪銅參數。在Allegro中打開

2012-03-29 22:48:20

在allegro軟件中插入公司LOGO的方法,有附件。

2015-07-13 17:51:55

在AD14中如何在重新定義板子形狀時畫出圓形的板子,求高手解答

2015-08-17 10:36:16

的摸索,找到一些實現的曲線實現方法。我用Altium Designer 6.6,下面以6.6為例講講如何將Allegro的brd板子導入Protel (DXP)中。

2019-07-23 07:00:19

如何在BIM中添加pin的驅動,因為ImgB沒有OAD功能,希望在ImgB不能正常工作時,也能夠在boot的時候通過引腳電平去選擇從ImgA啟動,但是我想加入PIN.h和CC26XXPIN.C的時候提示各種錯誤,我把其他工程中的路徑包含和宏定義都加上也不行,請問是還缺少什么?

2016-03-31 16:52:33

請教個問題,在 CCG5代碼中怎么實現DR_SWAP?我們配置了端口 0 作為源對外充電,但是我們希望 PORT0 做了 UFP。我們是這樣寫的代碼:案例 APP_EVT_PD_合同談判_完成

2024-02-26 06:27:15

教大家一個如何在頭文件中定義全局變量的方法 通常情況下,都是在C文件中定義全局變量,在頭文件中聲明,但是,如果我們定義的全局變量需要被很多的C文件使用的話,那么將全局變量定義在頭文件里面會方便

2018-07-04 08:34:47

教大家一個如何在頭文件中定義全局變量的方法 通常情況下,都是在C文件中定義全局變量,在頭文件中聲明,但是,如果我們定義的全局變量需要被很多的C文件使用的話,那么將全局變量定義在頭文件里面會方便

2018-07-09 09:25:50

allegro 16.2中文教程,英文圖文說明,并附有中文注釋,有allegro基礎的都能看懂。點擊下載

2019-04-28 16:13:25

步可以完成在Altium Designer中打開ALLEGRO的brd文件,也可以用來提取ALLEGRO的封裝(不過AD畫封裝已經夠容易了,估計不會有人需要這么做吧),通過手動元件恢復,可以重建

2014-12-03 15:05:29

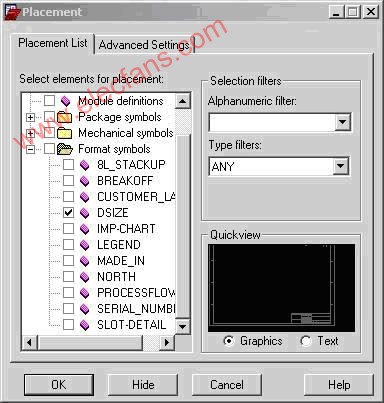

OrACD capture cis 使用中問題:通過CIS網絡抓取功能獲得元器件老出錯:如圖所示,老提示 cannotplace part outside of Capture CISq求大神指教啊!!!

2014-05-04 16:03:28

。通過這一功能我們可以直接將Protel的原理圖轉化到Capture CIS中。 注意事項: 1) Protel DXP在輸出Capture DSN文件的時候,沒有輸出封裝信息,在Capture中

2018-09-17 17:14:49

PCB設計軟件allegro藍牙音箱案例實操講解,以藍牙音箱為案例將PCB設計基礎知識融進實際案例中,通過操作過程講解PCB設計軟件功能及實用經驗技巧,本文著重講解結構性器件的定位的相關內容。本期

2018-08-15 10:10:36

開啟這項功能而已.在Cadence 16.5中的capture開始交互式布局方法為在Capture中設置'option'-->'preferences'-->'miscellaneous

2012-04-19 22:11:11

問:Allegro中如何合并銅皮(Merge Shapes)答:在Allegro中,Shape不僅可以是走線,還可以是各種其他屬性,例如Silkscreen,Place Bound,Solder

2014-11-12 17:49:12

一致的,本文以BeamRF中的開窗設計為例。其實在Allegro中設計開窗的方法非常簡單,總的來說就是在Board Geometry下的Soldermask Top或者Soldermask Bottom

2019-08-07 04:00:00

`我需要的是直接在allegro中修改的方法,不要導出,因為沒有CAD那些其他的軟件。點擊setup-outlines-board outline后彈出下面這個對話框求各位大大們幫忙一下,我是新手~謝謝了`

2017-11-13 14:46:11

ALLEGRO快速換層技巧-----博勵pcb培訓整理打開env文件在EVN文件里增加如下命令funckey 1 'pop bbdrill;pop swap;subclass top'funckey

2019-02-15 03:24:30

in drill legends,and there could be problems elsewhere as well.內容是Drill/Slot symbol需設定,而手工制作焊盤時不設定這個參數也不會報錯。請教如何在LP中設置Drill/Slot symbol或不定義這個參數。萬分感謝!

2014-07-17 11:29:28

V853開發板購買鏈接:https://www.hqchip.com/p/KFB-V853.htmlswap功能簡介1、概念介紹swap:系統內存緊張時進行的內存回收操作。swap分區:在swap

2022-07-18 09:36:09

的 Constraint 設定,用戶只須按要求設定好布線規則,在布線時不違反 DRC 就可以達到布線的設計要求,從而節約了煩瑣的人工檢查時間,提高了工作效率!更能夠定義最小線寬或線長等參數以符合當今高速電路板布線的種種需求。本資料詳細劃分了allegro的每個功能對應的教程,看完必定會有所收獲。

2019-01-15 14:01:00

PSpice菜單中,配置文件名稱顯示在PSpice配置文件中。 2.更加簡潔的工作區 OrCAD Capture為您提供了大量易于使用的工具和功能,便于您的原理圖設計。從17.4版本開始,工作區

2020-07-06 14:49:39

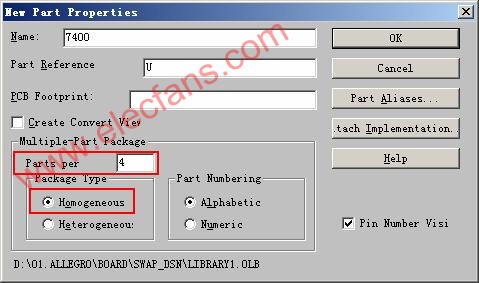

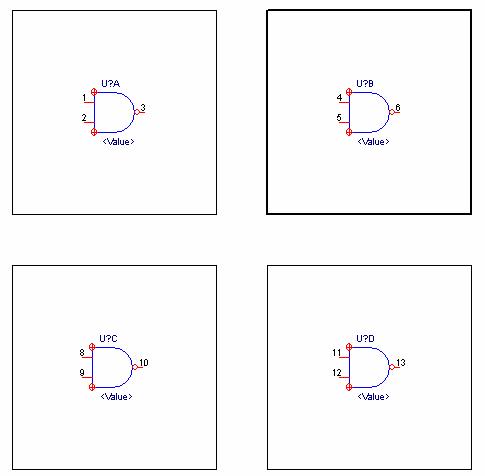

點查找了相關的帖子后找到解決方法,小結步驟如下: 1. 首先確認orcad中value值被設置 2. 在Allegro中建立元件庫(Package symbol)時,需要添加Ref,其中最常用的2個

2011-06-23 15:08:09

怎么直接在allegro PCB環境下直接給一個無網絡的pin賦予網絡(不通過原理圖)我已經在 PCBeditor已經創建了網絡了,但是不知道怎么賦予這個pi 你們誰知道?

2019-06-25 22:49:36

1. 前言什麼是 SKILL?SKILL 是一種程式語言。是Cadence 開放給使用者可以藉由SKILL 取得Allegro中的資料並做一些客製化的程式

2011-01-11 10:36:56

allegro中這個怎么樣添加模型?

2019-08-01 05:35:21

allegro中 要修改 絲印編號 比如從pcb01改成pcb02怎么修改呀還是只能再次重新添加

2019-09-09 05:35:31

嗨? 如何在HLS 14.3中編寫pow功能? HLS 14.3不支持exp和pow功能。我在我的代碼中寫了“#include math.h”。但是,它不起作用。 另外,我想知道C代碼中

2019-03-05 13:40:09

如何在IAR for ARM中定義常量或數組到flash而不是RAM中?const,__flash關鍵字都不行,網上說加一個編譯開關,也沒有,如何實現想請教,謝謝!已經得到解決,是我看錯了地址區間,實際上const定義就行。

2022-12-09 16:17:13

如何在IAR中實現printf函數功能?

2021-12-01 06:29:17

如何在Keil ARM MDK中實現延遲功能,等待給定時間(以微秒為單位),可以重新編譯為Keil項目設置中定義的任何合理時鐘速度?所有這一切都沒有使用計時器。

2018-08-22 10:29:23

我使用相同的示例代碼來捕獲句點。在調試模式下,我正在讀取表達式 - 數據,我能夠在那里看到十六進制值你能幫我理解嗎,如何將這個十六進制值與輸入引腳上的頻率聯系起來和如何在 PPG bean 中配置

2023-03-20 07:38:51

如何在PSOC4中覆蓋PrtTf?重寫RealTest.c中的PrtTf函數,但仍在“y-siNIT”ARM LIB函數調用中崩潰。如何在PSoC4編譯中跳過(或重寫)?目標是從PrtTF到RealTest.c中定義的FPTCCF函數。附上項目供參考。Cyrjj.CaseV02.Zip的設計176.4 K

2019-09-25 14:08:37

。我定義了兩個屏幕:一,二。兩個屏幕都包含容器“Selection1”這個過程工作正常。問題:如何在 ScreenOneView::setupScreen() 函數中設置容器中按鈕的顏色?我已經嘗試了一切,只是找不到解決方案。

2023-02-02 06:20:02

在FPGA中,動態相位調整(DPA)主要是實現LVDS接口接收時對時鐘和數據通道的相位補償,以達到正確接收的目的。那么該如何在低端FPGA中實現DPA的功能呢?

2021-04-08 06:47:08

請問如何在函數中命名引腳,如[C] 純文本查看 復制代碼//兩個函數在同一個程序中。以下為示例需求***it P1_1= P1^1; void test(){P1_1= P1^2;}void

2019-07-10 04:12:56

我如何在啟動文件中調用定義為 uint32_t getValue(void) 的 C 函數(在 Reset_Handler 例程中)?需要什么語法?我嘗試導入它并將其設置為 extern(其他標準

2022-12-09 07:27:54

使用BLE共享內存引導加載程序我試圖定義用于在應用程序的配置數據bootloadable一塊閃光。但這不應該由一個引導閃存操作的影響。所以我想塊應在bootloader程序定義。我做了以下工作:在

2019-09-06 12:57:34

我在C中編寫代碼,但需要與包含文件通信。如何在源代碼中包含包含文件的定義?我必須創建一個頭文件,它反映了包含文件嗎?如果是,有沒有辦法將頭文件與包含文件合并?,或者可能從包含文件生成頭文件?

2019-09-17 11:51:07

對于virtex7系列FPGA,如何在用戶代碼中定義“Startup”元素?我在哪里可以找到有關其用法的具體文檔?謝謝!

2020-07-25 11:17:37

,如何實現linux中支持的swap功能的呢?1,嵌入式linux隨產品發布時,運行的邏輯往往是在設計之初就確定了。因而在選擇內存大小時,避免了可用內存的不足的問題。因而不會出現swap現象和需求...

2021-11-05 07:05:22

allegro中怎么制作Mark點,有沒有教程文檔之類的資料,在百度上找了,都沒有找到制作教程

2019-08-27 05:30:54

在allegro中,請問怎么給一個過孔賦予網絡?多謝解答!

2019-08-26 05:35:41

allegro中機械孔怎么制作的,有沒有制作教程,新手不懂,求指教

2019-08-29 02:36:37

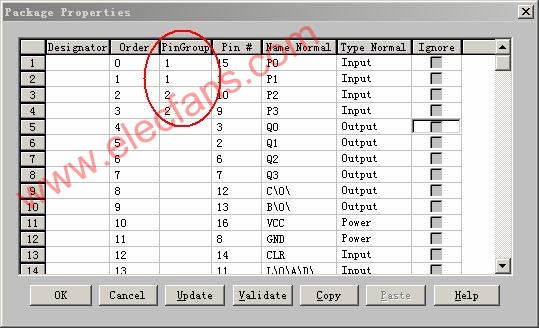

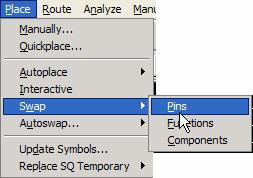

我在PCB editor中swap了pin,怎么成長orcad中back annotate時使用的.SWP文件?

2011-12-18 11:26:04

更換了一次計算機域,計算機名字,然后重新更新了allegro破解licence之后,在allegro中鼠標滾輪的縮放功能就沒有了。鼠標沒壞,在其他軟件里面縮放功能都沒問題。查看了env,對比同事的也沒有問題。網上也沒有解決方法,求大神指點。

2018-08-22 11:56:30

/Capture CIS(含有元件庫管理之功能),原理圖仿真工具PSpice(PSpiceAD、PSpiceAA),PCB Layout工具 OrCAD PCB Editor(Allegro L版本

2012-07-08 22:59:53

功能我們可以直接將Protel的原理圖轉化到Capture CIS中。 這里,我們僅提出幾點通過實踐總結出來的注意事項。 1) Protel DXP在輸出Capture DSN文件的時候,沒有輸出

2018-11-22 15:47:00

Capture生成的Allegro格式的網表傳遞到Allegro BRD中,作為我們重現工作的起點; 2) 首先,我們要重現器件布局。在Protel中輸出Place & Pick文件,這個文件

2014-12-03 15:20:51

在allegro中怎么把整個模塊旋轉

2019-04-26 07:35:24

想要使用data capture功能,但是下載下來的文件夾(見附件)中沒有data_capture.bat這個文件。點擊其他文件顯示找不到系統路徑。請問data capture功能怎么使用?附件DataCapture.zip40.3 KB

2018-10-23 09:29:28

大家好!請問如何在RT-Thread studio的debug和release模式中設置各自的宏定義,我在debug模式下設置了一個DEBUG的宏定義,發現它在release模式下也起作用。切換

2022-07-26 11:15:21

如何在Allegro增加零件及修改連線關系 步驟: 1. 設定環境變數: 使用這項功能前必先啟動Logic_edit_enabled環境變數. 在Allegro選擇下拉式菜單

2009-09-06 11:07:31 0

0 Allegro中網絡表的導入以及回編到Capture中的一些注意事項:網絡表(Netlist)是溝通電路原理圖和Layout實際板子的橋梁網絡表包含的內容有零件Pin的連接線關系以及零件的包裝等基本

2009-09-20 18:08:08 0

0 What is the Capture to Allegro interface?Before the 9.2.1 release, Capture used the third party

2010-04-05 06:21:28 0

0 如何在Allegro中執行SKILL-由下拉菜單執行指令:如何在 Allegro 中執行SKILL(2)-由下拉選單執行指令1. 前言在之前我們已經介紹過如何載入以及執行 SKILL,接下

2010-04-25 10:06:53 0

0 Best practices for preparing a library for Capture-Allegro PCB Editorflow Limit part and pi

2006-04-16 20:47:17 665

665 PCB抄板之PROTEL到ALLEGRO的轉換技術1

1. PROTEL 原理圖到Cadence Design Systems, Inc. Capture CIS

在Protel原理圖的轉化上我們可以利用Protel DXP SP2的新功能來實現。通過

2010-02-02 10:42:53 1435

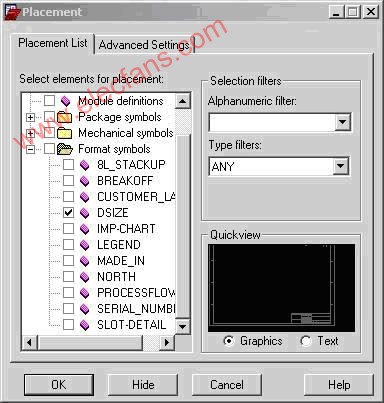

1435 一、創建圖紙外框Allegro提供專門的創建圖紙外框功能,并把它視為一種的Symbol,稱為Format Symbol。 方法:在Fil

2010-06-24 10:29:05 2936

2936

本章的主要內容介紹Allegro 如何載入Netlist,進而認識新式轉法和舊式轉法有何不同及優缺點的分析,通過本章學習可以對Allegro 和Capture 之間的互動關係,同時也能體驗出Allegro 和Captur

2011-11-24 11:37:21 0

0 allegro常用功能介紹

2022-01-10 11:53:15 0

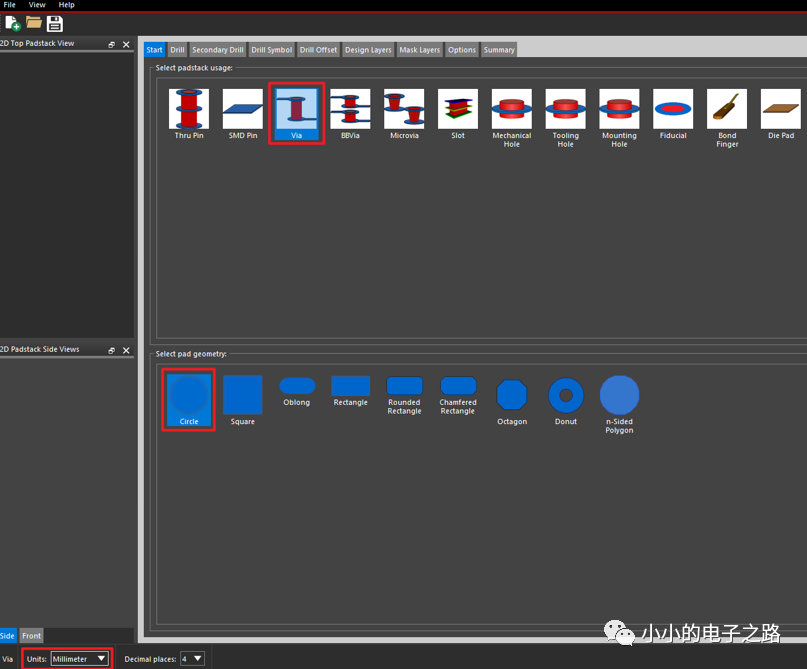

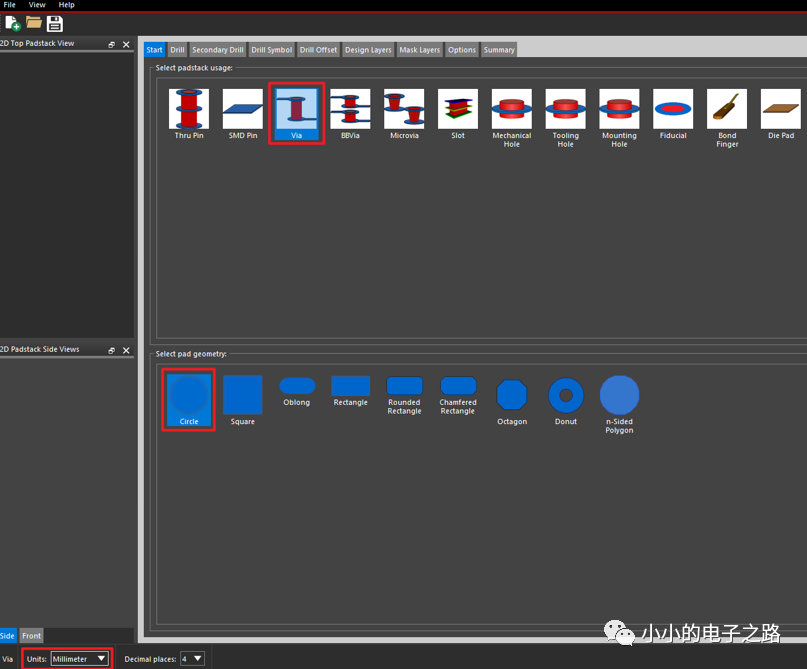

0 過孔也是PCB中最常見的孔之一,它用于連接雙面板和多層板中各層之間的走線。下面就來簡單介紹一下如何在Cadence Allegro軟件中制作過孔。

2023-10-21 14:07:25 1287

1287

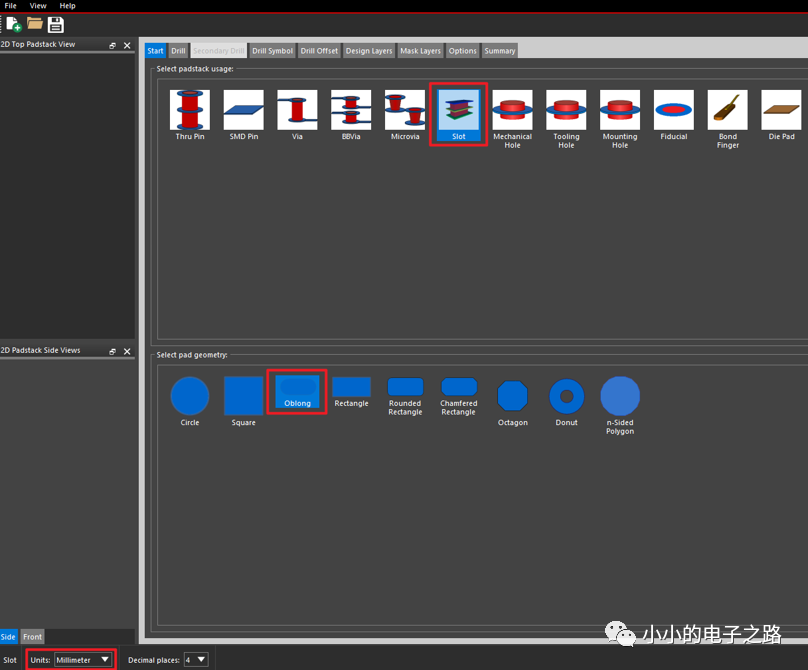

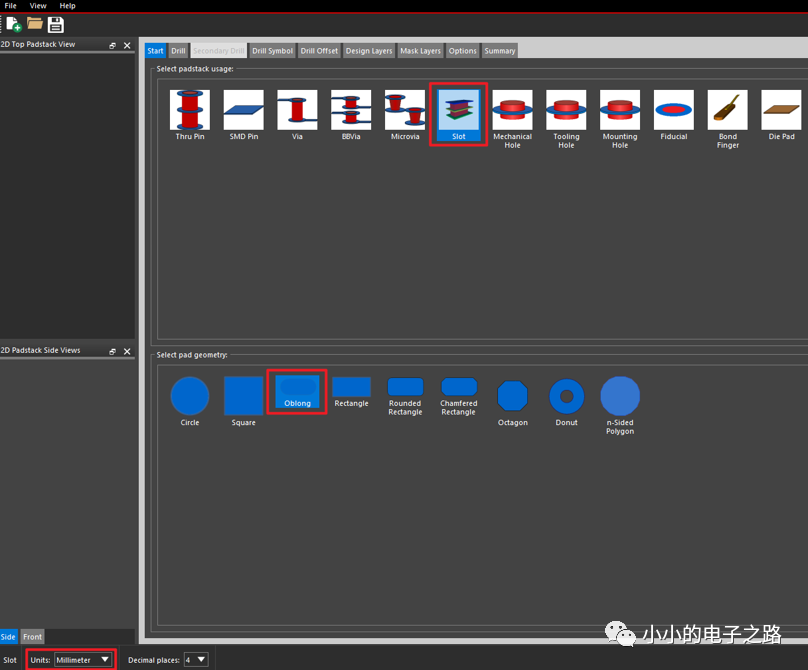

槽孔是指鉆孔形狀不是圓形的通孔,某些體積較大的開關的封裝會采用槽孔。下面就來簡單介紹一下如何在Cadence Allegro軟件中制作槽孔焊盤。

2023-10-21 14:08:29 621

621

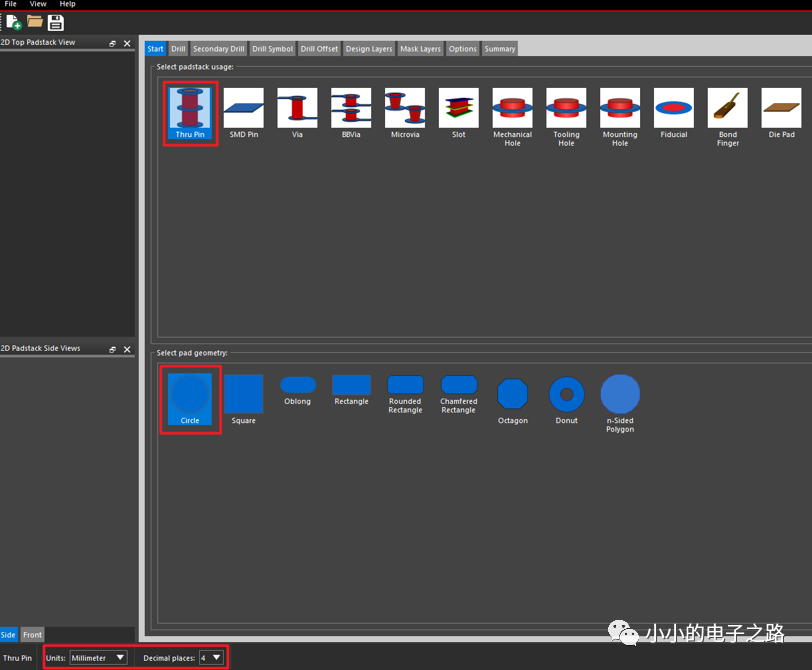

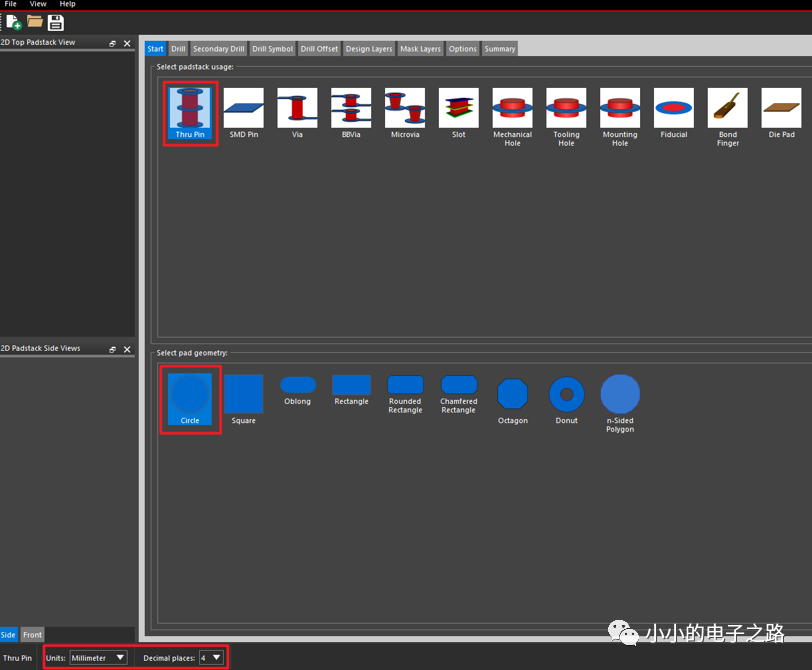

通孔焊盤可以說是PCB中最常見的焊盤之一了,對于插針等插件元器件的焊接,其采用的焊盤大都是通孔焊盤。下面就來簡單介紹一下如何在Cadence Allegro軟件中制作通孔焊盤。

2023-10-21 14:10:59 1189

1189

?

? ?

?

?

? 電子發燒友App

電子發燒友App

評論