CPLD_LED測試

2012-08-10 18:52:58

還算不上是復(fù)雜系統(tǒng),總共采用了8 塊IC,一個(gè)實(shí)現(xiàn)特定功能的系統(tǒng)往往更復(fù)雜,需要采用的IC 會(huì)更多。能不能把這些分離的器件用CPLD 來實(shí)現(xiàn)呢?答案是肯定的。 三、單片機(jī)與CPLD接口設(shè)計(jì) 以上經(jīng)典電路

2012-01-17 16:48:45

和CPLD相連接,作為I/O擴(kuò)展,再把CPLD和LCD彩色屏相連接,此時(shí)CPLD也需要用VHDL語言編程。這個(gè)板子運(yùn)行正常。但是現(xiàn)在要換一個(gè)LCD彩色屏,兩個(gè)LCD屏的接口不一樣,此時(shí)LCD接口電路要重新改動(dòng)

2016-12-23 18:51:28

CPLD在DSP系統(tǒng)中的應(yīng)用設(shè)計(jì)

2011-08-03 16:15:49

CPLD在汽車制動(dòng)性能檢測系統(tǒng)中的應(yīng)用汽車制動(dòng)性是汽車主動(dòng)安全的主要性能之一,是汽車行駛安全的重要保障。因此,汽車的制動(dòng)性能的檢測研究為其制動(dòng)性能試驗(yàn)研究和生產(chǎn)檢測提供了條件,為提高制動(dòng)性能提供了

2009-04-16 13:56:57

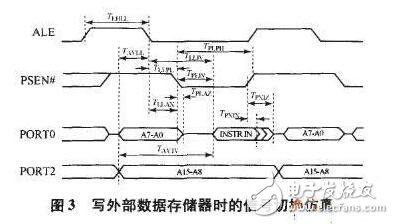

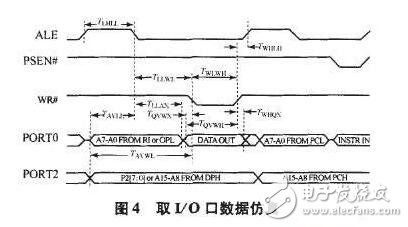

,可是沒有找到,只好自己寫咯,若是只用cpld做51系統(tǒng)的地址譯碼,會(huì)用cpld的都能寫出代碼來,可是cpld與51的總線接口由于涉及到時(shí)序就沒有那么容易了,我也是郁悶了近3天才把接口電路K掉的,它現(xiàn)在

2012-08-10 18:56:47

購買了adsp-21489處理器 。現(xiàn)在有兩個(gè)問題。一:使用ami接口與fpga連接,如何編寫測試程序進(jìn)行讀寫驗(yàn)證;二:如何配置dai下的pdap接口使得其與cpld進(jìn)行互連。求解答。

2019-01-08 09:55:17

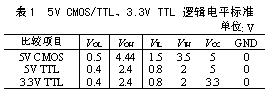

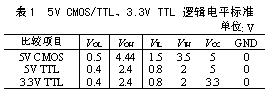

求助FPGA和CPLD和單片機(jī)接口時(shí)能直接接口嗎?(5v3.3v會(huì)不會(huì)燒掉啊)有的同學(xué)說行有的說不行很迷茫好像沒問題但又不敢進(jìn)行電平轉(zhuǎn)換又似乎很麻煩 求大神給個(gè)解釋哈。。。。。。。

2012-07-26 15:32:56

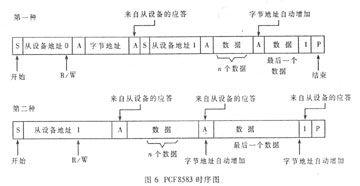

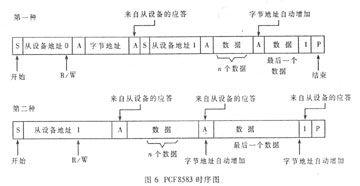

IIC總線通訊接口器件的CPLD實(shí)現(xiàn)摘要:介紹了采用ALTERA公司的可編程器件EPF10K10LC84-3實(shí)現(xiàn)IIC總線的通訊接口的基本原理,并給出了部分的VHDL語言描述。該通訊接口與專用的接口芯片相比,具有使用靈活、系統(tǒng)配置方便的特點(diǎn)。 [/hide]

2009-10-30 14:57:35

購買了adsp-21489處理器 。現(xiàn)在有兩個(gè)問題。

一:使用ami接口與fpga連接,如何編寫測試程序進(jìn)行讀寫驗(yàn)證;

二:如何配置dai下的pdap接口使得其與cpld進(jìn)行互連。求解答。

2024-01-12 07:12:46

的邊界掃描測試第5章 Xilinx Foundation應(yīng)用基礎(chǔ)第6章 Foundation高級(jí)應(yīng)用第7章 VHDL語言簡介第8章 CPLD/FPGA在數(shù)字系統(tǒng)設(shè)計(jì)中的應(yīng)用第9章 CPLD/FPGA在通信

2018-03-29 17:11:59

用Altera_Cpld作了一個(gè)186(主CPU)控制sdram的控制接口, 發(fā)現(xiàn)問題:要使得sdram讀寫正確, 必須把186(主CPU)的clk送給sdram, 而不能把clk經(jīng)cpld的延時(shí)

2019-09-18 05:02:19

什么是CPLD,怎么選擇?CPLD在雙軸位置檢測系統(tǒng)中的應(yīng)用設(shè)計(jì)

2021-04-30 06:24:23

本最近在做基于CPLD+PC104電機(jī)驅(qū)動(dòng)接口板設(shè)計(jì),CPLD上共有來自電機(jī)驅(qū)動(dòng)器和開關(guān)等的24路輸入信號(hào),經(jīng)pc104主板處理后,CPLD輸出6路信號(hào)返回到電機(jī)驅(qū)動(dòng)器。不知道在pc104主線下如何實(shí)現(xiàn)這一過程?求大神指點(diǎn)迷津!

2015-01-29 15:42:30

與聲卡的接口電路 整個(gè)系統(tǒng)結(jié)構(gòu)框圖如圖2所示。從圖中可以看出,CPLD主要完成數(shù)據(jù)總線驅(qū)動(dòng)、地址總線驅(qū)動(dòng)、地址鎖存器、譯碼和時(shí)鐘分頻等功能,其中譯碼電路是整個(gè)電路的核心。數(shù)據(jù)總線驅(qū)動(dòng)電路和地址總線驅(qū)動(dòng)將

2018-12-14 10:57:58

的應(yīng)力值。為了解決快速DSP和慢速外設(shè)之問接口的問題,根據(jù)上述分析系統(tǒng)采用了以CPLD為橋梁的液晶顯示模塊。其主要的工作流程是:DSP把顯示的數(shù)據(jù)送給CPLD,然后DSP去做其他的事情,而后續(xù)顯示

2019-05-21 05:00:16

摘要:介紹了用ALTERA公司MAX7000系列CPLD芯片實(shí)現(xiàn)單片機(jī)與PC104ISA總線接口之間的關(guān)行通信。給出了系統(tǒng)設(shè)計(jì)方法及程序源代碼。關(guān)鍵詞:CPLD ISA總線 并行通信 CPLD

2019-06-20 05:00:02

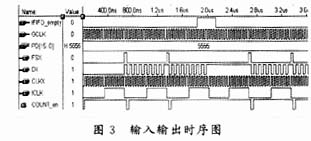

數(shù)據(jù)采集系統(tǒng)控制器的管理下有序進(jìn)行。工作速率由時(shí)鐘信號(hào)CLK的速率決定。1.2 單片機(jī)與CPLD/FPGA接口設(shè)計(jì)單片機(jī)采用以總線方式與可編程芯片進(jìn)行數(shù)據(jù)與控制信息通信,此方式有許多優(yōu)點(diǎn):(1)速度快。其通信工作

2018-12-10 10:18:34

基于CPLD的計(jì)算機(jī)接口設(shè)計(jì)技巧

2012-08-16 19:49:11

基于fpga/cpld的數(shù)字系統(tǒng)設(shè)計(jì)流程包括哪些步驟,EDA——Electronic Design Automation電子設(shè)計(jì)自動(dòng)化EDA是從CAD(計(jì)算機(jī)輔助設(shè)計(jì))、CAM(計(jì)算機(jī)輔助制造

2021-07-27 06:52:45

CPU程序跑飛,控制接口仍有很高抗干擾性能,不會(huì)產(chǎn)生誤跳閘電平,徹底解決繼電保護(hù)系統(tǒng)控制出口的可靠性問題。 CPLD技術(shù)在微機(jī)保護(hù)裝置中應(yīng)用的優(yōu)越性 CPLD(complex

2019-04-25 07:00:04

本文分別針對(duì)Hynix公司的兩款SRAM和DRAM器件,介紹了使用CPLD進(jìn)行接口連接和編程控制,來構(gòu)成低成本、大容量、高速度FIFO的方法。該方法具有通用性,可以方便地移植到與其他RAM器件相連的應(yīng)用中去。

2021-04-15 06:25:14

求助各位大神如何使用ATE對(duì)CPLD進(jìn)行測試???對(duì)CPLD進(jìn)行測試的思路與流程是怎樣的?

2013-02-17 16:14:53

本文根據(jù)國內(nèi)外線纜測試技術(shù)的發(fā)展及生產(chǎn)企業(yè)的實(shí)際要求,設(shè)計(jì)了一種新型便攜式線纜組快速測試系統(tǒng)。該測試系統(tǒng)采用兩塊CPLD 用于接口電路,從而實(shí)現(xiàn)多組線纜(內(nèi)有多條導(dǎo)線)同時(shí)測試,檢測線纜的通斷、短路和錯(cuò)接情況,進(jìn)而達(dá)到快速檢測線纜連通性能的目的。

2021-05-08 06:04:28

嵌入式系統(tǒng)接口測試策略嵌入式系統(tǒng)接口測試策略摘要:在日益廣泛應(yīng)用的嵌入式系統(tǒng)中,軟件測試因?yàn)?b class="flag-6" style="color: red">系統(tǒng)平臺(tái)局限性需要重復(fù)下裝,耗費(fèi)較大的測試資源與時(shí)間成本。文章根據(jù)嵌入式系統(tǒng)軟件的特性,結(jié)合實(shí)際案例智能

2021-10-27 08:41:34

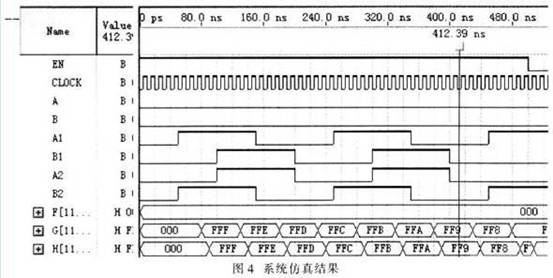

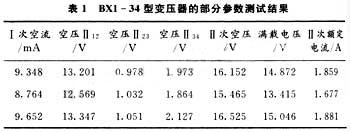

基于MCU+CPLD變壓器測試系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn),不看肯定后悔

2021-04-08 06:21:15

本文根據(jù)國內(nèi)外線纜測試技術(shù)的發(fā)展及生產(chǎn)企業(yè)的實(shí)際要求,設(shè)計(jì)了一種新型便攜式線纜組快速測試系統(tǒng)。該測試系統(tǒng)采用兩塊CPLD 用于接口電路,從而實(shí)現(xiàn)多組線纜(內(nèi)有多條導(dǎo)線)同時(shí)測試,檢測線纜的通斷、短路和錯(cuò)接情況,進(jìn)而達(dá)到快速檢測線纜連通性能的目的。

2021-05-14 06:19:16

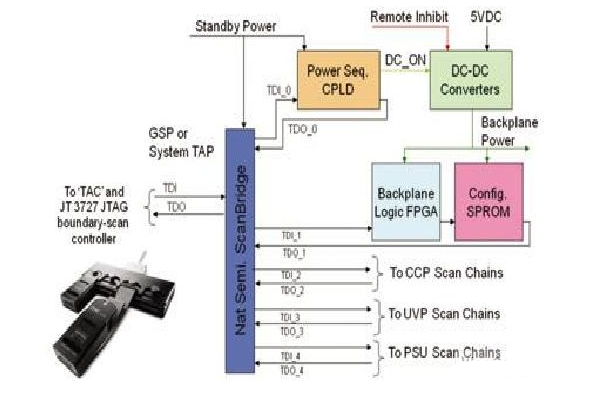

的接口。它們帶有元件編號(hào)和序列號(hào)數(shù)據(jù)等等,還包括最近故障檢測日志。PCI-DIO-96 被作為一個(gè)使用CPLD、有160 個(gè)管腳的DIO,CPLD 將來自測試控制器PC 的I/O 板卡的輸出和輸入進(jìn)行

2013-10-28 14:41:12

降級(jí)。主通信處理器允許通過EFA總線標(biāo)準(zhǔn)、雷達(dá)總線接口、接收器接口和視頻接口對(duì)VP 板卡進(jìn)行訪問。 在測試系統(tǒng)中,NI PCI-6533用作位于每個(gè)SRI(商店可替換品)上EMId(電子模塊標(biāo)識(shí)

2018-09-10 16:49:58

用CPLD設(shè)計(jì)所構(gòu)成的CPI接口系統(tǒng)具有簡潔、可靠等優(yōu)點(diǎn),是一種行之有效的設(shè)計(jì)途徑。很多技術(shù)雜志和網(wǎng)站上,都有不少用CPLD設(shè)計(jì)PCI常規(guī)傳輸系統(tǒng)的文章。但用這些方法在MzxPlusII

2019-06-17 05:00:11

另外,在DSP系統(tǒng)中為什么要使用CPLD?有大俠指導(dǎo)嗎?

2019-07-05 03:42:00

基于CPLD的CAN接口如何去設(shè)計(jì)?

2021-04-28 06:01:30

最近有一個(gè)小題目:使用CPLD和STM32單片機(jī)設(shè)計(jì)一個(gè)具有12路信號(hào)輸入接口的板卡(每一個(gè)接口都是獨(dú)立的,具有自己的固定地址),當(dāng)隨機(jī)接入1~4路方波信號(hào)時(shí),CPLD可以快速判斷是12路接口

2018-06-27 15:24:06

如何實(shí)現(xiàn)CPLD的在系統(tǒng)編程?

2021-04-25 07:05:12

你好。我知道這可能是一個(gè)愚蠢的問題......是否有任何CPLD質(zhì)量測試工具?(在焊接cpld之前)(*我找到一些測試板,但它在焊接后工作。)幾天前isolderonecpld,但直到我改變其他

2019-10-14 09:36:00

的接口電路整個(gè)系統(tǒng)結(jié)構(gòu)框圖如圖2所示。從圖中可以看出,CPLD主要完成數(shù)據(jù)總線驅(qū)動(dòng)、地址總線驅(qū)動(dòng)、地址鎖存器、譯碼和時(shí)鐘分頻等功能,其中譯碼電路是整個(gè)電路的核心。數(shù)據(jù)總線驅(qū)動(dòng)電路和地址總線驅(qū)動(dòng)將DSP

2019-05-31 05:00:03

的是表貼器件,但仍占相當(dāng)大PCB面積,由引腳松動(dòng)、虛焊等原因引發(fā)的故障率較高。采用CPLD器件后,接口電路全部集成在一片中,系統(tǒng)的可靠性、靈活性大大提高。復(fù)雜可編程邏輯器件因其使用方便、具有很高的性價(jià)比,必將擁有廣闊的應(yīng)用前景。

2019-06-05 05:00:14

FPGA/CPLD下載方式 (ISP下載線接口電路)

SP功能提高設(shè)計(jì)和應(yīng)用的靈活性未編程前先焊接安裝系統(tǒng)內(nèi)編

2009-03-08 10:47:02 129

129 為了獲得一定的靈活性,嵌入式系統(tǒng)大都設(shè)計(jì)有可編程邏輯器件CPLD。利用單片機(jī)對(duì)CPLD進(jìn)行編程,可以方便地升級(jí)、修改和測試已完成的設(shè)計(jì)。文中給出了它的實(shí)現(xiàn)過程。

2009-04-03 10:49:49 22

22 詳細(xì)闡述一種利用CPLD 實(shí)現(xiàn)的8 位單片機(jī)與PCI 設(shè)備間的通信接口方案,給出用ABEL HDL編寫的主要源程序。該方案在實(shí)踐中檢驗(yàn)通過。

2009-04-14 17:32:19 34

34 講述快速器件DSP和慢速器件液晶模塊的接口方法;結(jié)合作者實(shí)際工作的一個(gè)成功應(yīng)用,給出TMS320C32 DSP 與內(nèi)藏T6963C 控制器的液晶模塊通過CPLD 接口的硬件和軟件實(shí)例。

2009-04-16 10:26:44 22

22 在單片機(jī)系統(tǒng)中使用CPLD,可使系統(tǒng)構(gòu)成靈活,提高可靠性,縮短開發(fā)周期。介紹在MCS-51 應(yīng)用系統(tǒng)中的CPLD 應(yīng)用設(shè)計(jì)實(shí)例, 詳細(xì)分析CPLD 的應(yīng)用和實(shí)現(xiàn)方法,提出設(shè)計(jì)中選用和使用CPLD

2009-05-14 13:49:49 39

39 本文根據(jù)SPI 同步串行接口的通信協(xié)議,介紹了在CPLD 中利用VHDL 語言實(shí)現(xiàn)PC/104

總線擴(kuò)展SPI 接口的設(shè)計(jì)原理和編程思想。通過該方法的介紹,使得那些沒有SPI

接口功能的

2009-05-30 09:28:18 41

41 講述快速器件DSP 和慢速器件液晶模塊的接口方法;結(jié)合作者實(shí)際工作的一個(gè)成功應(yīng)用,給出TMS320C32 DSP 與內(nèi)藏T6963C 控制器的液晶模塊通過CPLD 接口的硬件和軟件實(shí)例。關(guān)鍵

2009-05-31 14:27:22 22

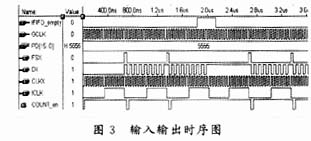

22 介紹了一種基于ARM9 和CPLD 架構(gòu)的嵌入式輸入輸出系統(tǒng)的軟硬件設(shè)計(jì)。系統(tǒng)以工業(yè)級(jí)EP9315 為核心,擴(kuò)展了LCD、觸摸屏、以太網(wǎng)、串口和USB 等控制接口;以MAX2_EPM240為核心,進(jìn)行了

2009-06-01 10:55:12 21

21 本文介紹了一種基于CPLD的溫度采集系統(tǒng)的設(shè)計(jì)方法,設(shè)計(jì)分為溫度采集和LED顯示兩個(gè)功能模塊。與常用溫度采集系統(tǒng)相比,本設(shè)計(jì)采用高精度數(shù)字溫度傳感器MAX6627與CPLD控制芯片E

2009-07-07 13:44:56 22

22 基于CPLD 和DSP 設(shè)計(jì)了線陣CCD 檢測系統(tǒng),CCD 的時(shí)序驅(qū)動(dòng)由CPLD 實(shí)現(xiàn),經(jīng)過運(yùn)放后的視頻信號(hào)由TMS320F2812 進(jìn)行采集和處理,此檢測系統(tǒng)已成功應(yīng)用于醫(yī)藥包裝行業(yè)的數(shù)粒機(jī)系統(tǒng),能夠可

2009-08-13 14:53:46 22

22 介紹了基于CPLD 和EDA 技術(shù)的BIT(機(jī)內(nèi)測試)系統(tǒng)的實(shí)現(xiàn)。本系統(tǒng)以CPLD 為控制核心,在MAX+PLUSII 環(huán)境下采用VHDL 語言實(shí)現(xiàn)了系統(tǒng)接口及測頻電路。該系統(tǒng)具有集成度高、靈活性強(qiáng)、易于開

2009-09-03 09:30:51 9

9 本文提出了一種基于CPLD 的雙向并行通信接口,這種接口設(shè)計(jì)簡單明了,可以解決兩主機(jī)之間傳輸速率不一致問題,實(shí)現(xiàn)了可靠實(shí)時(shí)的數(shù)

2009-09-04 08:23:21 17

17 復(fù)雜可編程邏輯器件(CPLD)結(jié)合了專用集成電路和DSP 的優(yōu)勢,既具有很高的處理速度,又具有一定的靈活性。因此,基于CPLD 的數(shù)字調(diào)制系統(tǒng)的研究具有重要的實(shí)際意義。本文論

2009-11-30 16:30:17 20

20 基于對(duì)IC 測試接口原理和系統(tǒng)結(jié)構(gòu)的闡釋,具體針對(duì)型號(hào)為SL431L 的電源芯片,提出改進(jìn)測試電路的方法,電壓測試值的波動(dòng)范圍小于3mV。關(guān)鍵詞:測試系統(tǒng)結(jié)構(gòu),測試接口,芯片

2009-12-19 15:10:33 33

33 介紹了一種基于ARM9 和CPLD 架構(gòu)的嵌入式輸入輸出系統(tǒng)的軟硬件設(shè)計(jì)。系統(tǒng)以工業(yè)級(jí)EP9315 為核心,擴(kuò)展了LCD、觸摸屏、以太網(wǎng)、串口和USB 等控制接口;以MAX2_EPM240為核心,進(jìn)行了

2009-12-22 11:33:23 30

30 本文針對(duì)新型匝間耐壓測試儀中需要高速采集數(shù)據(jù)的問題提出了一種結(jié)合CPLD 與單片機(jī)的高速數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)方案。CPLD 產(chǎn)生A/D 芯片的控制時(shí)序以及SRAM 的讀寫控制時(shí)序,單片機(jī)輸

2009-12-23 14:59:57 88

88 本文詳細(xì)介紹了USB 總線的光隔離接口的隔離原理、硬件組成及控制程序的設(shè)計(jì)。該實(shí)現(xiàn)方案采用先進(jìn)的高速光隔離技術(shù)和CPLD 控制技術(shù),對(duì)基于USB 的測試與測量的設(shè)備、人體起保

2009-12-23 15:04:38 25

25 在單片機(jī)系統(tǒng)中使用CPLD,可使系統(tǒng)構(gòu)成靈活,提高可靠性,縮短開發(fā)周期。介紹在MCS-51應(yīng)用系統(tǒng)中的CPLD應(yīng)用設(shè)計(jì)實(shí)例,詳細(xì)分析CPLD的應(yīng)用和實(shí)現(xiàn)方法,提出設(shè)計(jì)中選用和使用CPLD的

2010-07-14 14:04:25 39

39 介紹了基于CPLD的刷卡式電腦聯(lián)網(wǎng)集控型自動(dòng)存包系統(tǒng)的設(shè)計(jì),并對(duì)系統(tǒng)的軟硬件構(gòu)成、CPLD內(nèi)部邏輯設(shè)計(jì)、工作原理等進(jìn)行了詳細(xì)說明。該系統(tǒng)速度快、安全性好、可靠性高,而且具

2010-07-16 15:11:12 20

20 本文詳細(xì)介紹了USB總線的光隔離接口的隔離原理、硬件組成及控制程序的設(shè)計(jì)。該實(shí)現(xiàn)方案采用先進(jìn)的高速光隔離技術(shù)和CPLD控制技術(shù),對(duì)基于USB的測試與測量的設(shè)備、人體起保護(hù)作用

2010-07-21 17:26:16 19

19 本文介紹了利用Xilinx公司的XC9500系列CPLD器件,以I2S接口方式對(duì)四路輸入語音信號(hào)進(jìn)行處理與傳輸,并用VHDL進(jìn)行建模,通過ISE軟件仿真得出了比較理想的結(jié)果,并在工程應(yīng)用中使用良

2010-08-06 15:54:34 62

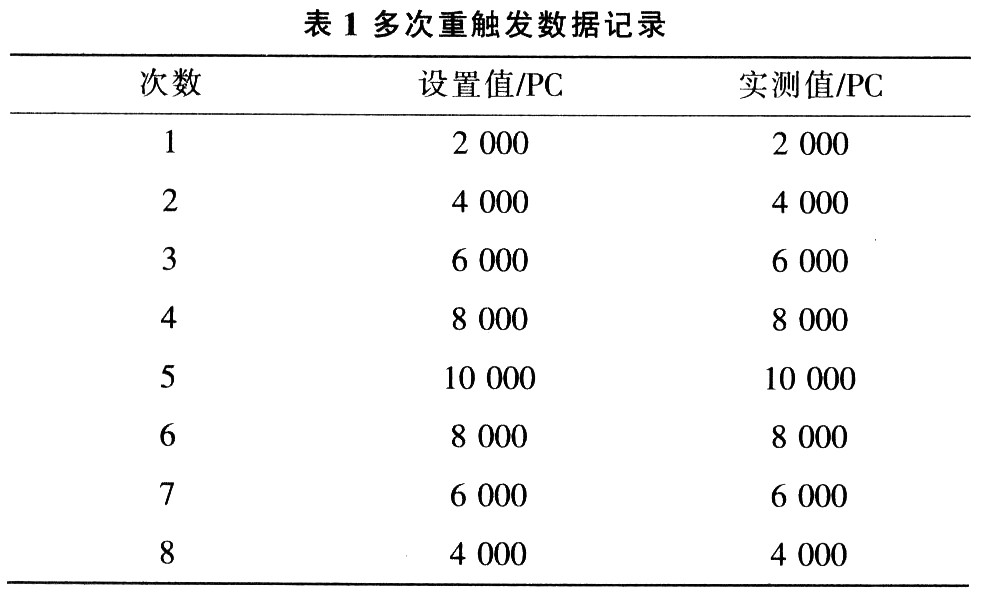

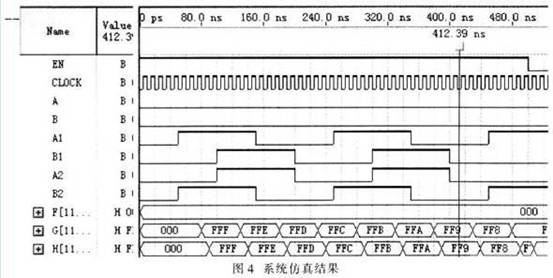

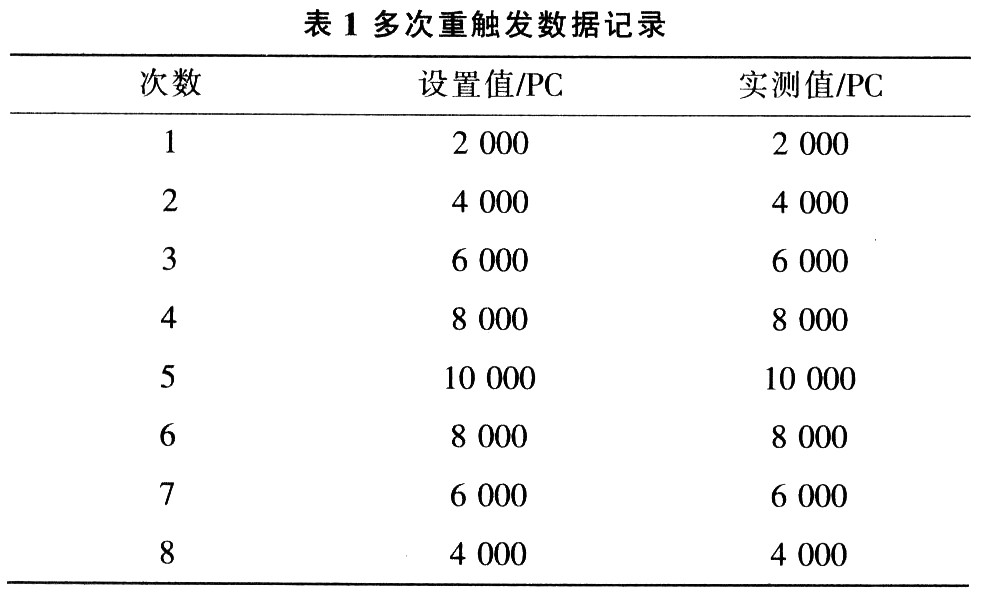

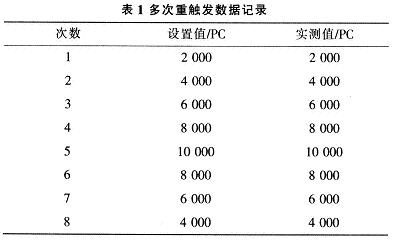

62 提出一種基于CPLD的多次重觸發(fā)存儲(chǔ)測試系統(tǒng)設(shè)計(jì)方案,詳細(xì)介紹系統(tǒng)硬件設(shè)計(jì)以及CPLD內(nèi)部控制原理,并對(duì)CPLD控制電路仿真。該系統(tǒng)體積小、功耗低,能夠?qū)崟r(shí)記錄多次重觸發(fā)信號(hào)

2010-12-30 16:05:11 22

22 摘 要: 本文采用Altera的CPLD實(shí)現(xiàn)了PCI總線至UTOPIA接口的邏輯轉(zhuǎn)換控制,為低成本實(shí)現(xiàn)ATM終端奠定了基礎(chǔ)。

2006-03-11 13:16:50 864

864

基于DSP與CPLD的I2C總線接口的設(shè)計(jì)與實(shí)現(xiàn)

帶有I2C總線接口的器件可以十分方便地將一個(gè)或多個(gè)單片機(jī)及外圍器件組成單片機(jī)系統(tǒng)。盡管這種總線結(jié)構(gòu)沒有并行總線那

2009-03-28 15:07:47 1105

1105

I2C器件接口IP核的CPLD設(shè)計(jì)

根據(jù)單片機(jī)I2C串行擴(kuò)展的特點(diǎn),在EDA軟件MaxplusII的環(huán)境下,利用AHDL語言,建立IP核。此設(shè)計(jì)利用狀態(tài)機(jī)實(shí)現(xiàn),在給出設(shè)計(jì)的同時(shí)詳細(xì)說明IP核的建立

2009-03-28 16:21:35 1076

1076

什么是CPLD

CPLD(Complex Programmable Logic Device)是Complex PLD的簡稱,一種較PLD為復(fù)雜的邏輯元件。CPLD是一種用戶根據(jù)各自

2009-03-30 13:40:43 3143

3143 【摘 要】 根據(jù)McBSP和CPLD的時(shí)序分析,采用VHDL語言設(shè)計(jì)了CPLD模擬McBSP并與之進(jìn)行全雙工通信,給出了實(shí)際的接口時(shí)序結(jié)果。

2009-05-14 20:40:02 1130

1130

摘要: 較詳細(xì)地闡述不同邏輯電平的接口原理。以低壓CPLD EPM7512A為例,給出在混合電壓系統(tǒng)中的具體設(shè)計(jì)方案。

關(guān)鍵詞: 低壓CPLD 邏輯電平

2009-06-20 10:53:23 800

800

摘要:詳細(xì)闡述一種利用CPLD實(shí)現(xiàn)的8位單片機(jī)與PCI設(shè)備間的通信接口方案,給出用ABEL HDL編寫的主要源程序。該方案在實(shí)踐中檢驗(yàn)通過。

關(guān)鍵詞:單片機(jī) CPLD PCI

8位單片

2009-06-20 13:31:29 869

869

基于CPLD的單片機(jī)與PCI接口設(shè)計(jì)解決方案

8位單片機(jī)在嵌入式系統(tǒng)中應(yīng)用廣泛,然而讓它直接與PCI總線設(shè)備打交道卻有其固有缺陷。8位單片機(jī)只有16位

2009-09-26 17:41:20 825

825

基于CPLD和嵌入式系統(tǒng)的高速數(shù)據(jù)采集系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn)

介紹一種基于CPLD和嵌入式系統(tǒng)的高速數(shù)據(jù)采集系統(tǒng),并詳細(xì)闡述了系統(tǒng)的結(jié)構(gòu)和軟硬件的實(shí)

2009-10-15 23:46:59 615

615

CPLD在雙軸位置檢測系統(tǒng)中的應(yīng)用

1 引言數(shù)控機(jī)床的加T精度主要南位置檢測系統(tǒng)的精度決定,

2009-10-30 08:32:33 431

431

基于USB接口的通用測試儀的設(shè)計(jì)與實(shí)現(xiàn)

隨著片上系統(tǒng)(SoC,System on Chip)時(shí)代的到來,包括復(fù)雜可編程邏輯器件(CPLD,Complex ProgrammableLogic Devi(e)和現(xiàn)場

2009-11-12 10:18:29 1004

1004

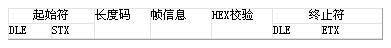

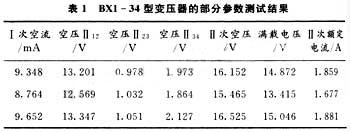

基于MCU CPLD變壓器測試系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn)

1 引言

???? BX型信號(hào)變壓器,BG型軌道變壓器和ZG型硅整流器作為鐵路信號(hào)電器設(shè)備的前端,其工作的穩(wěn)定性

2010-01-07 10:50:50 1199

1199

采用CPLD的多次重觸發(fā)存儲(chǔ)測試系統(tǒng)解決方案

概述:提出一種基于CPLD的多次重觸發(fā)存儲(chǔ)測試系統(tǒng)設(shè)計(jì)方案,詳細(xì)介紹系統(tǒng)硬件設(shè)計(jì)以及CPLD內(nèi)部控制

2010-03-17 11:37:51 531

531

采用CPLD的多次重觸發(fā)存儲(chǔ)測試系統(tǒng)的實(shí)現(xiàn)

1 引言

多次重觸發(fā)技術(shù)應(yīng)用于多種場合,如一個(gè)30齒的齒輪,設(shè)齒輪嚙臺(tái)系數(shù)為1.2,若測量其中1齒多次嚙合

2010-03-25 09:04:36 601

601

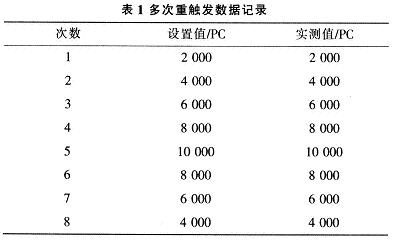

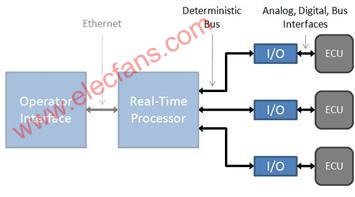

高性能模塊化的I/O接口是構(gòu)建成功硬件在環(huán)測試系統(tǒng)所必須的。硬件在環(huán)(HIL)測試系統(tǒng)體系結(jié)構(gòu)教程討論了多種硬件在環(huán)測試系統(tǒng)體系結(jié)構(gòu)和用于實(shí)現(xiàn)的實(shí)時(shí)處理技術(shù)。本教程討

2010-06-18 09:56:19 1468

1468

本文討論的四種常用FPGA/CPLD設(shè)計(jì)思想與技巧:乒乓操作、串并轉(zhuǎn)換、流水線操作、數(shù)據(jù)接口同步化,都是FPGA/CPLD邏輯設(shè)計(jì)的內(nèi)在規(guī)律的

2010-11-04 10:11:28 625

625

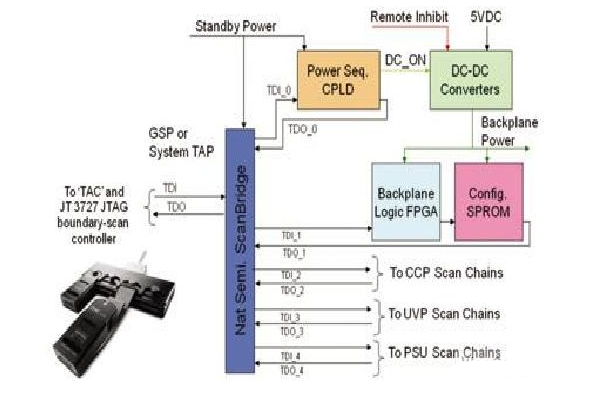

摘要:通信電源技術(shù)的發(fā)展,對(duì)其生產(chǎn)測試設(shè)備提出了更高的要求。本文在實(shí)踐的基礎(chǔ)上,利用CPLD設(shè)計(jì)工業(yè)電源系統(tǒng)插框生產(chǎn)測試系統(tǒng),簡化了電路設(shè)計(jì),縮短了開發(fā)周期,提高了系統(tǒng)的可靠性。利用該系統(tǒng)可以實(shí)現(xiàn)被測系統(tǒng)的故障定位。 關(guān)鍵詞:通信電源;生產(chǎn)測試

2011-02-24 12:32:12 31

31 高性能模塊化的I/O接口是構(gòu)建成功硬件在環(huán)測試系統(tǒng)所必須的。硬件在環(huán)(HIL)測試系統(tǒng)體系結(jié)構(gòu)教程討論了多種硬件在環(huán)測試系統(tǒng)結(jié)構(gòu)和用于實(shí)現(xiàn)的實(shí)時(shí)處理技術(shù)。本教程討厭了多種

2011-04-05 17:25:32 179

179 設(shè)計(jì)了利用TMS320LF2407A與EPM3032A控制的ADS7805多通道采集系統(tǒng)的邏輯結(jié)構(gòu),介紹了系統(tǒng)的工作原理,詳細(xì)描述了ADS7805、DSP及CPLD之間接口的硬件與軟件設(shè)計(jì)。

2011-09-27 14:33:51 1810

1810 CPLD在高速數(shù)據(jù)采集系統(tǒng)中的應(yīng)用! 介紹了高速數(shù)據(jù)采集系統(tǒng)的整體框架分析了其中的通用部分CPLD系列產(chǎn)品的特點(diǎn)及其開發(fā)軟件.CPLD根據(jù)高速數(shù)據(jù)采集系統(tǒng)的需要VHDL語言的形式,介紹了由

2011-12-17 00:12:00 26

26 設(shè)計(jì)了基于CPLD的低功耗溫度存儲(chǔ)式測試系統(tǒng);運(yùn)用鎢錸熱電偶溫度傳感器匹配先進(jìn)的電源管理模塊,并結(jié)合動(dòng)態(tài)存儲(chǔ)測試技術(shù),能夠應(yīng)用于環(huán)境條件比較差的惡劣環(huán)境中,在可靠可信、

2012-02-16 16:55:41 27

27 文中主要介紹了采用CPLD實(shí)現(xiàn)32 bit 33 MHzPCI從設(shè)備接口的設(shè)計(jì)方法,該從設(shè)備接口模塊遵從PCI規(guī)范2.2版,實(shí)現(xiàn)了資源的自動(dòng)配置,支持突發(fā)傳輸,并為用戶提供了一個(gè)簡單的接口。設(shè)計(jì)完成

2012-08-06 15:18:22 1788

1788

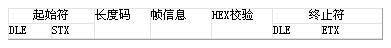

摘要:本系統(tǒng)采用cPLD和AvR單片機(jī)作為邏輯控制核心,設(shè)計(jì)了姿態(tài)存儲(chǔ)測試系統(tǒng),以實(shí)現(xiàn)姿態(tài)信息的采集、編幀和存儲(chǔ)。詳細(xì)介紹了姿態(tài)測試系統(tǒng)的工作原理和硬件設(shè)計(jì)。利用AVR單片機(jī),

2013-03-06 16:00:38 22

22 基于CPLD的多路音頻采集系統(tǒng),有需要的下來看看。

2016-01-21 11:07:07 28

28 基于ARM和CPLD的無線內(nèi)窺系統(tǒng)設(shè)計(jì)

2017-01-24 16:15:38 19

19 鉆取采樣裝置靜態(tài)接口測試系統(tǒng)設(shè)計(jì)_陳德靖

2017-01-19 21:54:15 0

0 GPS接收機(jī)中1553B總線接口的CPLD設(shè)計(jì)

2017-02-07 15:53:43 10

10 基于CPLD高速數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)_鮮果

2017-03-19 11:45:23 3

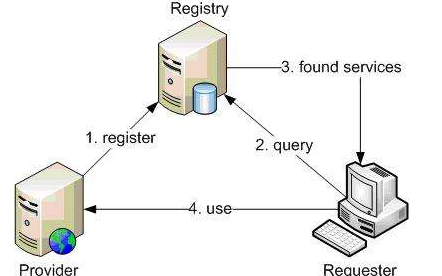

3 接口測試是測試系統(tǒng)組件間接口的一種測試。接口測試主要用于檢測外部系統(tǒng)與系統(tǒng)之間以及內(nèi)部各個(gè)子系統(tǒng)之間的交互點(diǎn)。測試的重點(diǎn)是要檢查數(shù)據(jù)的交換,傳遞和控制管理過程,以及系統(tǒng)間的相互邏輯依賴關(guān)系等。接口測試大體分為兩類:模塊接口測試和web接口測試。

2019-01-04 16:04:23 2373

2373

的通用性;此外CPLD內(nèi)部有豐富的邏輯資源,可將用戶控制邏輯和PCI接口邏輯在同一塊芯片中實(shí)現(xiàn),這樣不僅充分利用了邏輯資源,還能使系統(tǒng)設(shè)計(jì)顯得更加緊湊。

2020-03-20 09:54:04 1266

1266

嵌入式系統(tǒng)接口測試策略嵌入式系統(tǒng)接口測試策略摘要:在日益廣泛應(yīng)用的嵌入式系統(tǒng)中,軟件測試因?yàn)?b class="flag-6" style="color: red">系統(tǒng)平臺(tái)局限性需要重復(fù)下裝,耗費(fèi)較大的測試資源與時(shí)間成本。文章根據(jù)嵌入式系統(tǒng)軟件的特性,結(jié)合實(shí)際案例智能

2021-10-20 19:06:08 13

13 在測試系統(tǒng)中,NI PCI-6533用作位于每個(gè)SRI(商店可替換品)上EMId(電子模塊標(biāo)識(shí))設(shè)備的接口。它們帶有元件編號(hào)和序列號(hào)數(shù)據(jù)等等,還包括近故障檢測日志。PCI-DIO-96 被作為

2023-10-17 14:53:08 192

192

電子發(fā)燒友網(wǎng)站提供《一種通用基于CPLD實(shí)現(xiàn)的CAN接口連接設(shè)計(jì).pdf》資料免費(fèi)下載

2023-10-27 11:29:01 0

0

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論