的PCB走線的時(shí)候一旦產(chǎn)生了開環(huán)的結(jié)果,將產(chǎn)生線形天線,增加EMI的輻射強(qiáng)度。圖3 開環(huán)規(guī)則規(guī)則四:高速信號(hào)的特性阻抗連續(xù)規(guī)則高速信號(hào),在層與層之間切換的時(shí)候必須保證特性阻抗的連續(xù),否則會(huì)增加EMI的輻射

2018-11-28 11:14:18

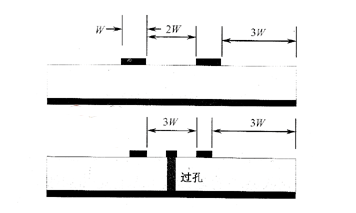

3W原則在PCB設(shè)計(jì)中為了減少線間串?dāng)_,應(yīng)保證線間距足夠大,當(dāng)線中心間距不少于3倍線寬時(shí),則可保持大部分電場(chǎng)不互相干擾,這就是3W規(guī)則。3W原則是指多個(gè)高速信號(hào)線長(zhǎng)距離走線的時(shí)候,其間距...

2022-01-26 06:50:22

布線(Layout)是PCB設(shè)計(jì)工程師最基本的工作技能之一。走線的好壞將直接影響到整個(gè)系統(tǒng)的性能,大多數(shù)高速的設(shè)計(jì)理論也要最終經(jīng)過(guò) Layout 得以實(shí)現(xiàn)并驗(yàn)證,由此可見,布線在高速 PCB 設(shè)計(jì)中

2015-01-12 14:53:57

、高速PCB設(shè)計(jì)中,蛇形線沒(méi)有所謂濾波或抗干擾的能力,只可能降低信號(hào)質(zhì)量,所以只作時(shí)序匹配之用而無(wú)其它目的。 7、有時(shí)可以考慮螺旋走線的方式進(jìn)行繞線,仿真表明,其效果要優(yōu)于正常的蛇形走線。

2018-09-13 15:50:25

下面從直角走線、差分走線、蛇形線三個(gè)方面來(lái)闡述PCB LAYOUT的走線。

2021-03-17 07:25:46

本帖最后由 一生紅與黑 于 2012-2-3 13:52 編輯

3W原則:這里3W是線與線之間的距離保持3倍線寬。你說(shuō)3H也可以。但是這里H指的是線寬度。不是介質(zhì)厚度。是為了減少線間串?dāng)_,應(yīng)

2012-01-17 14:21:41

3W原則:4 A2 [3 F4 A. C這里3W是線與線之間的距離保持3倍線寬。你說(shuō)3H也可以。但是這里H指的是線寬度。不是介質(zhì)厚度。是為了減少線間串?dāng)_,應(yīng)保證線間距足夠大,如果線中心距不少于3倍

2014-10-28 15:29:44

布線(Layout)是PCB設(shè)計(jì)工程師最基本的工作技能之一。走線的好壞將直接影響到整個(gè)系統(tǒng)的性能,大多數(shù)高速的設(shè)計(jì)理論也要最終經(jīng)過(guò) Layout 得以實(shí)現(xiàn)并驗(yàn)證,由此可見,布線在高速 PCB 設(shè)計(jì)中

2019-06-10 10:11:23

本帖最后由 maskmyself 于 2017-7-10 10:08 編輯

布線(Layout)是PCB設(shè)計(jì)工程師最基本的工作技能之一。走線的好壞將直接影響到整個(gè)系統(tǒng)的性能,大多數(shù)高速

2017-07-07 11:45:56

布線(Layout)是PCB設(shè)計(jì)工程師最基本的工作技能之一。走線的好壞將直接影響到整個(gè)系統(tǒng)的性能,大多數(shù)高速的設(shè)計(jì)理論也要最終經(jīng)過(guò)Layout得以實(shí)現(xiàn)并驗(yàn)證,由此可見,布線在高速PCB設(shè)計(jì)中

2019-05-23 08:52:37

布線(Layout)是PCB設(shè)計(jì)工程師最基本的工作技能之一。走線的好壞將直接影響到整個(gè)系統(tǒng)的性能,大多數(shù)高速的設(shè)計(jì)理論也要最終經(jīng)過(guò)Layout得以實(shí)現(xiàn)并驗(yàn)證,由此可見,布線在高速PCB設(shè)計(jì)中

2014-08-13 15:44:05

布線(Layout)是PCB設(shè)計(jì)工程師最基本的工作技能之一。走線的好壞將直接影響到整個(gè)系統(tǒng)的性能,大多數(shù)高速的設(shè)計(jì)理論也要最終經(jīng)過(guò)Layout得以實(shí)現(xiàn)并驗(yàn)證,由此可見,布線在高速PCB設(shè)計(jì)中

2019-08-05 06:40:24

新人,求PCB布局走線資料,謝謝!

2014-08-02 19:19:40

大安全間距等方法。保證信號(hào)質(zhì)量。

d) 有阻抗控制要求的網(wǎng)絡(luò)應(yīng)布置在阻抗控制層上,須避免其信號(hào)跨分割。

2布線竄擾控制

a) 3W原則釋義

線與線之間的距離保持3倍線寬。是為了減少線間串?dāng)_,應(yīng)保證線間距足夠大,如果線中心距不少于3倍線寬時(shí),則可保持70%的線間電場(chǎng)不互相干擾,稱為3W規(guī)則。

2023-12-12 09:23:35

,MIPI信號(hào)線應(yīng)遠(yuǎn)離其它高速、高頻信號(hào)(并行數(shù)據(jù)線、時(shí)鐘線等),至少保持3W以上的距離且絕不能平行走線。對(duì)開關(guān)電源這一類的干擾源更應(yīng)遠(yuǎn)離。 過(guò)孔:MIPI信號(hào)線盡量不要打過(guò)孔,如有過(guò)孔則線對(duì)上的兩根

2023-04-12 15:08:27

好的圖像質(zhì)量的保證。 PCB走線如果可能的話,信號(hào)走線使用6mil, 走線間距使用6mil. 放置0.1uF的退耦電容在對(duì)應(yīng)的DSP電源腳上,并盡可能的靠近。它的走線盡可能的粗。電源正極的走線最少要

2023-04-13 16:09:54

求高手貢獻(xiàn)PCB設(shè)計(jì)走線經(jīng)驗(yàn)!及相關(guān)技術(shù)

2013-01-11 20:02:07

來(lái)說(shuō),沒(méi)有按照正確的方法評(píng)估走線線寬,可能導(dǎo)致電流過(guò)大,燒毀板子走線;對(duì)于高速信號(hào)來(lái)說(shuō),沒(méi)有合適的計(jì)算線寬,可能導(dǎo)致阻抗失配,引起信號(hào)完整性問(wèn)題。 2.PCB走線跟哪些因素有關(guān) PCB的走線主要跟

2023-04-12 16:02:23

`為什么下圖中PCB走線正反面不同。孔與孔之間為直接通路。為什么背面的走線環(huán)繞迂回。小白菜提問(wèn),求高手詳解。謝謝`

2018-10-29 08:46:46

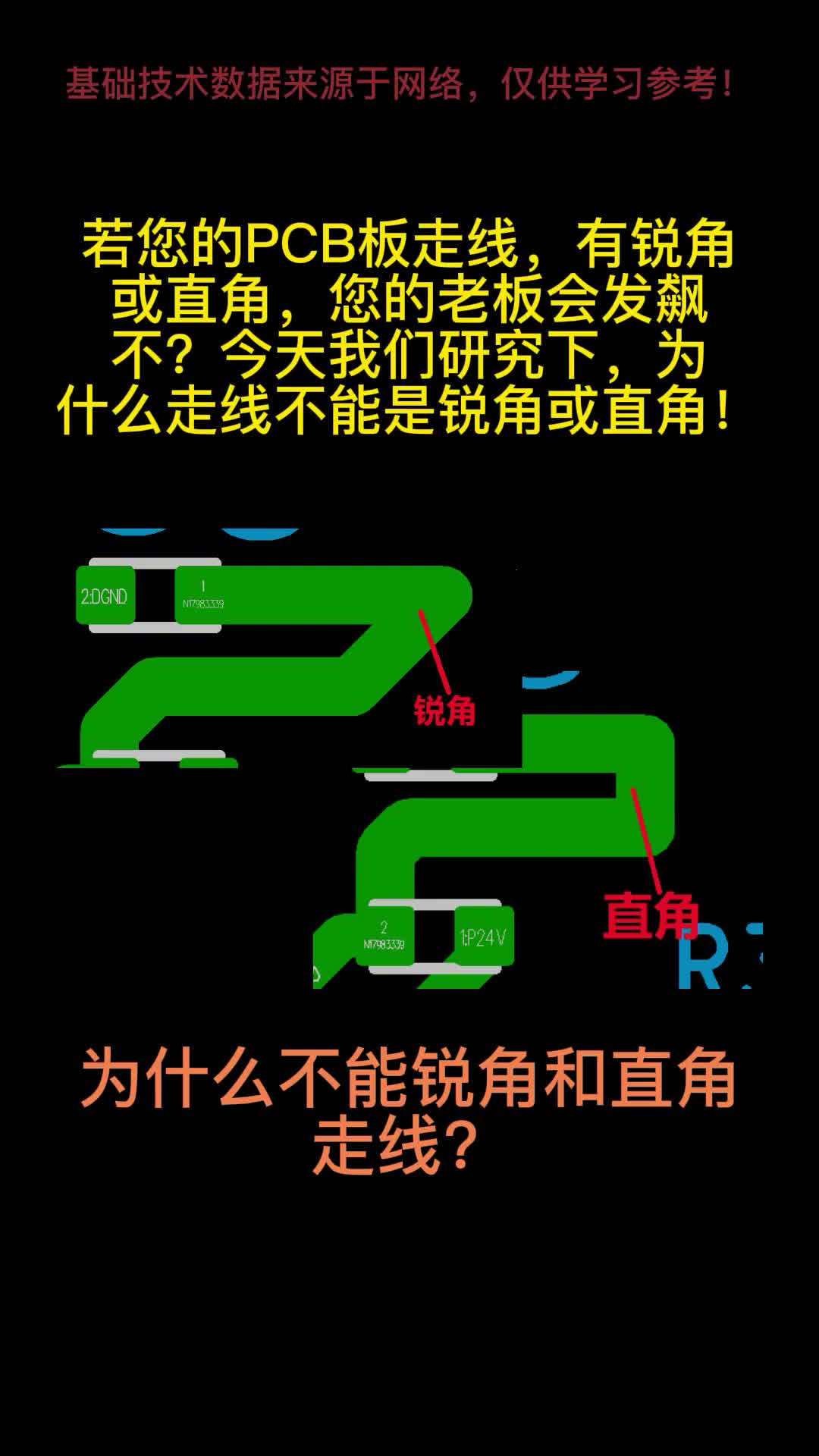

不出來(lái),高速PCB設(shè)計(jì)工程師的重點(diǎn)還是應(yīng)該放在布局,電源/地設(shè)計(jì),走線設(shè)計(jì),過(guò)孔等其他方面。當(dāng)然,盡管直角走線帶來(lái)的影響不是很嚴(yán)重,但并不是說(shuō)我們以后都可以走直角線,注意細(xì)節(jié)是每個(gè)優(yōu)秀工程師必備的基本素質(zhì)

2014-11-18 17:29:31

采訪過(guò)蘋果公司CEO的B站up主-何同學(xué),近期更新一條視頻中,有出現(xiàn)過(guò)他自己設(shè)計(jì)的PCB圖。很多人說(shuō)他不應(yīng)該直角走線。PCB為什么不能直角走線呢?一般在高速信號(hào)線中,直角線會(huì)帶來(lái)阻抗的不均勻

2022-09-08 16:54:17

經(jīng)常聽說(shuō)“PCB走線間距大于等于3倍線寬時(shí)可以抑制70%的信號(hào)間干擾”,這就是3W原則,信號(hào)線之間的干擾被稱為串?dāng)_。那么,你知道串?dāng)_是怎么形成的嗎?當(dāng)兩條走線很近時(shí),一條信號(hào)線上的信號(hào)可能會(huì)在另一

2022-12-27 20:33:40

在pcb的設(shè)計(jì)過(guò)程中,元器件的布局和走線的調(diào)整是非常重要的一個(gè)步驟。恰當(dāng)?shù)牟季挚梢院?jiǎn)化布線的難度,更重要的是可以提高PCB的電氣性能,減少EMC,EMI。 下面是同一個(gè)原理圖對(duì)應(yīng)的兩種不同的布局和走

2019-10-17 04:37:54

布線(Layout)是pcb設(shè)計(jì)工程師最基本的工作技能之一。走線的好壞將直接影響到整個(gè)系統(tǒng)的性能,大多數(shù)高速的設(shè)計(jì)理論也要最終經(jīng)過(guò)Layout得以實(shí)現(xiàn)并驗(yàn)證,由此可見,布線在高速PCB設(shè)計(jì)中

2019-08-21 07:30:00

PCB電容引腳之間可以走線嗎?

2023-04-13 16:25:48

$ z/ V( f0 C5 c 總的說(shuō)來(lái),直角走線并不是想象中的那么可怕。至少在GHz以下的應(yīng)用中,其產(chǎn)生的任何諸如電容,反射,EMI等效應(yīng)在TDR測(cè)試中幾乎體現(xiàn)不出來(lái),高速PCB設(shè)計(jì)工程師的重點(diǎn)還是

2014-10-28 15:08:55

1.1 PCB板上預(yù)劃分?jǐn)?shù)字、模擬、DAA信號(hào)布線區(qū)域。1.2 數(shù)字、模擬元器件及相應(yīng)走線盡量分開并放置於各自的布線區(qū)域內(nèi)。1.3 高速數(shù)字信號(hào)走線盡量短。1.4 敏感模擬信號(hào)走線盡量短。1.5

2019-05-30 06:58:19

減少布線層,降低PCB成本。 當(dāng)然,這樣做的代價(jià)是冒一些技術(shù)風(fēng)險(xiǎn),甚至犧牲一半成功率。 對(duì)于背板的層疊設(shè)計(jì),鑒于常見背板很難做到相鄰走線互相垂直,不可避免地出現(xiàn)平面長(zhǎng)距離布線。 對(duì)于高速背板

2023-04-12 15:12:13

硬件工程師做久了自然有自己處理電路板的一套方法,也許不是最好的辦法,自己卻能理解其中的意義。但是工作中還是要按照最完美的辦法進(jìn)行操作,本期我們就來(lái)了解一下關(guān)于高速信號(hào)走線準(zhǔn)則到底有哪幾條是你不清楚的?

2020-10-30 08:33:48

`3W原則在PCB設(shè)計(jì)中為了減少線間串?dāng)_,應(yīng)保證線間距足夠大,當(dāng)線中心間距不少于3倍線寬時(shí),則可保持大部分電場(chǎng)不互相干擾,這就是3W規(guī)則。3W原則是指多個(gè)高速信號(hào)線長(zhǎng)距離走線的時(shí)候,其間距應(yīng)該遵循

2020-09-27 16:49:19

電容,反射,EMI等效應(yīng)在TDR測(cè)試中幾乎體現(xiàn)不出來(lái),高速PCB設(shè)計(jì)工程師的重點(diǎn)還是應(yīng)該放在布局,電源/地設(shè)計(jì),走線設(shè)計(jì),過(guò)孔等其他方面。當(dāng)然,盡管直角走線帶來(lái)的影響不是很嚴(yán)重,但并不是說(shuō)我們以后都可以

2018-09-17 17:31:52

的數(shù)據(jù);在走線時(shí)一般遵循3W法則(繞線的間距要兩倍于線寬),這樣可消除線間78%的互感,盡量減少因電感變化而引起的阻抗不連續(xù)。 另外說(shuō)明我不是高手,抬得越高摔得越痛;若想見識(shí)高手,可以到WWW

2014-11-19 11:54:01

1. 一般規(guī)則1.1 PCB板上預(yù)劃分?jǐn)?shù)字、模擬、DAA信號(hào)布線區(qū)域。1.2 數(shù)字、模擬元器件及相應(yīng)走線盡量分開并放置於各自的布線區(qū)域內(nèi)。1.3 高速數(shù)字信號(hào)走線盡量短。1.4 敏感模擬信號(hào)走線盡量

2014-03-14 17:44:44

pcb布局,走線方面,有什么建議嗎,該怎么怎么走,怎么提高效率

2016-10-15 14:51:34

;=2倍的線寬。PCI板上的蛇行線就是為了適應(yīng)PCI 33MHzClock的線長(zhǎng)要求。若在一般普通PCB板中,是一個(gè)分布參數(shù)的 LC濾波器,還可作為收音機(jī)天線的電感線圈,短而窄的蛇形走線可做保險(xiǎn)絲等等

2019-05-22 02:48:05

問(wèn)題,布線應(yīng)遵循3-W原則。 3-W原則就是讓所有的信號(hào)走線的間隔距離滿足:走線邊沿之間的距離應(yīng)該大于或等于2倍的走線寬度,即兩條走線中心之間的距離應(yīng)該大于或等于走線寬度的3倍。對(duì)于靠近PCB邊緣的走線

2018-11-27 15:26:40

誤區(qū)一:認(rèn)為差分信號(hào)不需要地平面作為回流路徑,或者認(rèn)為差分走線彼此為對(duì)方提供回流途徑。造成這種誤區(qū)的原因是被表面現(xiàn)象迷惑,或者對(duì)高速信號(hào)傳輸?shù)臋C(jī)理認(rèn)識(shí)還不夠深入。從圖1-8-15的接收端的結(jié)構(gòu)可以

2012-12-18 12:03:00

誤區(qū)一:認(rèn)為差分信號(hào)不需要地平面作為回流路徑,或者認(rèn)為差分走線彼此為對(duì)方提供回流途徑。造成這種誤區(qū)的原因是被表面現(xiàn)象迷惑,或者對(duì)高速信號(hào)傳輸?shù)臋C(jī)理認(rèn)識(shí)還不夠深入。從圖1-8-15的接收端的結(jié)構(gòu)可以

2012-12-19 16:52:38

高速PCB信號(hào)走線的九條規(guī)則.pdf(220.78 KB)

2019-09-16 07:26:43

多層PCB通常用于高速、高性能的系統(tǒng),其中一些層用于電源或地參考平面,這些平面通常是沒(méi)有分割的實(shí)體平面。無(wú)論這些層做什么用途,電壓為多少,它們將作為與之相鄰的信號(hào)走線的電流返回路徑。構(gòu)造一個(gè)好

2018-11-27 15:14:59

分對(duì)之間的距離;s為差分對(duì)兩根信號(hào)線間的距離;W為差分對(duì)走線的寬度;Ff為介質(zhì)厚度。 使用差分對(duì)走線時(shí),要遵循以下原則: · 保持差分對(duì)的兩信號(hào)走線之間的距離S在整個(gè)走線上為常數(shù); · 確保D

2018-11-27 10:56:15

°拐角;另一種方法是用圓角,如圖2所示。圓角方式是最好的,45°拐角可以用到10 GHz頻率上。值得注意的是,對(duì)于45°拐角走線,拐角長(zhǎng)度最好滿足:L≥31W。 圖1直角拐角的高頻等效電路 圖2拐角走線的處理 歡迎轉(zhuǎn)載,信息維庫(kù)電子市場(chǎng)網(wǎng)(www.dzsc.com):

2018-11-27 10:55:56

上期講到了高速PCB設(shè)計(jì)中建立元件庫(kù)的方法元件放置完成后接下來(lái)的重點(diǎn)便是連接走線▼▼原理圖走線▼▼在原理圖走線中有導(dǎo)線的連接和總線的連接。執(zhí)行Place指令下的操作,可以用以添加連線(Wire

2017-03-02 11:55:35

。也就是說(shuō),同層的布線的寬度必須連續(xù),不同層的走線阻抗必須連續(xù)。 規(guī)則五:高速PCB設(shè)計(jì)的布線方向規(guī)則 相鄰兩層間的走線必須遵循垂直走線的原則,否則會(huì)造成線間的串?dāng)_,增加EMI輻射。 簡(jiǎn)而言之

2016-01-19 22:50:31

。 而絕對(duì)的要求是控制兩個(gè)器件之間的走線延遲為某一個(gè)值,比如器件A、B之間的延遲為Ins,而這樣的要求往往由高速電路設(shè)計(jì)者提出,而由PCB工程師去實(shí)現(xiàn)。要滿足這個(gè)要求,就必須知道信號(hào)的傳播速度c但需要

2018-11-27 15:22:54

PCI-Clk,AGPCIK,IDE,DIMM等信號(hào)線。(2)若在一般普通PCB板中,除了具有濾波電感的作用外,還可作為收音機(jī)天線的電感線圈等等。如2.4G的對(duì)講機(jī)中就用作電感。(3)對(duì)一些信號(hào)布線長(zhǎng)度要求

2019-03-22 06:20:09

高速中的蛇形走線,適合在那種情況?有什么缺點(diǎn)沒(méi),比如對(duì)于差分走線,又要求兩組信號(hào)是正交的。回答:”蛇形走線,因?yàn)閼?yīng)用場(chǎng)合不同而具不同的作用:(1)如果蛇形走線在計(jì)算機(jī)板中出現(xiàn),其主要起到一個(gè)濾波電感

2019-05-09 07:35:35

差分走線,差分走線嚴(yán)格按照差分仿真所得出的結(jié)論,2S,和 3W 的要求進(jìn)行把控走線,其目的在于增強(qiáng)信號(hào)質(zhì)量的耦合性能,減少信號(hào)的回?fù)p。

2019-09-11 11:52:29

比如射頻走線或者一些高速信號(hào)線,必須走多層板外層還是內(nèi)層也可以走線

2023-10-07 08:22:18

Netl。 但是,對(duì)于高速信號(hào),如第3章所講的就完全不是這樣了,一個(gè)信號(hào)從引腳A輸出,到達(dá)D可能完全失真,而且也完全不考慮信號(hào)電流是如何返回的,所以需引入傳輸線的概念。傳輸線的原理在第3章已有詳細(xì)

2018-11-23 16:05:07

完整性問(wèn)題;3、蛇形線,滿足3W原則,高頻關(guān)鍵信號(hào)盡量不走蛇形線;4、盡量減少走線分叉,對(duì)于一驅(qū)多,走成菊花鏈來(lái)減少stub;5、控制過(guò)孔的數(shù)目,過(guò)孔呈容性,過(guò)多的過(guò)孔會(huì)導(dǎo)致信號(hào)完整性問(wèn)題;6、對(duì)于晶振

2020-12-21 09:23:34

AD中畫PCB板時(shí)過(guò)孔原則和線最短原則有沖突的時(shí)候,要遵循哪個(gè),求大神賜教

2019-08-26 01:37:16

時(shí),一般需要保持DP/DN在走線的過(guò)程中保持等距,保證一定的耦合程度,但是需要弄清楚的時(shí),等長(zhǎng)的優(yōu)先級(jí)是高于等距的。且在走線時(shí),線對(duì)之間要保持2W的距離。3、參考層MIPI走線應(yīng)該保持連續(xù)的參考層,且最好

2018-05-21 11:53:33

PCBLayout中的走線方法走線的好壞將直接影響到整個(gè)系統(tǒng)的性能,布線(Layout)是PCB設(shè)計(jì)工程師最基本的工作技能之一。大多數(shù)高速的設(shè)計(jì)理論也要最終經(jīng)過(guò)Layout得以實(shí)現(xiàn)并驗(yàn)證,由此可見

2010-03-16 09:23:41

為了保證良好的信號(hào)質(zhì)量, USB 2.0 端口數(shù)據(jù)信號(hào)線按照差分線方式走線。為了達(dá)到USB 2.0 高速 480MHz 的速度要求,建議 PCB 布線設(shè)計(jì)采用以下原則:差分?jǐn)?shù)據(jù)線走線盡可能短、直,差分?jǐn)?shù)據(jù)線對(duì)內(nèi)走線長(zhǎng)度嚴(yán)格等長(zhǎng),走線長(zhǎng)度偏差控制在±5mil 以內(nèi)。

2019-05-23 08:52:33

PCB Layout中的走線策略布線(Layout)是PCB設(shè)計(jì)工程師最基本的工作技能之一。走線的好壞將直接影響到整個(gè)系統(tǒng)的性能,大多數(shù)高速的設(shè)計(jì)理論也要最終經(jīng)過(guò)Layout得以實(shí)現(xiàn)并驗(yàn)證,由此可見

2009-08-20 20:58:49

,其產(chǎn)生的任何諸如電容,反射,EMI等效應(yīng)在TDR測(cè)試中幾乎體現(xiàn)不出來(lái),高速PCB設(shè)計(jì)工程師的重點(diǎn)還是應(yīng)該放在布局,電源/地設(shè)計(jì),走線設(shè)計(jì),過(guò)孔等其他方面。當(dāng)然,盡管直角走線帶來(lái)的影響不是很嚴(yán)重,但

2018-07-08 13:28:36

cadence PCB 怎么取消走線?***用過(guò),取消很容易,cadence沒(méi)發(fā)現(xiàn)這個(gè)功能!

2016-01-25 22:57:46

cadence pcb布線怎么實(shí)現(xiàn)3w原則的? 找不到規(guī)則設(shè)定的命令 求前輩指點(diǎn)一下

2016-01-25 22:48:42

PCB設(shè)計(jì)中,3W原則并不能完全滿足避免串?dāng)_的要求。按實(shí)踐經(jīng)驗(yàn),如果沒(méi)有屏蔽地線的話,印制信號(hào)線之間大于lcm以上的距離才能很好地防止串?dāng)_,因此在PCB線路布線時(shí),就需要在噪聲源信號(hào)(如時(shí)鐘走線)與非噪聲

2015-12-12 20:37:31

很多人對(duì)于PCB走線的參考平面感到迷惑,經(jīng)常有人問(wèn):對(duì)于內(nèi)層走線,如果走線一側(cè)是VCC,另一側(cè)是GND,那么哪個(gè)是參考平面?要弄清楚這個(gè)問(wèn)題,必須對(duì)了解傳輸線的概念。我們知道,必須使用傳輸線來(lái)分析

2014-11-17 10:07:29

要強(qiáng)制使用3W原則,而且還要進(jìn)行屏蔽地線包地處理,以防止串?dāng)_的發(fā)生。另外,不是所有的PCB上的走線都必須遵照3W布線原則。使用這一設(shè)計(jì)指導(dǎo)原則,在PCB布線前,決定哪些條走線必須使用3W原則是十分重要

2016-09-06 14:43:52

完整地平面相鄰,優(yōu)選兩地平面之間。原因:關(guān)鍵信號(hào)線一般都是強(qiáng)輻射或極其敏感的信號(hào)線,靠近地平面布線能夠使其信號(hào)回路面積減小,減小其輻射強(qiáng)度或提高抗干擾能力。原則3:對(duì)于單層板,關(guān)鍵信號(hào)線兩側(cè)應(yīng)該包地處

2018-11-23 16:21:49

布線(Layout)是PCB設(shè)計(jì)工程師最基本的工作技能之一。走線的好壞將直接影響到整個(gè)系統(tǒng)的性能,大多數(shù)高速的設(shè)計(jì)理論也要最終經(jīng)過(guò)Layout得以實(shí)現(xiàn)并驗(yàn)證,由此可見,布線在高速PCB設(shè)計(jì)中

2019-03-18 21:38:12

,阻抗不連續(xù),引起信號(hào)反射。為了減小不連續(xù)性,要對(duì)拐角進(jìn)行處理,有兩種方法:切角和圓角。圓弧角的半徑應(yīng)足夠大,一般來(lái)說(shuō),要保證:R>3W。銳角、直角走線銳角走線一般布線時(shí)我們禁止出現(xiàn),直角走線一般

2017-08-12 15:09:54

`表層走線與內(nèi)層走線更為規(guī)范的說(shuō)法應(yīng)該是微帶線與帶狀線。兩種走線方式因?yàn)榻橘|(zhì)和參考面不同,會(huì)存在比較明顯的差異。對(duì)于長(zhǎng)距離傳輸?shù)?b class="flag-6" style="color: red">高速信號(hào),尤其是背板之類的,需要特別注意損耗帶來(lái)的影響,避免高頻分量

2020-03-09 10:57:00

4x7628pp,滑片2mm板厚極限14層,1.6mm一般最多12層,做14層阻抗不易控制高速要求:信號(hào)層與地層盡量近電源與地盡量近,并有一處相鄰保證地平面足夠大,并完整保證相鄰的兩個(gè)信號(hào)層盡量遠(yuǎn),布線走線為交叉走線,盡量滿足3W規(guī)則,不行則相互錯(cuò)開信號(hào)層如果以VCC為參考平

2022-03-02 06:09:06

,相鄰走線間的影響就越小,走線間距盡量滿足3W原則。 2,使耦合長(zhǎng)度盡量短。相鄰傳輸線平行走線長(zhǎng)度越長(zhǎng)串?dāng)_越大,走線時(shí)候盡量減小相鄰線平行走線長(zhǎng)度;對(duì)于相鄰層走線盡量采用相鄰層垂直走線。 3,走線盡量

2014-10-21 09:51:22

利用高速FPGA設(shè)計(jì)PCB的要點(diǎn)及相關(guān)指導(dǎo)原則有哪些?

2021-04-25 08:17:55

通用的高速信號(hào)PCB設(shè)計(jì)處理原則有:(1)層面的選擇:處理高速信號(hào)優(yōu)先選擇兩邊是GND的層面處理(2)處理時(shí)要優(yōu)先考慮高速信號(hào)的總長(zhǎng)(3)高速信號(hào)Via數(shù)量的限制:高速信號(hào)允許換一次層,換層時(shí)加

2017-02-07 09:40:04

圖解在高速的PCB設(shè)計(jì)中的走線規(guī)則

2021-03-17 07:53:30

最近學(xué)習(xí)PCB布線,其他人的板子好像線與線之間距離能滿足3W原則,這個(gè)規(guī)則到底是在哪里設(shè)置的呢?

2016-01-09 20:50:03

~10mils),3W是夠了;但兩層板,走線與參考層高度距離(45~55mils),3W對(duì)高速信號(hào)走線可能不夠。3W原則一般是在50歐姆特征阻抗傳輸線條件下成立。3W原則是指多個(gè)高速信號(hào)線長(zhǎng)距離走線

2019-05-08 08:30:00

開關(guān)電源PCB布線原則及走線技巧

2019-03-06 11:43:16

在PCB設(shè)計(jì)中,布線是完成產(chǎn)品設(shè)計(jì)的重要步驟,PCB走線的好壞直接影響整個(gè)系統(tǒng)的性能,布線在高速PCB設(shè)計(jì)中是至關(guān)重要的。布線的設(shè)計(jì)過(guò)程限定高,技巧細(xì)、工作量大。PCB布線有單面布線、 雙面布線

2014-12-16 09:47:09

,一般電路應(yīng)盡可能使元器件平行排列,這樣不僅美觀,而且裝焊容易,易于批量生產(chǎn)。三、布線原則1、輸入輸出端用的導(dǎo)線應(yīng)盡量避免相鄰平行,最好加線間地線,以免發(fā)生反饋藕合。2、走線的寬度主要由導(dǎo)線與絕緣基板間

2020-08-01 07:54:14

網(wǎng)絡(luò),在多層的PCB走線的時(shí)候一旦產(chǎn)生了開環(huán)的結(jié)果,將產(chǎn)生線形天線,增加EMI的輻射強(qiáng)度。 圖3 開環(huán)規(guī)則 規(guī)則四:高速信號(hào)的特性阻抗連續(xù)規(guī)則 高速信號(hào),在層與層之間切換的時(shí)候必須保證特性阻抗

2018-09-20 10:38:01

設(shè)計(jì)的布線方向規(guī)則相鄰兩層間的走線必須遵循垂直走線的原則,否則會(huì)造成線間的串?dāng)_,增加EMI輻射。簡(jiǎn)而言之,相鄰的布線層遵循橫平豎垂的布線方向,垂直的布線可以抑制線間的串?dāng)_。規(guī)則六:高速PCB設(shè)計(jì)中的拓?fù)浣Y(jié)構(gòu)

2017-11-02 12:11:12

! j9 K# {: E 總的說(shuō)來(lái),直角走線并不是想象中的那么可怕。至少在GHz以下的應(yīng)用中,其產(chǎn)生的任何諸如電容,反射,EMI等效應(yīng)在TDR測(cè)試中幾乎體現(xiàn)不出來(lái),高速PCB設(shè)計(jì)工程師的重點(diǎn)還是應(yīng)該放在

2014-11-07 09:40:54

PCB長(zhǎng)距離走線和短距離加個(gè)過(guò)孔走線哪種走線更合理?

2019-09-25 22:11:32

AD18 ,PCB,走線,任意走線,在哪里設(shè)置?

2019-03-07 01:36:59

高速PCB布板原則,高速PCB布板原則。高速PCB布板原則。

2015-12-25 10:11:53 0

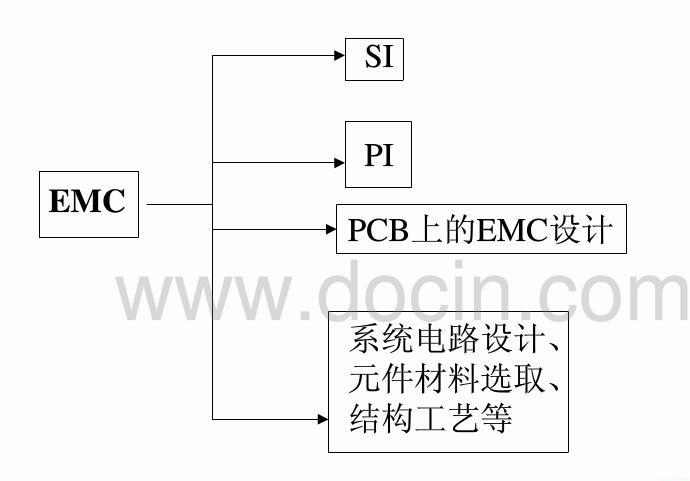

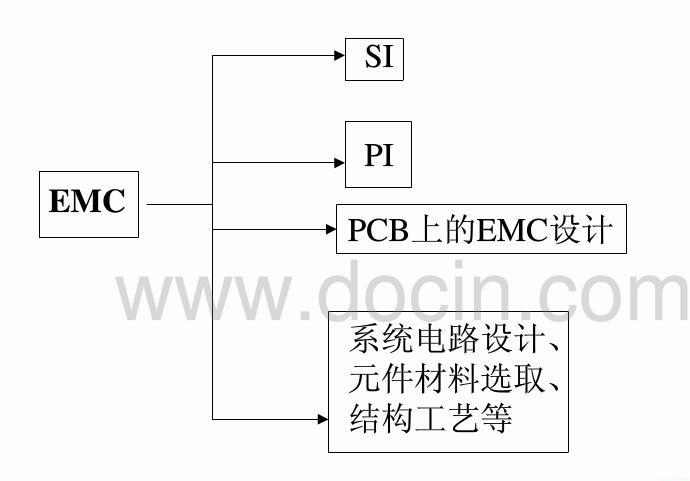

0 本文主要介紹了高速PCB的EMC設(shè)計(jì)原則,首先介紹了PCB設(shè)計(jì)的EMC基礎(chǔ)知識(shí),其次闡述了PCB中EMC設(shè)計(jì)的重要性以及PCB中EMC設(shè)計(jì)相關(guān)項(xiàng),最后詳細(xì)的介紹了關(guān)于高速PCB的EMC設(shè)計(jì)的47項(xiàng)原則,具體的跟隨小編一起來(lái)了解一下。

2018-05-25 15:58:19 4664

4664

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論