工程師設計電子產品時面臨的主要挑戰之一就是在不影響特性集的前提下減小系統尺寸。系統設計每一步驟都要考慮減小尺寸問題,從晶體管大小直到最終產品的尺寸,無不如此。不過,每一階段的小型化并非總能保持相同的特性集。有時,我們要把較少用到的屬性去除掉,從而節約芯片面積。如果特定的應用需要這些特性,那么工程師就不得不使用尺寸更大或者價格更高的芯片,這樣才能保留有關特性。不過,工程師通常可采用創新性的設計理念,讓低成本芯片發揮超出其基本功能之上的功能,從而實現所需的特性集要求。

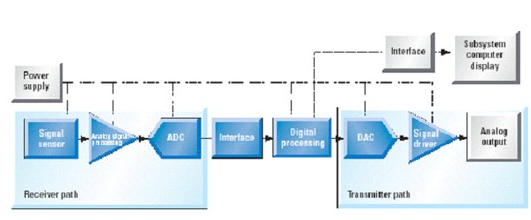

許多使用混合信號器件的應用(也稱作SoC器件),可將模擬信號轉換為數字信號,并在數字域或固件中執行操作。目前,市場上有多種面向需要有限模擬功能應用的SoC產品,比如只需要比較器和模數轉換器(ADC)的應用。考慮到最終結果在數字領域完成,因此通常不需要模擬輸出引腳。由于模擬輸出引腳需要模擬總線和模擬緩沖器來提供外部驅動功能,因此在不使用模擬輸出引腳的情況下,可以節約大量芯片面積。

就某些應用而言,即便所有信號處理都在數字領域進行,它們也仍然需要模擬參考電壓。例如,我們不妨設想這樣一個系統,其ADC范圍為0 ~ 5 V,輸入信號值為±20 mV。輸入信號不能直接用ADC測量,而是要用外部參考電壓向輸入信號添加DC偏置,將其轉化到ADC的范圍之內才行。測量結束后,偏置會由固件加以補償。由于模擬功能有限且不帶模擬輸出引腳,因此生成輸出模擬電壓參考是一個很大的挑戰。本文將介紹如何在不使用模擬輸出引腳的小型化芯片中只用一些外部無源組件來支持模擬電壓參考。

基本方法

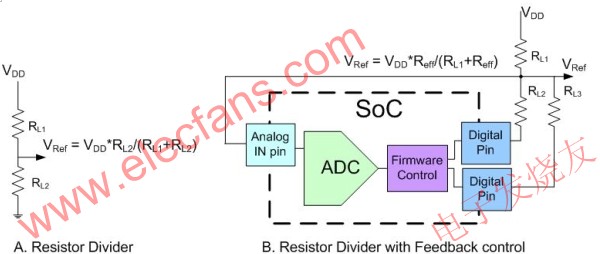

圖1:使用電阻分壓器電路的參考電壓。

每個系統都有可直接作為參考電壓或間接獲得其他電壓參考的供電電壓。如圖1a所示,電阻分壓器法是從供電電壓獲得電壓參考的基本方法。這種基本的電路不帶控制回路,其缺點在于參考電壓會直接與供電電壓的變動相關聯。

要想進行穩壓或獲得不同的電壓,我們可如圖1b所示向本電路添加控制回路。這樣,我們可以測量參考電壓并調節電阻,保持所需的參考值。電阻的一端連接到Vref節點,另一端則通過引腳加以控制。引腳可以接地,也可以為高Z。如果引腳接地,那么在有效電阻計算中要加入相應的電阻。如果引腳為高Z,則如同電阻未連接。

參考電壓根據并聯有效電阻 (Reff) 計算獲得,計算方程式如下所示:

如果應用不需要參考電壓,則所有引腳都可為高 Z,從而節省功率。我們可通過增加控制電阻的數量來提高控制分辨率,這進而也會增加引腳數量,形成電阻鏈控制。電阻鏈控制的概念可用來調節參考電壓,同時也能用來在不同時刻獲得不同的參考電壓。就穩壓而言,這種類型的控制只有在變化比控制延遲更慢時才能生效。

傳統的PWM-DAC方法

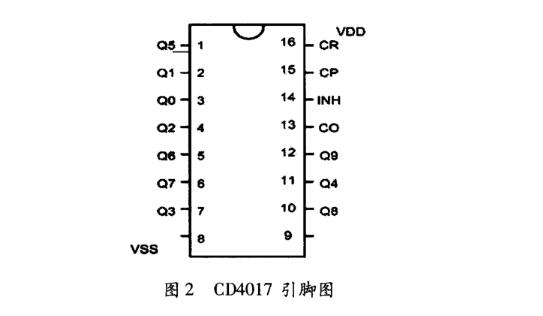

脈沖寬度調制—數模轉換器(PWM-DAC)是通過數字引腳獲得可編程參考電壓的最常見方法。PWM的輸出為數字信號,通過低通濾波,可獲得如圖2所示的平均DC值。低通濾波器截止頻率的選擇應確保其大大小于PWM的頻率輸出,以便盡可能接近DC值。

在上述方法中,參考電壓由PWM的供電電壓(Vdd)和負載周期(D)決定,計算方程式如下所示。如果供電電壓為5V,負載周期為50%,那么參考電壓就是2.5V。

脈沖寬度變動會改變Vref,不過由于PWM-DAC方法是一種開環系統,只有在供電電壓精度很高的時候才有優勢。如果供電電壓不準確,則輸出參考電壓也會不準確。獲得準確的供電電壓成本較高,因此對低成本系統來說是不適用的。為了補償供電電壓的變動,我們可用ADC和固件控制形成如圖2B所示的閉環系統。我們用ADC來檢測參考電壓值,并在固件中調節PWM的負載周期,從而獲得所需的參考值。這種反饋回路可減小對供電電壓的依賴,但會增大延遲,而且會占用更多系統資源。

自調整電壓參考

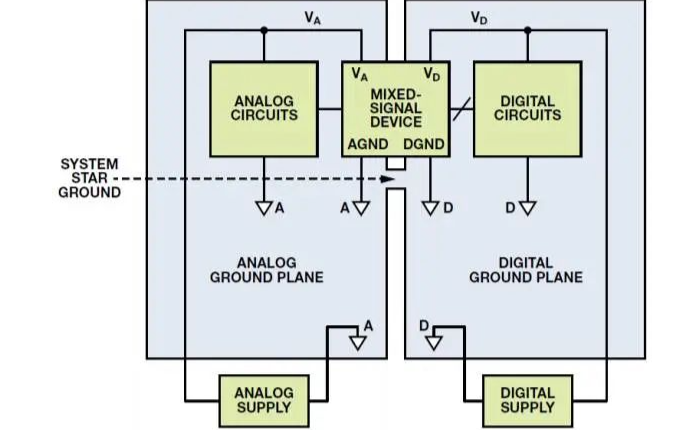

我們可以假定,盡管模擬組件數量有限,但SoC仍有內部參考電壓,自調整電路正由此產生。這在具有ADC的系統通常如此。這種方法是一種通過外部數字引腳獲得模擬電壓的技術。PWM-DAC方法建立在脈沖寬度調制的基礎之上,而這種方法則建立在脈沖密度調制(PDM)原理之上,其中數字信號的密度是信號為高時的百分比。具體而言,信號密度是指由“1”和“0”所構成的數字信號流中“1”所占的百分比。需要注意的是,具體的波形并不重要,只有信號為高的百分比才重要。在提供的參考材料中給出了關于密度信號處理的更多信息。

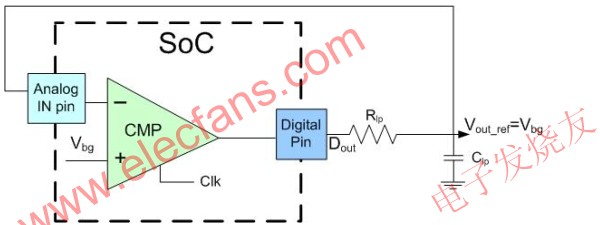

如圖3所示,電路使用SoC中的同步比較器和外部低通濾波器。低通濾波器的輸出為反饋,通過模擬輸入引腳傳遞到比較器的負輸入。使用該反饋的比較器遵循與運算放大器相同的原理,也采用電壓跟隨器模式。電壓跟隨器輸出將根據需要而改變,以保持其兩個輸入相同。如果正輸入上的值高于負輸入上的值,那么輸出就較高。高輸出將導致低通濾波器的輸出漂移較高,最終使得進入比較器的負輸入高于正輸入。如果負輸入較高,而輸出保持較低,則會讓負輸入下降。這樣,信號為高時的百分比(也就是信號密度)會發生變化,從而保持兩個輸入值相同。最終這會形成一個穩定狀態,實現輸出的自我調制,低通濾波器輸出上的密度結果為Vref = Vbg。由于比較器采用時鐘計時,因此輸出是一個明確定義的數字信號,經過低通濾波后可獲得DC參考電壓。

圖3:自調整電壓參考電路。

添加衰減器后可獲得除內部參考電壓(Vbg)之外的電壓。如果衰減器添加到輸出上,則能獲得小于Vbg的參考。如果衰減器添加到反饋中,就能獲得大于Vbg的參考。該衰減既可在模擬域,也可在密度域。

密度衰減

由于自調整電路的理念建立在PDM基礎之上,因此我們可向密度調制添加更多電路,以獲得主電路的不同體現。例如,如圖4A所示,我們可在比較器輸出和反饋信號之間添加密度調制器(本例中為PWM)。

圖4:自調整電路的實例。

放大器:如果PWM輸出的負載周期為50%,那么AND門輸出的有效密度就是此前的一半,這會讓負輸入值為低的時間翻一番,從而讓比較器輸出密度翻番。此外,比較器輸出的密度會根據PWM的負載周期發生變化。該數字密度信號經過低通過濾可獲得DC值,該值取決于內部帶隙參考電壓和PWM負載周期,其計算方程式如下所示:

這樣,我們就能獲得改變PWM負載周期的可編程電壓參考,而且避免了PWM-DAC方法的缺點。由于Dout2不能小于零,因此Vref2不能小于Vbg。

衰減器:如圖4B所示,我們可對同樣的組件進行重組,從而獲得小于參考電壓的電壓(即經過密度調制的衰減器)。通過這種方法,我們可由以下方程式獲得輸出:

模擬衰減

我們可用類似于電阻分壓器電路的電阻模擬衰減器來獲得模擬路徑上的衰減,從而得到參考電壓以外的電壓。

放大器:通過如圖4C所示添加模擬衰減器,自調整電路可用來獲得高于內部參考電壓的電壓(放大器)。參考電壓值的計算方程式如下所示:

衰減器:通過如圖4D所示添加外部電阻,自調整電路還可用來獲得低于內部參考電壓的電壓(衰減器)。參考電壓值的計算方程式如下所示:

緩沖器

在外部獲得兩個輸入的情況下,自調整配置中的比較器可用作緩沖器。緩沖器的準確度與參考電壓的準確度一樣。緩沖模式的方框圖與圖3所示相同,只不過內部參考電壓Vbg被外部輸入電壓所替換而已。

精確度和依賴性

用來從數字信號獲得DC值的低通濾波器決定著輸出信號的穩定時間和準確度。如果采用PWM-DAC方法,那么低通濾波器的極點必須根據PWM的頻率進行選擇;如果采用自調整方法,則必須根據比較器的時鐘頻率來選擇。如果低通濾波器的極點過高,Vout就不能達到穩定狀態值。以Fclk作為內部時鐘頻率,低通濾波器的具體要求可通過如下方程式計算獲得:

電阻鏈和PWM方法直接與供電電壓相關聯,而自調整參考電壓的變動則取決于帶隙電壓和比較器偏置的變動。

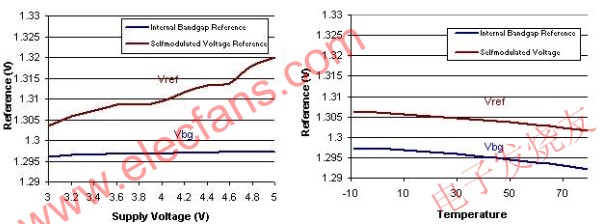

我們用賽普拉斯可編程片上系統(PSoC)構建了自調整電路的實施方案,并以此來收集性能數據。內部參考帶隙電壓和Vdd上外部獲得的參考電壓變動情況如圖5所示。該圖由通過收集采用最小型PSoC芯片CY8C21123所實施電路的數據繪制而成,該電路的平均比較器偏置電壓為8mV。從圖中可以看出,外部電壓參考對供電電壓的依賴取決于帶隙參考電壓變動和供電電壓的比較器參數(偏置)。

圖5:參考電壓隨供電電壓和溫度而產生的變化。

前兩種方法對溫度的依賴可以忽略。自調整電壓參考電路取決于帶隙電壓和溫度偏置差異。參考電壓隨溫度的變動情況如圖5所示。溫度變動幾乎完全隨Vbg變動。與溫度的變動相比,比較器的偏置等非理想參數與供電變化有較大不同。這會導致輸出參考電壓與內部參考電壓差異更大,具體差異為Vdd。

因為輸出的有效電阻不為零,所以上述所有方法的負載驅動功能均小于緩沖電壓輸出。在三種方法的驅動功能中,第一種方法最低。連接到該節點的電阻必須大大高于有效電阻 (Reff)。PWM-DAC的負載驅動功能與任何低通濾波器相同。

我們可通過理想的比較器來獲得自調整電路的負載驅動功能。反饋電阻器(低通濾波器電阻)(Rlp) 決定著電路的驅動功能。由于輸出會發生變動,以保持比較器的兩個輸入值相同,因此負載電阻會有以下限制,計算方程式如下:

本文介紹了模擬功能有限的芯片如何獲得模擬電壓參考值的方法。我們可在已將模擬功能用于其他目的的系統中采用上述方法,此外還能將不同的電路結合起來使用,從而獲得不同的電壓參考,進而提高靈活性和可編程性。

電子發燒友App

電子發燒友App

評論