本電路的AD1674工作在完全受控方式。A/D轉換為12位,而轉換后數據分兩次讀取,即先讀數據的高八位,后讀數據的低四位。

1.3.1 A/D轉換的啟動方式

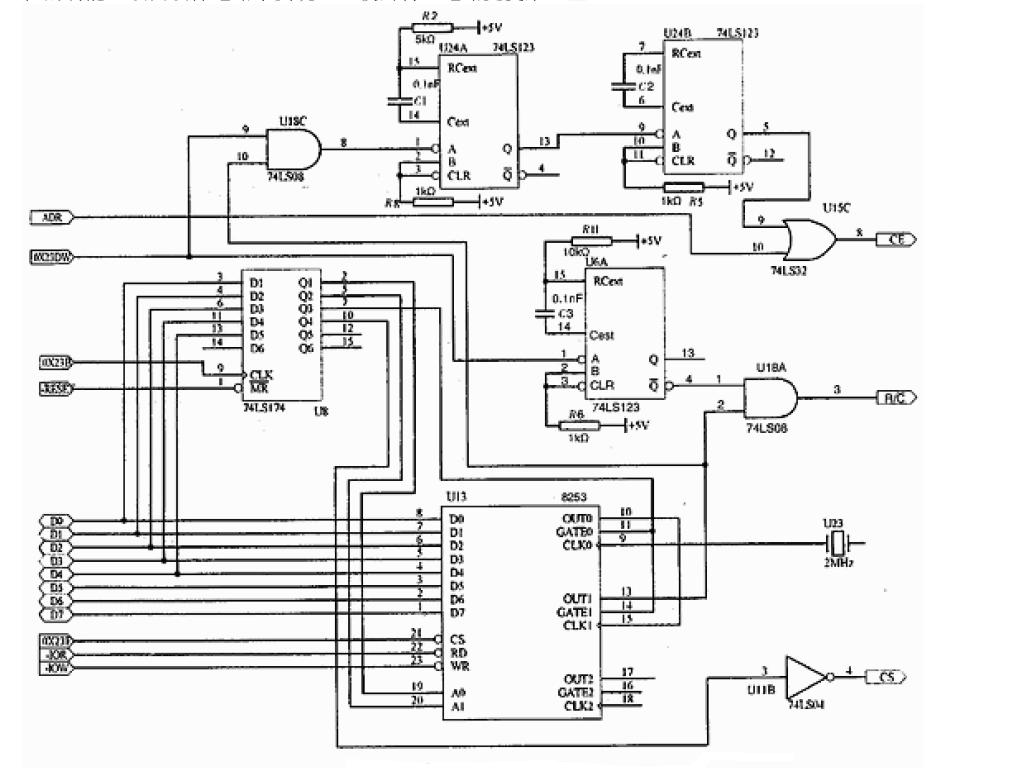

A/D轉換的啟動方式有兩種:8253定時器硬件啟動和寫端口軟件啟動。

8253定時器啟動方式應用于對數據采集的時隔要求準確的場合,該方式是利用8253的定時脈沖啟動A/D轉換,通過8253數據總線緩沖器(端口地址為&0X23F)輸出鑒別通道的計數初值,通過向6位鎖存器74LS174(端口地址為&0X23B)寫入控制字設定8253的控制字以及A/D片選控制位。6位鎖存器數據位定義說明如下:

A1A0=00:&0X23D口輸出的數據為計數器0的計數值。

A1A0=01:&0X23F口輸出的數據為計數器1的計數值。

A1A0=10:&0X23F口輸出的數據為計數器2的計數值。

A1A0=11:&0X23F口輸出的數據為計數器8253的方式字。

G0&G1=1:起動計數器0和計數器1;G0&G=0:禁止計數器0和計數器1。

CS=1:選中A/D芯片CS=0;不選中A/D芯片。

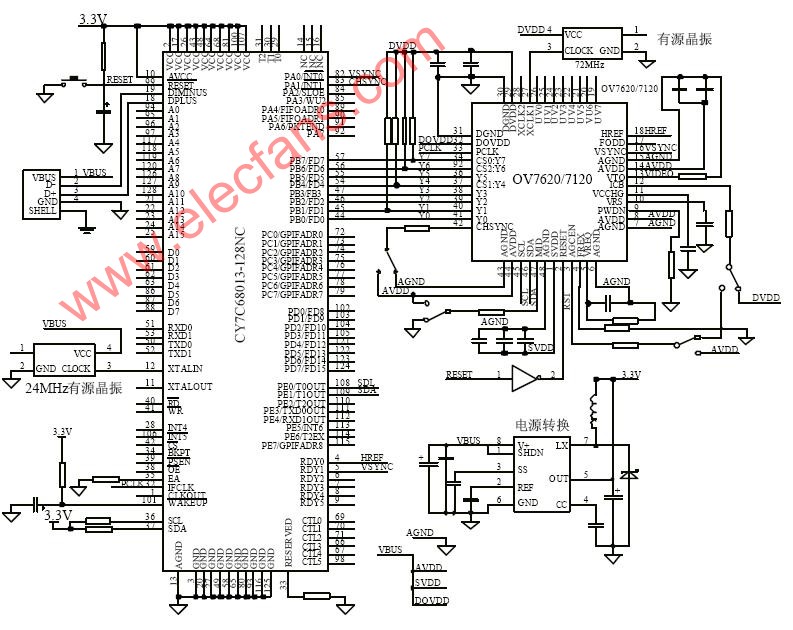

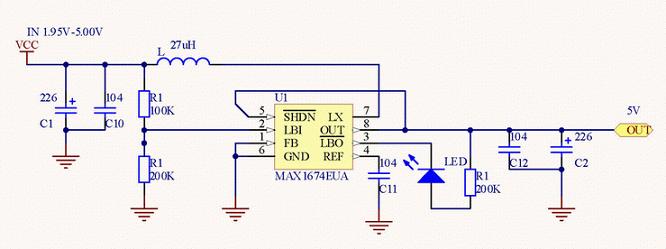

具體的實現電路如圖2所示。首先將8253定時通道0與通道1串聯起來定時,通道0的時鐘輸入CLK0的頻率是2MHz,工作在方式3(方波比率發生器)下,通道0的輸出OUT0為頻率1MHz的方波,作為通道1的輸入時鐘CLK1。通道1設定為方式2,即通道1的輸出OUT1從輸出開始一直維持高電平,計數回零后,輸出為低電平并自動重新裝入原計數值,低電平維持一個時鐘周期后,輸出恢復高電平并重新作減法計數。輸出OUT1分為兩路信號,一路通過與門U18A輸出,作為AD1674的R/C控制信號;另一路經過單穩觸發器U24延時和調節定時寬度后,再通過或門U15C輸出作為AD1674的CE控制信號。當OUT1輸出寬度為1μs的低電平脈沖時,一方面使控制信號R/C的轉換有效,同時經延時和調節定時寬度后,使A/D的使能控制CE開始啟動A/D轉換。因此在裝入計數初值以后,只要設置6位鎖存器U8的控制字,就可利用8253定時器啟動A/D。

寫啟動A/D方式應用于軟件定時,即通過對端口(地址為&0X23D)寫來觸發A/D轉換。如圖2所示,端口寫信號一方面經過單穩觸發器U6A調節定時寬度(寬度為1μs)后,作為AD1674的R/C控制信號,同時經過另一單穩觸發器U24延時和調節定時寬度后,再通過或門U15C輸出作為AD1674的CE控制信號。

可見兩種啟動A/D轉換的過程相似。相比較而言,前者的采樣間隔是由8253定時脈沖的周期決定的,屬于可編程定時器方式定時,共特點是采樣間隔準確;后者則由相鄰兩次寫端口(地址為&0X23D)的時間差決定采樣間隔,為軟件定時方式,特點是靈活方便。

1.3.2 A/D轉換數據的讀取方式

在數據采集系統中,計算機讀取A/D轉換數據的方式一般有三種,即查詢、中斷和DMA方式。其中查詢方式就是通過查詢標志位來判斷A/D是否轉換完畢,如果A/D轉換完畢則讀入轉換的數據。這種方式下CPU主動查詢,通過CPU讀取A/D轉換的數據,故實現的硬件電路簡單,但數據讀取速度慢,同時在WINDOWS的多任務執行方式下,存在著A/D轉換數據不能及時讀入的問題。中斷方式是利用A/D轉換完畢的標志位觸發一硬中斷,然后中斷管理器向CPU提出中斷申請。在中斷允許的情況下,執行中斷服務程序讀入轉換的數據。這種方式實現的硬件電路也比較簡單,但中斷服務程序的介入,引起數據采集程序的斷點的不可預測性,這樣會導致數據采集程序的失控。DMA方式利用A/D轉換完畢的標志位向DMA控制器提出DMA申請,當DMA控制器從CPU取得總線控制權時,接口便與內存之間直接地進行數據交換(不經過CPU)。這種方式下,由于不經過CPU讀入數據,故提高了數據傳輸速度。同時由于A/D轉換器主動申請數據傳輸,而DMA申請比外設中斷申請的優先級高,A/D轉換數據能夠及時讀入,系統性能也得到了提高,但實現的硬件電路較前兩種方式復雜。

本電路設計有查詢、中斷和DMA三種數據傳輸方式。通過一撥碼盤開關來選擇不同的的傳輸方式。如圖3所示,當A/D轉換完畢時,標志位STS由高電平變為低是電平,從而引起D觸發器U20A觸發,U20A的輸出Q由低電平變成高電平。當撥碼盤開關S1選擇為查詢方式時,該U20A的輸出Q通過一個三態門(端口地址為&0X23F)與數據線D6相連,提供計算機查詢;在中斷方式下,該U20A的輸出Q直接與硬中斷引腳IRQ2相連,當Q由低電平變成高電平時,引起計算機中斷。在前兩種方式下,通過軟件編程,向一鎖存器U22的最低位寫入0或1,選擇讀取A/D轉換數據的高八位或低四位,且由專門的端口(地址為&0X23D)讀取A/D轉換的數據。實現的硬件電路簡單。而在DMA方式下,通過應答信號DACK1尋址,并不由專門的端口讀取A/D轉換的數據,故選擇A/D轉換數據的高八位或低四位的功能必須由硬件電路來實現,比較而言,電路更復雜一些。

?

下面介紹DMA方式下的具體實現電路。DMA請求電路由兩個D觸發器組成,當A/D轉換完畢時,U20A的輸出Q由低電平變成高電平,DRQ1=1,DMA通道1發出請求,DRQ1被認可后進行兩次DMA傳輸。在第一次DMA傳輸期間,觸發器U20B的輸出Q為低電平,A/D轉換數據的高八位傳輸到指定內存單元。在第一次DMA傳輸結束時,DACK1由低電平變成高電平,觸發器U20B的輸出為高電平,但觸發器U20A的輸出Q仍然是高電平,該電平申請第二次DMA傳輸。在第二次DMA傳輸期間,觸發器U20B的輸出為高電平,A/D轉換數據的低四位傳輸到指定的內存單元。當第二次DMA傳輸結束時,DACK1由低電平變成高電平,使觸發U20B輸出低電平,同時觸發器U20A的輸出Q變為低電平,DRQ1=0變為低電平,DRQ1=0,DMA通道1的請求被撤銷,結束一次A/D轉換12位數據傳輸過程。

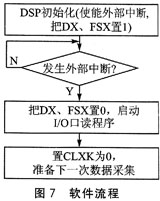

2 軟件設計

該接口電路支持各種帶有口指令操作的高級語言和8086/8088匯編語言。以下就以Turbo C為例對相應的部分編程,經供參考。

2.1 A/D編程

該編程適合于中斷或查詢方式下的編程,端口地址=0x238~0x23f。

outportb(0x23c,0x00); /*初始化清零*/

outportb(0x23a,0x00); /*選擇傳輸高8位數據并為A/D轉換作準備*/

{

}; /*啟動A/D并檢查A/D是否轉換完畢*/

dh=inportb(0x23d); /*輸入高八位數據*/

outporth(0x23a,0x01); /*選擇傳輸低四位數據*/

dl=inportb(0x23d); /*輸入低四位數據*/

outportb(0x23a,0x00); /*選擇傳輸高8位數據并為A/D轉換作準備*/

dl=dl>>4;

dh1=dh;

dl=(dh1<<4)+dl;

dh=dh>>4; /*將高八位低四位數據轉化為高四位低八位數據*/

d=dh*256+dl; /*拼合12位數據*/

u=(d-2047)*10.0/4096; /*轉換電壓值*/

2.2 寫啟動和查詢方式的編程

outportb(0x23d,0x00); /*寫啟動A/D轉換*/

if(inporth(0x23e)&0x80);/*D7=1則A/D轉換完畢*/

電子發燒友App

電子發燒友App

評論