采樣保持電路圖設(shè)計(jì)(三)

lf398峰值采樣保持電路

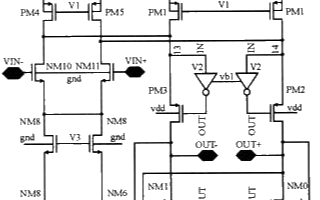

1.lf398的峰值保持電路

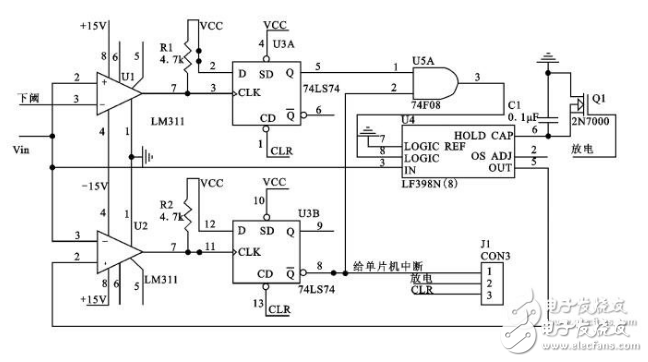

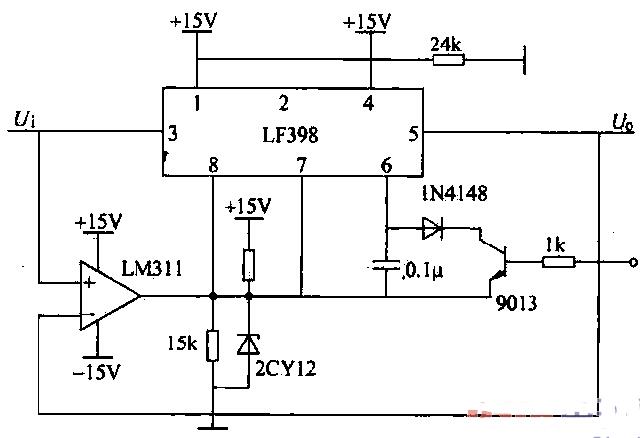

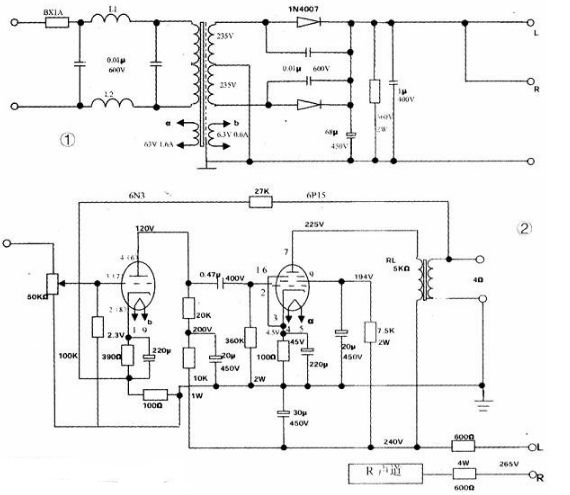

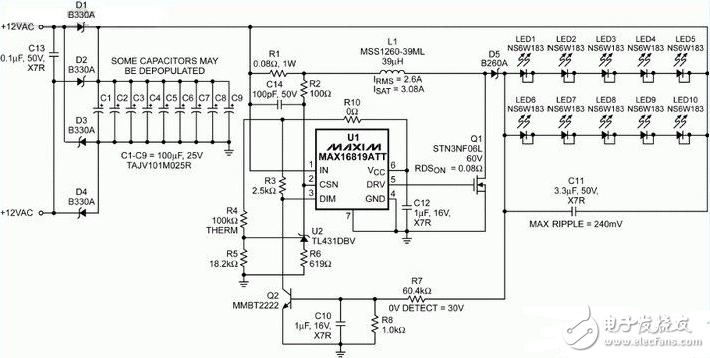

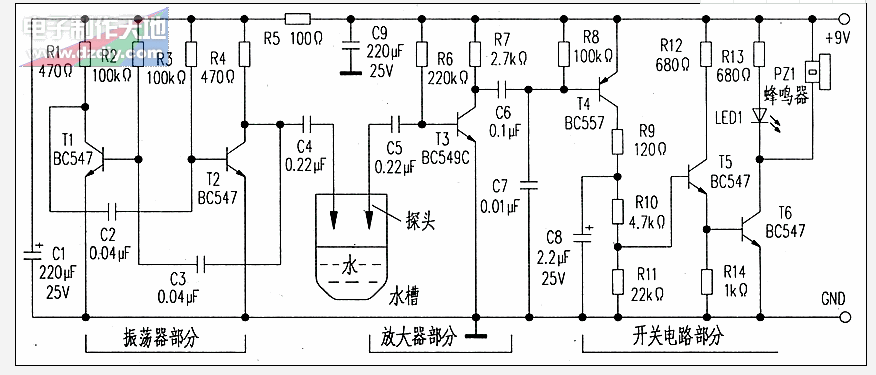

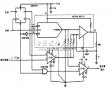

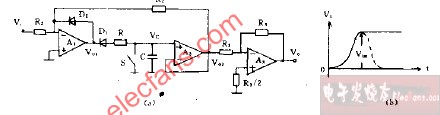

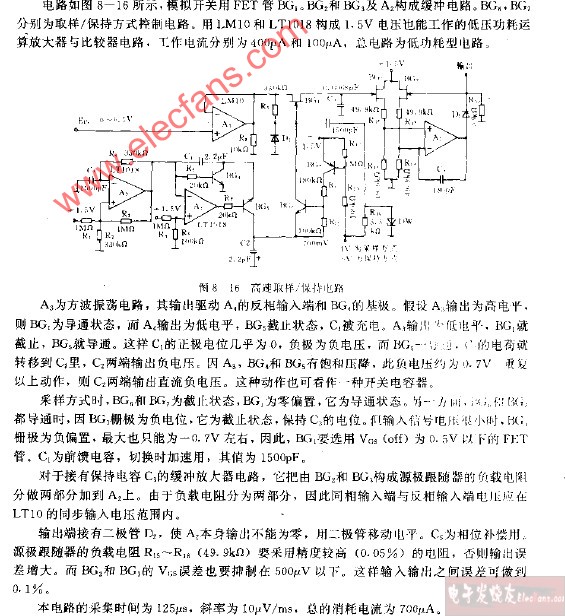

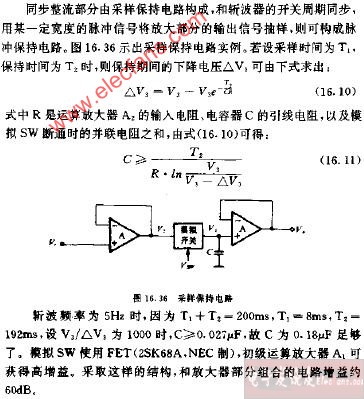

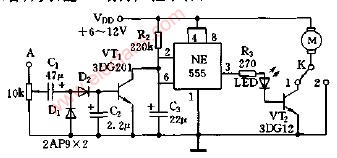

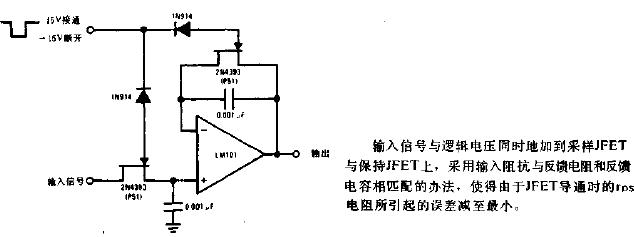

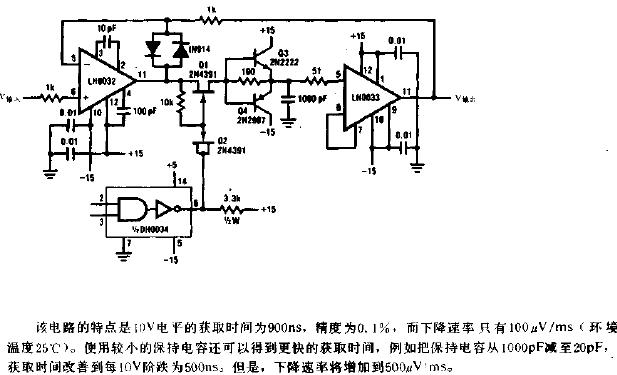

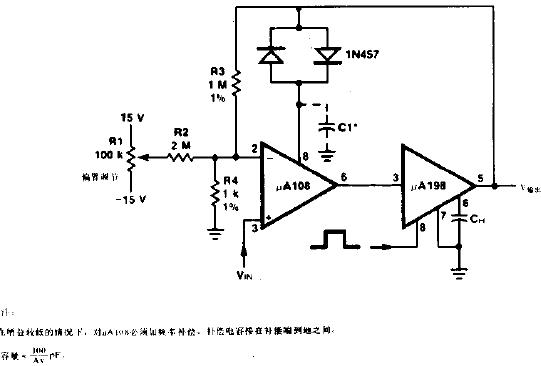

圖1:峰值保持電路原理圖

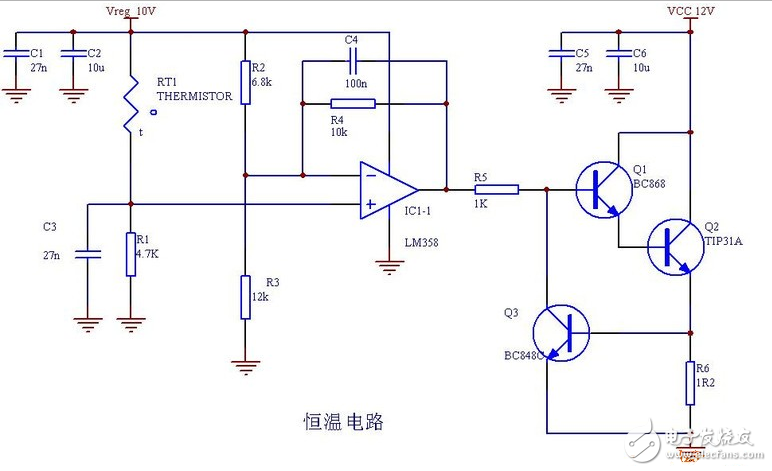

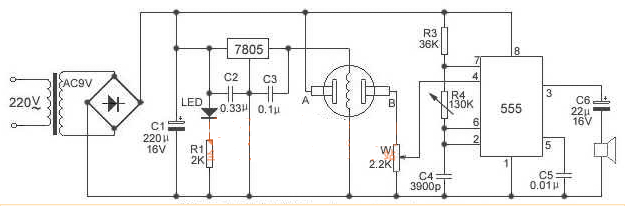

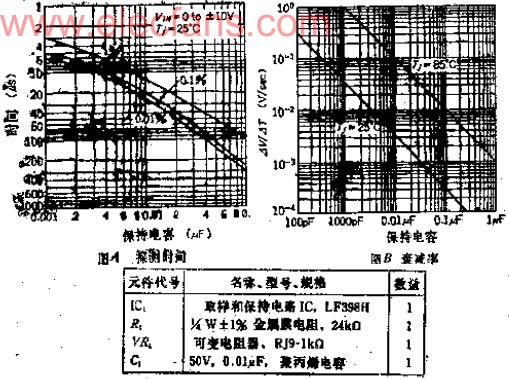

峰值保持電路探測(cè)核脈沖幅度信號(hào)并在脈沖峰值時(shí)刻通知保持峰值,同時(shí)向單片機(jī)提出中斷申請(qǐng)信號(hào),使單片機(jī)響應(yīng)中斷啟動(dòng)A/D轉(zhuǎn)換;轉(zhuǎn)換結(jié)束后單片機(jī)使采樣保持器復(fù)原為采樣狀況,實(shí)現(xiàn)系統(tǒng)的邏輯控制。峰值保持電路原理圖如圖1所示。U4是芯片LF398,它是美國國家半導(dǎo)體公司研制的集成采樣保持器。它只需外接一個(gè)保持電容就能完成采樣保持功能,其采樣保持控制端可直接接于TTL,CMOS邏輯電平。

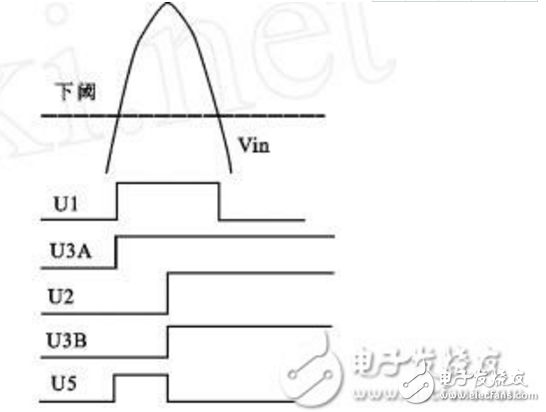

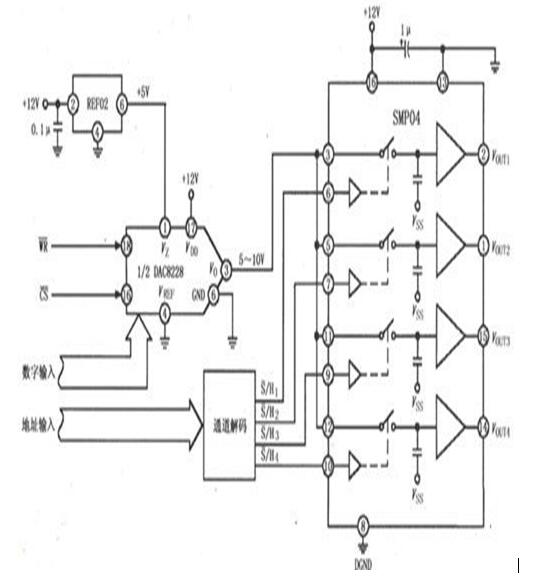

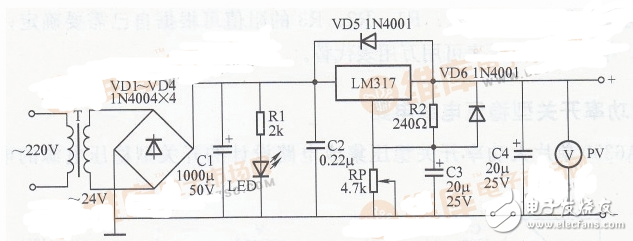

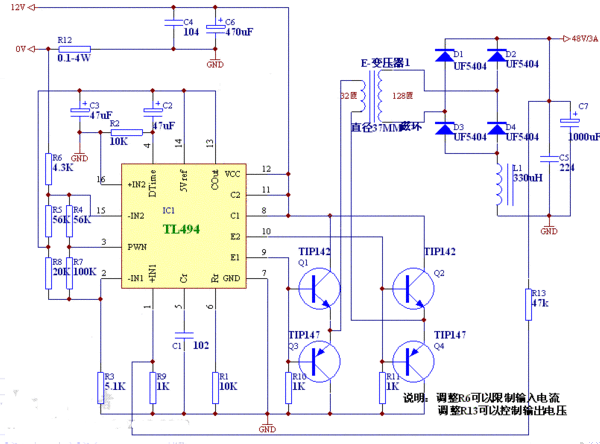

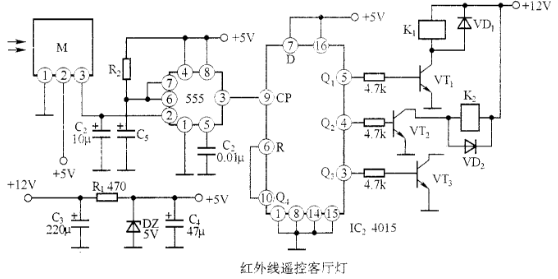

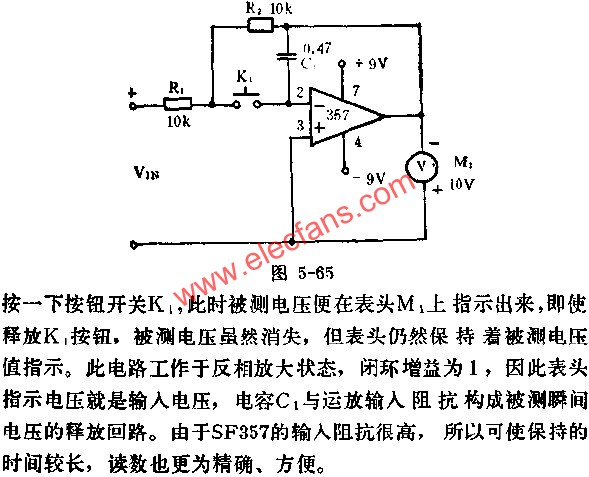

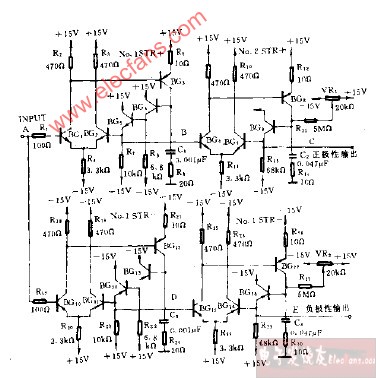

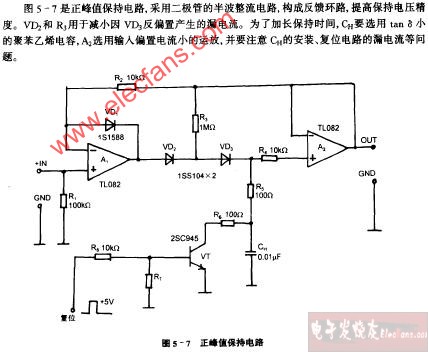

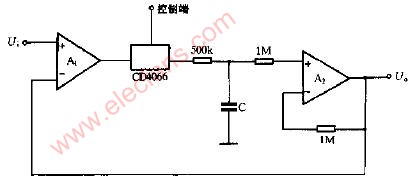

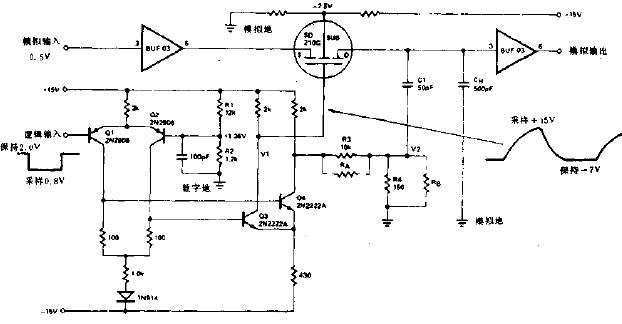

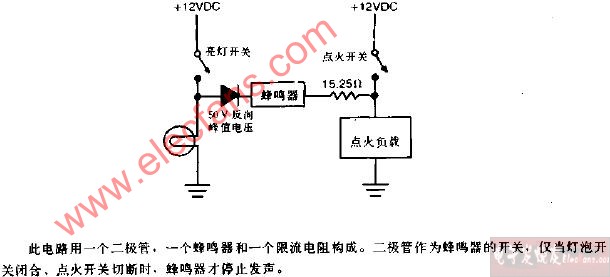

圖2

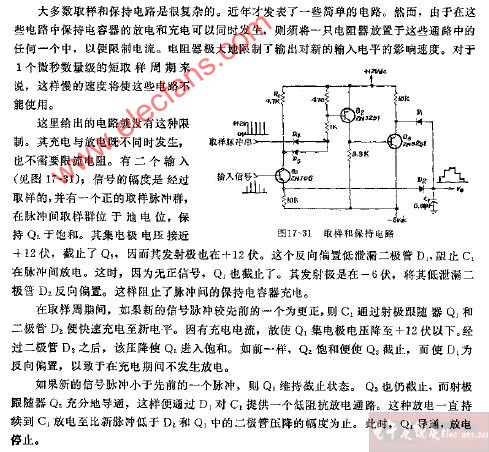

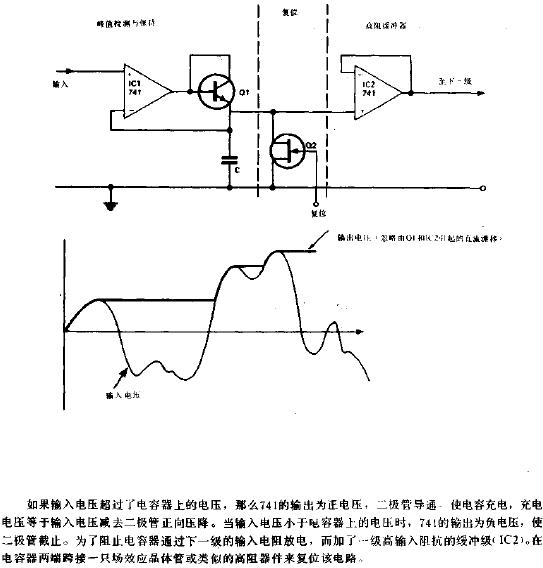

U1和U2是比較器LM311,U3是D觸發(fā)器74LS74,U5A是與門74LS08。放大后的脈沖核信號(hào)一路輸入到下閾比較器,另一路接輸入到LF398。當(dāng)核信號(hào)大于下閾時(shí),比較器U1輸出高電平,得到上升沿,上升沿再觸發(fā)U3A,它的Q端輸出高電平和U3B的Q非端相與得到高電平,去控制LF398的采樣控制端進(jìn)入采樣狀態(tài)。當(dāng)LF398的輸出端信號(hào)幅度比輸入端大時(shí),即到達(dá)峰值時(shí),比較器U2出高電平,得到上升沿,上升沿再觸發(fā)U3B,它的Q非端輸出低電平,U5A輸出變?yōu)榈碗娖剑琇F398進(jìn)入保持狀態(tài)。U3B的Q非端輸出的下跳沿作為單片機(jī)的中斷信號(hào),當(dāng)A/D轉(zhuǎn)換結(jié)束后,單片輸出放電和清零CLR信號(hào)使采樣保持器復(fù)原。電路波形見圖2。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論