濾波器和接口設計程序

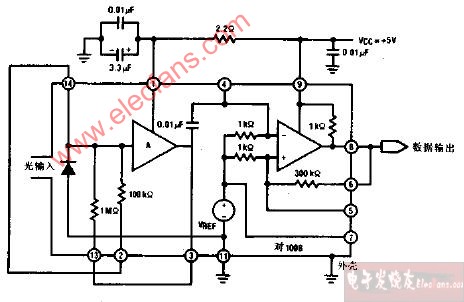

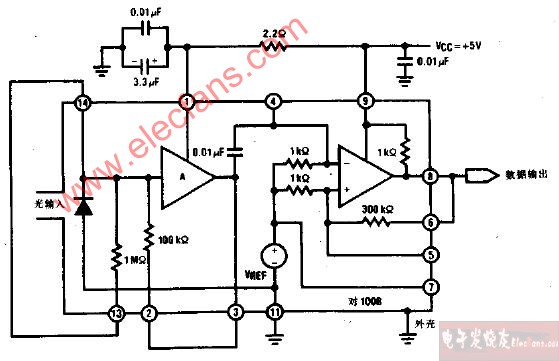

本節介紹放大器/ADC與濾波器接口設計的常用方法。為了實現最佳性能(帶寬、SNR、SFDR等),放大器和ADC應對一般電路形成某些設計限制:

放大器應參考數據手冊推薦的正確直流負載,以獲得最佳性能。

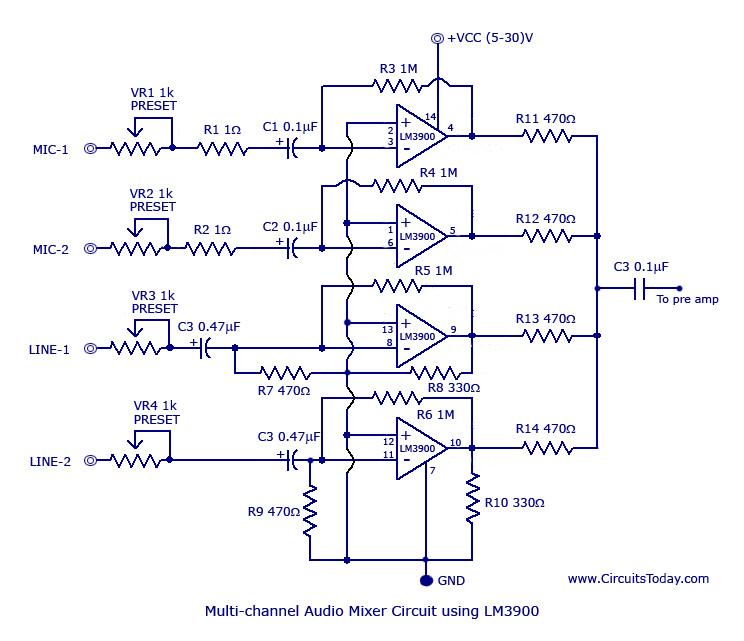

放大器與濾波器的負載間必須使用正確數量的串聯電阻。這是為了防止通帶內的不良信號尖峰。

ADC的輸入應通過外部并聯電阻降低,并使用正確串聯電阻將ADC與濾波器隔離開。此串聯電阻也會減少信號尖峰。

此設計方法傾向于利用大多數高速ADC的相對較高輸入阻抗和驅動源的相對較低阻抗,將濾波器的插入損耗降至最低。

設計程序的詳情請參見電路筆記 CN-0227 和 CN-0238。

電路優化技術和權衡

本接口電路內的參數具有高互動性;因此優化電路的所有關鍵規格(帶寬、帶寬平坦度、SNR、SFDR、增益等)幾乎不可能。不過,通過變更RA和RKB,可以最大程度地減少通常發生于帶寬響應內的信號尖峰。

ADC輸入端的串聯電阻(RKB)應選擇為盡量減少任何殘余電荷注入(從ADC內部采樣電容)造成的失真。增加此電阻也傾向減少帶內的信號尖峰。

不過,增加RKB會增加信號衰減,因此放大器必須驅動更大信號才能填充ADC的輸入范圍。

優化通帶平坦度的另一方法是略微變更濾波器分流電容。

ADC輸入端接電阻(2RTADC)通常應選擇為使凈ADC輸入阻抗介于200 Ω和400 Ω之間。降低該電阻可減少ADC輸入電容的效應并穩定濾波器設計,但會增加電路的插入損耗。提高該值也會減少信號尖峰。

上述因素的權衡可能有些困難。本設計中,每個參數權重相等;因此所選值代表了所有設計特征的接口性能。某些設計中,可根據系統要求選擇不同值,以優化SFDR、SNR或輸入驅動電平。

本設計中的SFDR性能取決于兩個因素:放大器和ADC接口元件值,如圖1所示。表1和圖5所示的最終SFDR性能數字是在優化濾波器設計后獲得的,考慮了用于濾波器設計的板寄生電容和非理想元件。

該特定設計中可以權衡的另一因素是ADC滿量程設置。對于采用本設計獲得的數據,滿量程ADC差分輸入電壓設置為1.75 V p-p,它可以優化SFDR。將滿量程輸入范圍更改為2.0 V p-p可稍稍改善SNR,但SFDR性能會略微降低。沿相反方向將滿量程輸入范圍更改為1.5 V p-p可稍稍改善SFDR,但SNR性能會略微降低。

請注意,本設計中的信號與0.1 μF電容進行交流耦合,以阻擋放大器、其端接電阻和ADC輸入之間的共模電壓。共模電壓的詳情請參見AD6657A數據手冊。

無源元件和PCB寄生考慮因素

該電路或任何高速電路的性能都高度依賴于適當的PCB布局,包括但不限于電源旁路、受控阻抗線路(如需要)、元件布局、信號布線以及電源層和接地層。高速ADC和放大器PCB布局的詳情請參見教程MT-031和MT-101。

低寄生表面貼裝電容、電感和電阻應用于濾波器內的無源元件。所選電感來自Coilcraft 0603CS系列。濾波器所用表面貼裝電容的穩定性和精度是5%、C0G、0402型。

系統的完整文檔請參見CN-0259設計支持包(CN0259-DesignSupport)。

常見變化

針對需要更少帶寬和更低功耗的應用,可使用ADL5562差分放大器。 ADL5562的帶寬為3.3 GHz。如需更低的功耗和帶寬,還可使用 ADA4950-1。該器件的帶寬為1 GHz,僅使用10 mA的電流。

電子發燒友App

電子發燒友App

評論