本文依據(jù)IEC TR 62380中集成電路的可靠性預測數(shù)學模型,對ISO 26262-11:2018中的案例進行推算,方便讀者對這一預測模型的了解;本文為IEC TR 62380介紹的上半部分,著重介紹IC Die失效率的三種計算方法,希望為功能安全硬件開發(fā)人員提供一定的幫助。

IEC TR 62380《電子組件、PCBs和設備的可靠性預計通用模型》是涵蓋電路、半導體分立器件、光電組件、電阻器、電容器、壓電組件、顯示器、開關等等電子元器件的可靠性預計模型,模型中包含了環(huán)境系數(shù)以及材料、工藝和結構等因素相關的系數(shù)。并將mission profile 溫度變化的影響放入模型中予以考慮。

ISO 26262-11:2018在進行失效率分析也推薦使用這一標準,本文將通過ISO 26262中的例子來介紹這一預測模型。

1.IEC TR?62380中可靠性預測的計算

?

?

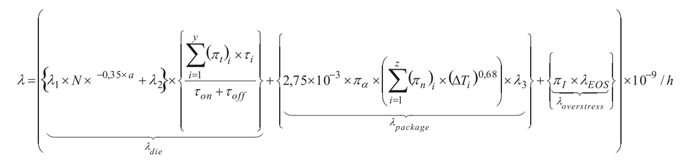

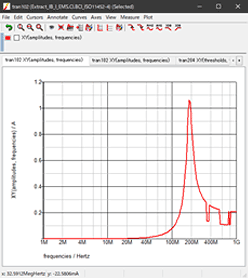

圖1?IEC TR 62380的可靠性預測數(shù)學模型

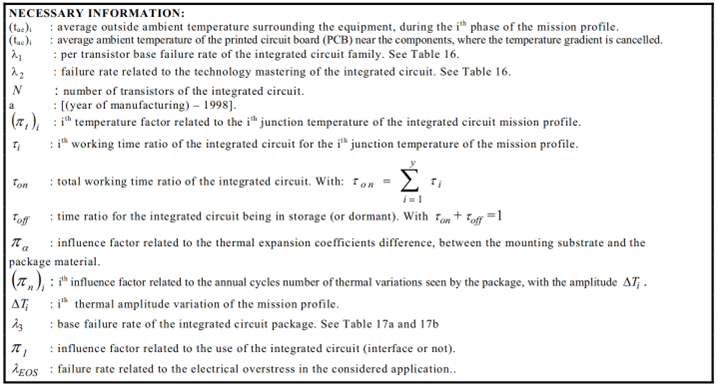

圖2 參數(shù)介紹

表1 參數(shù)介紹

以上為IEC TR 62380里的內容介紹,感興趣的同學可以去讀一下標準第七章:‘Integrated circuits’,標準里有一個例子,可以推算一下,驗證一下預測模型。

觀察IEC TR 62380的可靠性預測數(shù)學模型可以發(fā)現(xiàn):整個數(shù)學模型由如下3部分組成:

λdie組件失效率

λpackage封裝失效率

λoverstress電過應力失效率

下面將對組件Die失效率計算的三種方法予以介紹。

2.ISO 26262中的λdie計算

IEC TR 62380中的計算例子針對的是單一類型電路的計算,對芯片來說是遠遠不夠的,如何考慮包含2種及以上的電路類型的情況呢?

λ1表示的每個晶體管的失效率,只有電路類型有關;而λ2的值不受晶體管數(shù)量的影響,是使用的工藝相關的參數(shù),一般在較大規(guī)模的芯片芯片產品可靠性計算時,λ2只參與一次計算,每種電路都有專門的λ2,在計算包含多種類型電路的芯片λ2,base時面臨如何正確處理λ2的問題;因此在ISO 26262-11中基于IEC TR 62380提出了3個包含多種電路類型的情況的λdie計算方法。

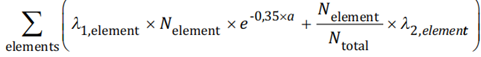

加權平均法

加權平均法:指的是根據(jù)每種電路的等效晶體管數(shù)量,通過加權平均的方式來計算對應的base失效率,計算模型參考ISO 26262-11:Equation (1):主要分成2部分,公式的左邊是不同的電路類型的基礎失效,后邊為集成電路在任務剖面(Mission profile)下的影響系數(shù)(受工作溫度及對應的時間占比影響)。

圖3 加權平均法的計算模型

已知一個CMOS的MCU、冷卻方式為自然對流、溫度剖面為“motor control”、結溫溫升26.27 C、PQFP 144引腳封裝、包含50k CPU和16kB SRAM;參考ISO 26262-11及相關內容描述。

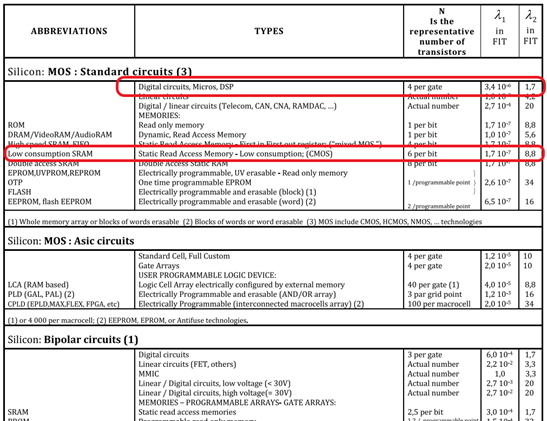

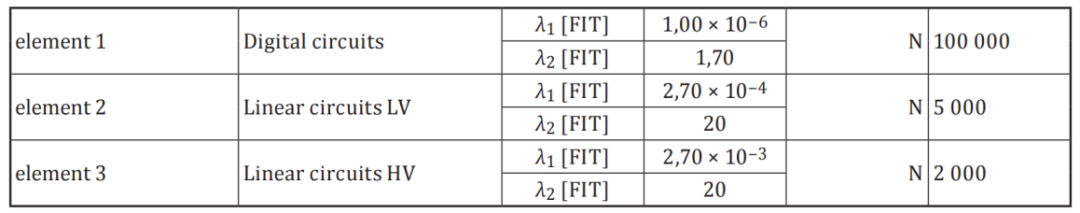

λ1和λ2的選取

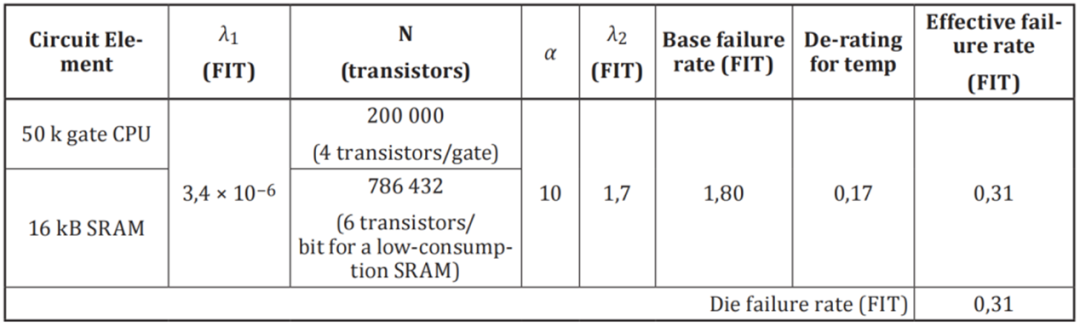

根據(jù)輸入的CPU、SRAM電路類型,查詢ISO 26262-11:Figure 10;即下圖,相應的參數(shù)選擇已標注:

圖4?λ1/2的參數(shù)選擇

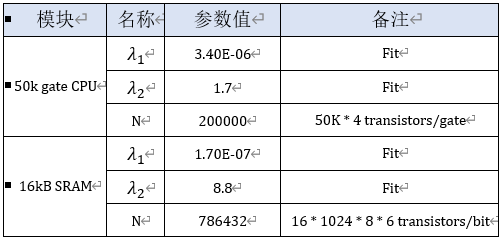

表2?λ1/2的選值和晶體管的數(shù)量

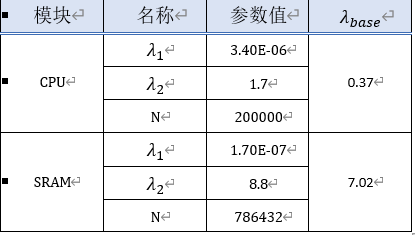

λbase失效率的計算

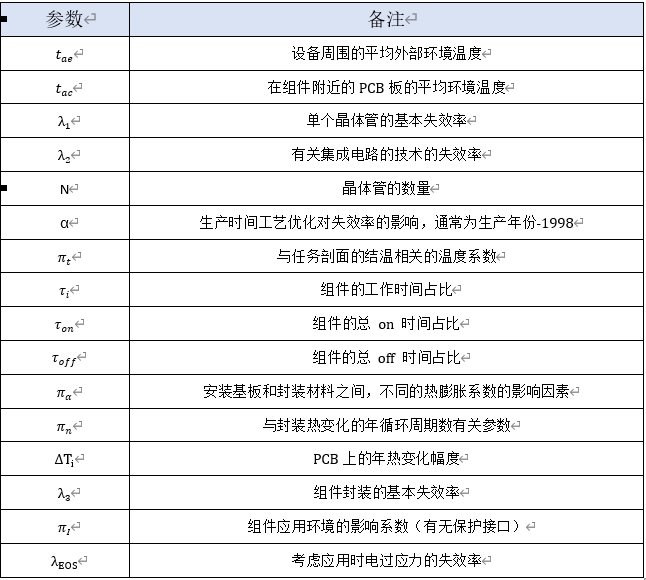

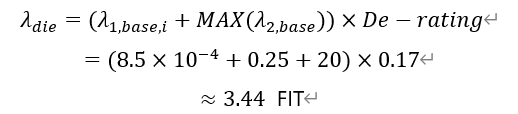

λbase的數(shù)學模型如下:

圖5?λbase的數(shù)學模型

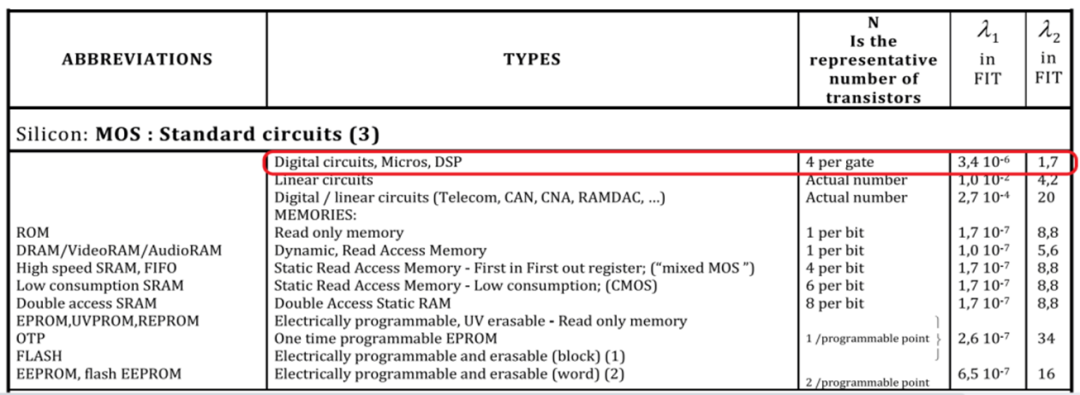

代入CPUSARM的的選值和晶體管的數(shù)量,得:

表3

溫度De-rating系數(shù)的計算

溫度De-rating系數(shù)用來評估工作環(huán)境溫度對組件Die失效率的影響大小,在這里由于篇幅問題,就不做詳細計算,直接引用Per calendar hour計算結果0.17,計算過程見之后的文章:《Mission profile的使用》。

λdie的計算

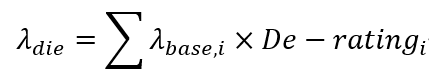

將基礎失效率和溫度De-rating系數(shù)代入:

表4

保守法

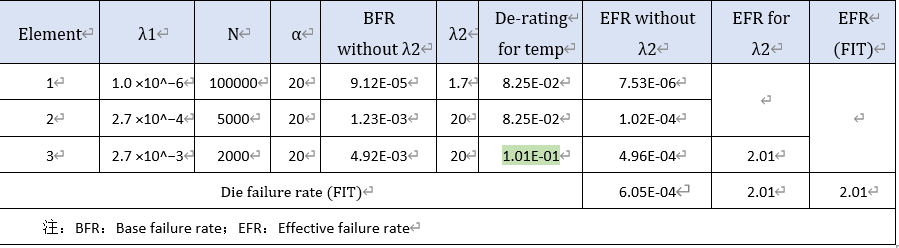

保守法:指的是選取電路類型中最大的值以及最大溫度De-rating系數(shù)計算λ2對應的base失效率,計算模型參考ISO 26262-11:Equation?(2):

圖6 保守法的計算模型

例1

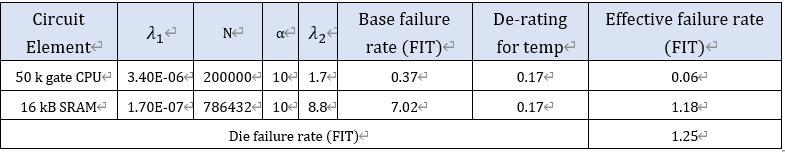

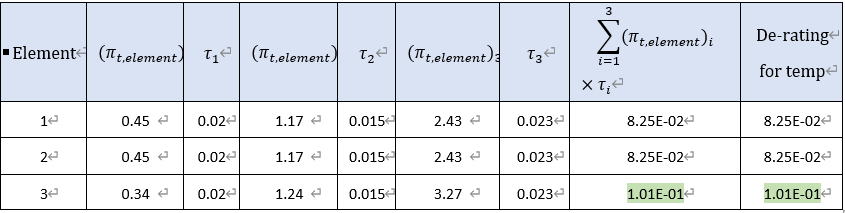

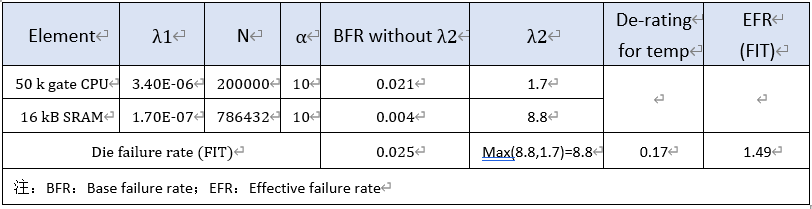

參考ISO 26262-11:Table 3,這個例子沒有進行詳細的分步計算,表格中已經列出了各個階段的結果值,供讀者理解保守法的計算模型:

圖7 ISO 26262 Part11:Table 3

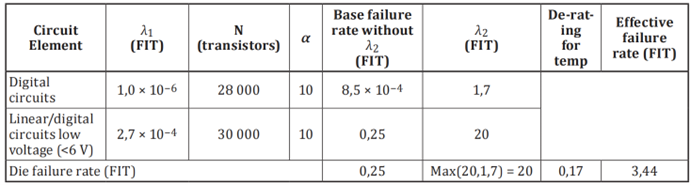

計算過程如下:

經過上面的計算我們知道Base失效率要乘以溫度De-rating系數(shù)才能得到最終的實際有效結果,在例1中選取了最大的λ2和溫度De-rating系數(shù)0.17進行計算;但是如果電路的溫度De-rating系數(shù)不相同呢?ISO 26262-11:Table 4及計算過程給出了答案。 ? ?

例2

參考ISO 26262-11:Table 4;輸入條件如下:

Mission profile仍然是“Motor Control”;

生產年份是2018年,因此 α 的值為20;

Step 1:?λ1和λ2的選取

ISO 26262-11:Table 4中直接列出了3種element對應的和,因此不需要查表。

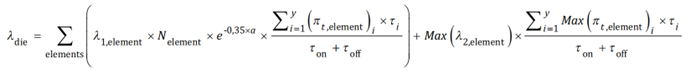

圖8 ISO 26262 Part11:Table 4

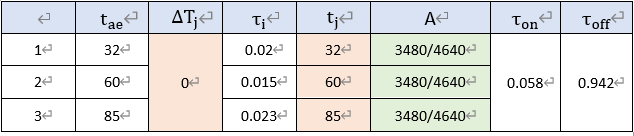

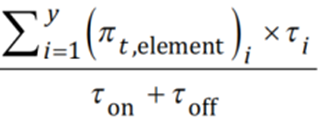

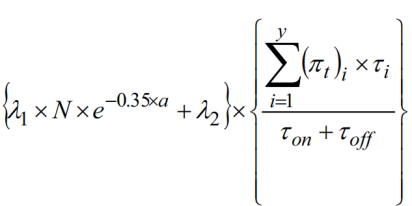

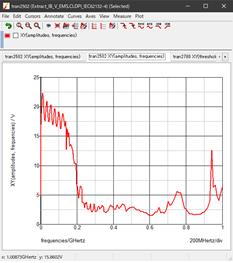

Step 2:溫度De-rating系數(shù)的計算

羅列計算溫度De-rating系數(shù)所需的參數(shù),Mission profile:“Motor Control”

表5

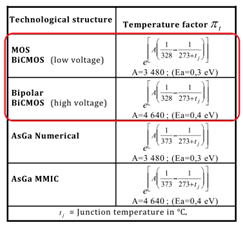

這里需要注意的是:由于element 3是的類型是linear circuits HV,包含2種技術結構,所以這個例子使用的πt計算模型有2個。

圖9 πt的計算模型選擇

將上表中的參數(shù)、計算模型代入溫度De-rating系數(shù)的計算公式中去,得:

?

表6

Step 3:失效率的計算

將step 1、2中的參數(shù)代入到下面的計算公式中,得:

?

表7

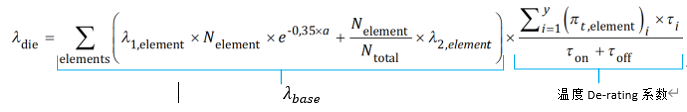

一體法

一體法是將芯片作為一個整體去考慮、不在區(qū)分內部電路類型,不用根據(jù)電路類型選取參數(shù)、也不用考慮不同電路晶體管數(shù)量和使用的技術的影響;由于只有一種類型電路,計算模型可以直接參考IEC TR 62380介紹的標準模型。

圖10 一體的計算模型

輸入參數(shù)(參考ISO 26262-11:Table 5)

圖11 參考ISO 26262-11:Table?5

輸入參數(shù)和參數(shù)的選擇與加權平均法的例子基本保持一致,后續(xù)的計算過程也不在進行詳細介紹;其中主要區(qū)別在于將CPU和SRAM當作整體考慮時電路類型選擇的是”Micros”,相應的λ1和λ2的選取如下:

圖12

據(jù)說Infineon的TC系列MCU所使用就是將MCU作為一個整體來選取參數(shù),希望有專家能提供一下一些參數(shù),可以嘗試推算一下其FMEDA里的參數(shù)。

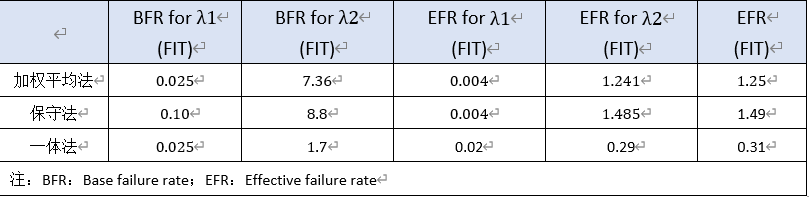

3.三種方法的結果對比

ISO 26262-11: 4.6.2.1.1.1介紹了三種方法來計算包含2種以上電路類型時的集成電路裸片失效,這三種方法計算的結果會有多大差異?

以(50k gate CPU、16kB SRAM)為例來對比,加權平均法和一體法都使用了這一例子,直接代入計算結果,計算過程可以見2.2.1和2.2.3章節(jié);針對保守法計算結果如下:

表8

將3種方法的結果列入表中進行對比:

表9

λdie三種計算方法的總結:

在晶體管數(shù)量較小的情況下,λ2的值對最終結果影響較大;

一體法是最樂觀的,可以理解為:選擇了較小的λ2;但是λ1的值會使λ1的base失效率有所偏大(存儲相關的λ1時DSP的1/20,粗略計算一下存儲比DSP等效晶體管數(shù)量多728萬個時,λ1的base失效率的影響將超過λ2)。

加權平均法處于保守法與一體法之間,即考慮了不同電路類型的技術、又兼顧到不同電路所包含的晶體管數(shù)量的占比問題;個人推薦。

來源?|?sasetech

參考文章:

[1]?ISO 26262:2018, Road vehicles — Functional safety —Part 11:Guidelines on application of ISO 26262 to semiconductors

[2] IEC/TR 62380:2004, Reliability data handbook — Universal model for reliability prediction of electronics components, PCBs and equipment

編輯:黃飛

?

電子發(fā)燒友App

電子發(fā)燒友App

評論