為何采用移動像素鏈路 (MPL)?

目前沒有一種線路互連標準可以完全符合小型手持式電子產品的嚴格要求。現有的接口技術如低電壓差分信號傳輸 (LVDS)、更低擺幅差分信號傳輸 (RSDS) 及 CMADS 雖然仍可滿足上一代筆記本計算機的要求,例如仍可節省舊式電子產品的用電,減少這類產品的互連線路,以及減低其電磁干擾,但對于正在開發中的新一代蜂窩式移動電話及個人數字助理來說,現有的接口技術便無法滿足其要求,因為新一代產品的設計要求更低的功率、更少互連線路以及更低的電磁干擾。移動像素鏈路 (MPL) 可為接收及發送視頻的輸入/輸出端口提供一個高性能的通信接口,而這種接口具有以下三大優點:更少的連線(只有兩條活躍線路)、功率低以及電磁干擾極為微弱。

MPL 鏈路

為了確保系統操作時可以充分發揮低功率及低電磁干擾的優點,MPL 鏈路技術利用較低的電流來傳送信號,而這兩個邏輯電平的高低取決于接收器傳送給發送器的電流究竟是強還是弱。這兩條電流可視為一條電流,在上層流動的是交流電電流,在下層流動的則是直流偏壓電流,上下層電流的典型值分別為 150mA 及 450mA。換言之,這兩條電流可分為一條在上層流動的交流電電流 (±150mA) 以及另一條在下層流動的直流電電流 (300mA)。

MPL 的技術規格對高低電流有清楚的界定,高電流 (即 450mA) 屬于邏輯低電平,而低電流 (150mA) 則屬于邏輯高電平。電流先由驅動器接收,然后通過 MG (MSSA) 管腳傳送回接收器。MPL 接地的附近應有一條低阻抗的路徑,而這條路徑應回到其起點 (即接收器)。此外,將接地設于信號傳送線路的附近有助縮小信號傳送線路的覆蓋面積,而且由于采用電流模式開關,加上電流量較低,以及較小的覆蓋面積,因此產生的電磁干擾也較少。

MPL 鏈路比其它信號傳輸標準更優勝,例如 MPL 鏈路傳送的電流比 LVDS 低 (前者為 300mA 而后者為 3.5mA);MPL 的 20mV 電壓擺幅也比 LVDS 的 350mv 低。這兩個優點有助減低功耗及噪音。鏈路通電時,從屬芯片隨即啟動,其電流由驅動器拉至適當的水平。這樣可以確保 MPL 鏈路無論從哪一個方向傳送信號,信號都可保持完整無缺,而且抵抗噪音干擾的能力也可獲得進一步加強。

美國國家半導體采用 WhisperBusÔ 技術作為 MPL 鏈路的物理層。一直以來,屏幕較大的薄膜晶體管 (TFT) 液晶顯示器都采用類似 WhisperBus 的技術,而便攜式電子產品也基于同樣的理由采用這種技術。MPL 鏈路除了保留 WhisperBus 物理層的基本功能之外,還設有自己的移動通信協議 (截至 2004 年有關協議仍在制定中),以及另外再添加節能 (睡眠) 模式及雙向數據傳輸功能。圖 1 所示的是基本的 MPL 鏈路。主控器設于主機 (BBP、微處理器或圖像處理器) 之旁,而從屬芯片則緊貼顯示器或目標裝置。

圖 1:MPL 鏈路總線的配置

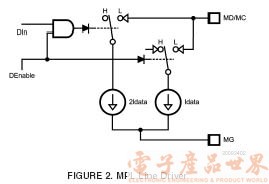

MPL 線路驅動器

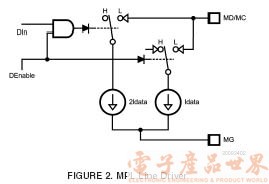

MPL 線路驅動器設有一個雙狀態的電流接收器。電流的大小取決于輸入的狀態 (LVCMOS)。線路的電壓由 MPL 鏈路上的接收器而非線路驅動器負責設定。由于線路驅動器可在廣闊的接收電壓范圍內操作,因此如有設計上的需要,線路驅動器及接收器可以分別由不同的供電干線為其提供電源。接收器的電源也可關閉,以便將線路電流調低至零,以支持極低功率的睡眠模式或 MPL 的關閉狀態。圖 2 所示的是已簡化的線路驅動器電路圖。若 DEnable* (內部信號) 處于邏輯低電平 (LOW),Idata 開關便與 MPL 信號線路連接一起,而驅動器會接收較強的電流 (Idata)。若 Din 內部信號處于邏輯低電平 (LOW),2Idata 也會通過開關輸入線路,令 3xIdata 的電流改由驅動器接收。若 Din 處于邏輯高電平,2xIdata 開關會斷開,以便進入另一狀態 (Idata)。若兩個開關都斷開 (DEnable* = High),驅動器會關閉,驅動器便不會接收任何電流。理論上,按照 MPL 標準的規定,邏輯低電平屬較高電流 (3 x Idata),而邏輯高電平則屬較低電流 (1 x Idata)。進行初步測試時,MPL 測試芯片 (LM2500) 的電流 (Idata) 可設定在 100mA 至 200mA 的范圍內。驅動器采用低電壓的設計,可以支持低至只有幾百 mV 的核心干線電壓。此外,電流會經過 MPL 接地 (MG) 直接回流。以驅動器的設計來說,MC (時鐘) 輸出與 MD (數據) 輸出實際相同。

圖 2:MPL 線路驅動器

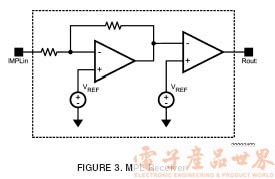

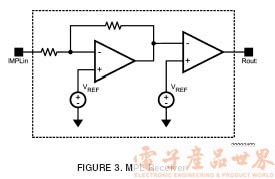

MPL 接收器

MPL 接收器負責測定總線的電流狀態,并將電流轉為電壓,然后不管電路是否已通電,再將電壓提升至標準的邏輯電路電平。此外,接收器也有自己的線路終端裝置,因此系統無需加設外接的終端電阻,有助精簡系統設計,以及節省印刷電路板的板面空間。這款接收器也內置電流傳感電路,一旦感測到任何信號,傳感器會向從屬芯片發出信號,要求有關芯片開啟或關閉電源供應。如果線路連接已中斷,主控器會監控 MD 線路的電流,以便清楚知道從屬芯片是否已發出服務請求。

圖 3:MPL 接收器

MPL 收發器

線路驅動器及接收器可以集成一起,成為收發器。以主控器為例來說,一般會以線路驅動器為 MD 的預設裝設。系統會關閉接收器區段的電流供應,以減低其用電量。處理 Read_Data 時,系統也可關閉主控器的 MD 線路驅動器,以中斷驅動器與總線之間的聯系。讀取數據時,數據會逆向傳送,線路驅動器的電源供應也會隨即中斷。以從屬芯片為例來說,一般會以接收器為 MD 的預設裝置,但為了節省能源,MD 線路驅動器不會獲得電源供應。收到有關 Read_Command 之后,系統會進入時間較長的逆轉 (Turn Around) 階段,讓從屬芯片的 MD 線路驅動器有足夠時間通電。此時,從屬芯片可以中斷 MD 接收器與 MD 線路的聯系,或干脆中斷其電源供應。

MPL 總線配置

基本的 MPL 鏈路由兩條活躍信號線路及一條信號接地回送 (MG) 線路組成。時鐘屬于單向信號,而且一定由主控器提供。數據信號 (MD) 與主控器送往從屬芯片的時鐘同步,而主控器傳送時鐘時,會同時利用兩個時鐘邊緣。這樣有助降低時鐘速率,以減低功耗、噪音及電磁干擾。MD 數據信號通過半雙工的雙向線路傳送。為了支持數據輸入 (讀取)的執行,數據信號可以逆向傳送。以正常的配置為例來說,處理數據輸出 (寫入) 時,系統不會為主控器的 MD 接收器及從屬芯片的 MD 線路驅動器提供供電,以便節省能源。MD 線路的逆轉 (TA) 時間較長,以確保線路在必要時有足夠時間通電或斷電。

目前的系統普遍采用獨特的視頻路徑及點至點的設計, MPL 的技術標準已充分考慮這兩個因素。MPL 技術采用點至點的設計,讓鏈路可以充分發揮其電子特性。此外,MPL 鏈路有自己的內部終端裝置,因此工程師可以輕易設計高性能的傳輸線路,例如,無需顧慮線頭所產生的影響。此外,需要利用 MPL 鏈路建立互連的裝置如顯示器、照相機等一般都分別設于不同的地方,因此串行的點至點鏈路比多站式或多點式鏈路更適合這些裝置采用。此外,由于 MPL 鏈路只有兩條活躍導線,因此采用多個 MPL 接口比采用并行總線更符合成本效益,而且可以節省板面空間及減少管腳數目。

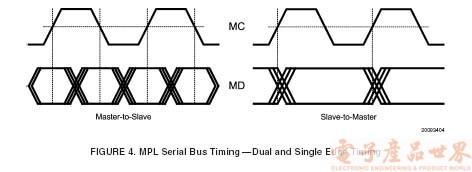

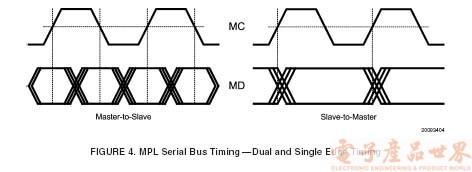

MPL 鏈路的數據傳輸率

當主控器將數據傳送往從屬芯片時,LM2500/1/2 收發器可以提供高達 160 Mbps 的基本數據傳輸率以作支持。由于這個模式可以同時利用時鐘的兩邊,因此數據傳輸率最高可達 160 Mbps (每段 6.25ns),而時鐘頻率則為 80 MHz。因為能夠同時利用時鐘的兩邊,所以可以傳送低頻的時鐘信號,而低頻操作則有助減低電磁干擾。相較之下,單單利用時鐘的一邊,會令時鐘信號高達 160 MHz。后排通道負責將數據由從屬芯片傳送往主控器。利用后排通道傳送數據時,從屬芯片只利用時鐘的上升邊緣控制數據的進出,使從屬芯片傳送數據往主控器時,可以有較多時間按照主控器提供的時鐘頻率進行取樣。系統只要能以 80 MHz 的時鐘頻率操作,后排通道便能以 80 Mbps 的傳輸率傳送數據。

目前的數據傳輸率一般都不超過 160 Mbps,但有足夠的空間可以提升至 200 Mbps 以至 400 Mbps。預計不久的將來物理層可以支持每秒高達千兆位 (Gbps) 以上的速度。但這些高速傳輸技術仍在研發中。

MPL 鏈路的數據傳輸率 (續)

圖 4:MPL 串行總線計時 – 雙及單邊計時

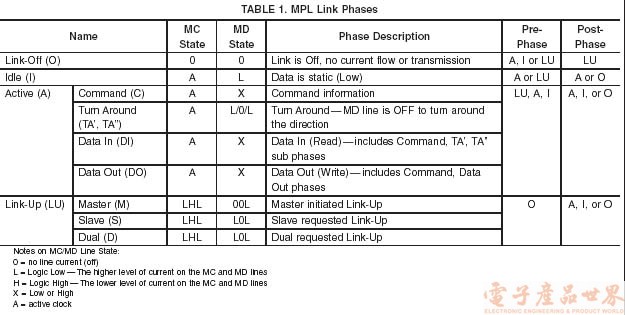

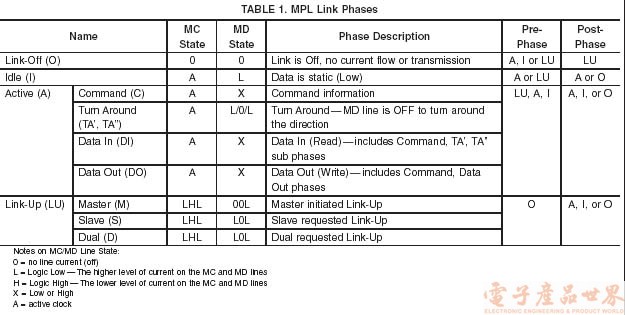

MPL 總線的不同階段

MPL 串行總線分為四個不同的總線階段,每一階段都由 MC 及 MD 線路的狀態決定,而其中的兩個階段有多個不同狀態可供選擇。圖表 1 “MPL鏈路的不同階段”顯示 MPL 總線的不同階段。

圖表 1:MPL 鏈路的不同階段

有關 MC/MD 線路狀態的詞語釋義:

O = 無線路電流 (關閉)

L = 邏輯低電平 -- MC 及 MD 線路電流的較高電平

H = 邏輯高電平 -- MC 及MD 線路電流的較低電平

X = 低或高

A = 動態時鐘

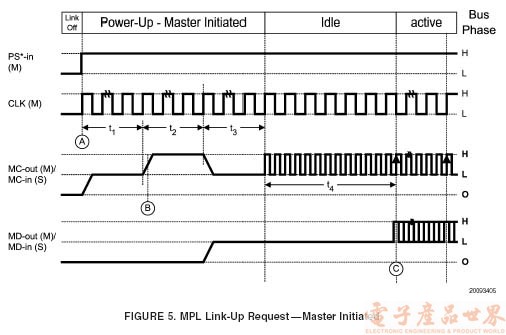

通電/斷電

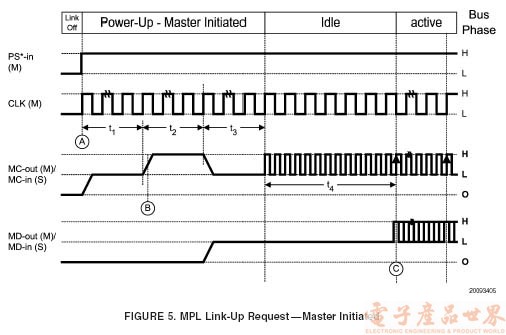

采用省電模式 (關閉) 時,系統會關閉 MD 及 MC 驅動器,線路上的電流會完全中斷。主控器將傳送 A 點 12 個時鐘 (t1) 的 MC 線路驅動至低電平,以便通知從屬芯片建立連接。然后主控器將傳送 12 個時鐘 (t2) 的 MC 線路驅動至高電平。當低電平轉為高電平時 ( B 點),從屬芯片充分利用其電源供應,以便有更大的能力承受噪音干擾。最后,主控器將傳送 12 個時鐘 (t3) 的 MC 及 MD 線路驅動至穩定的低電平狀態。建立連接的階段需要 36 個周期才能完成。主控器直到現在才可傳送數據 (動態),將總線閑置,或重新回到連接中斷狀態。

以圖 5 為例來說,總線閑置階段的時間長度為 t4,之后總線保持其活躍狀態,而 MD 線路的“高電平”起始位會啟動數據的傳輸 (C 點)。

圖 5:MPL 鏈路提出建立連接的請求 -- 由主控器啟動

有一點需要留意,當連接中斷之后,主控器便會進入省電 (Power_Save) 模式,而正在操作的主控器鎖相環路 (PLL) 會根據其時鐘來源鎖定其相位 (不同的應用有不同的安排 -- 若主機可以提供高速時鐘,便無需作此安排)。

從屬芯片也可通知主控器啟動電源。過程如下:從屬芯片先將 MD 線路驅動至邏輯低電平,直至主控器作出回應,將同樣已驅動至邏輯低電平的 MC 信號傳回為止。主控器可以檢測 MD 線路是否有電流,并產生 INTR 信號,以便將從屬芯片提出建立連接的請求通知本地主機。

主機首先停止為 PS* 管腳作出程序測試假設,以便清除 INTR 信號,然后主控器才將傳送最少 12 個時鐘周期的 MC 線路驅動至低電平。從屬芯片可以檢測出 MC 線路是否處于低電平狀態,然后在 MC 線路由高電平轉為低電平之前關閉其 MD 驅動器。可以感測 MD 線路的主控器隨即關閉,然后將 MD 線路驅動至靜態的低電平。正如圖 6 所顯示,經過另一段長達 12 個時鐘周期的階段之后,總線階段此時正處于閑置狀態,而且可能繼續維持在閑置狀態之中,以便將電源關閉 (中斷連接),或重新操作。有一點需要留意,t3 的長短取決于系統 (主機) 的反應時間。

通電/斷電 (續)

圖 6:MPL 鏈路提出建立連接的請求 -- 由從屬芯片啟動

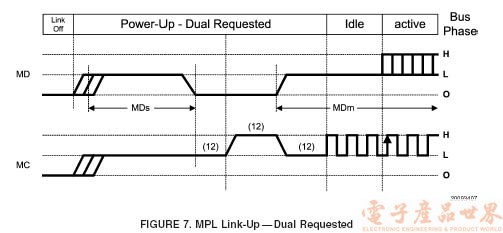

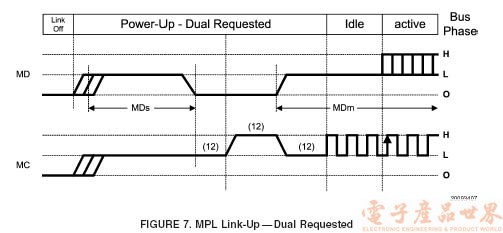

若從屬芯片及主控器同時啟動建立連接請求,便會出現圖 7 所顯示的時間序列。由于所需時間各不相同,因此各時段可能重疊,以這個情況來說,系統可以利用這個序列將 MPL 總線連接起來。當總線處于連接中斷階段時,MC 及 MD 線路上的電流會完全中斷。若主控器及從屬芯片差不多在同一時間啟動通電序列 (此時的 MC 及 MD 線路已驅動至低電平),從屬芯片會先行檢測主控器是否正在驅動 MC 線路,然后將其 MD 驅動器失效 (參看 MD)。主控器會檢測 MC 線路是否處于低電平,然后如圖 5 所示,啟動應由主控器啟動的標準通電序列。正如圖 7 所顯示,通電序列啟動后,總線階段會處于閑置狀態 (也可能處于活躍狀態),而且可能繼續維持在閑置狀態之中,以便將電源關閉,或重新操作。有一點需要留意,圖 7 并無顯示控制信號。

圖 7:MPL 連接 -- 兩方提出請求

線路互連的載體

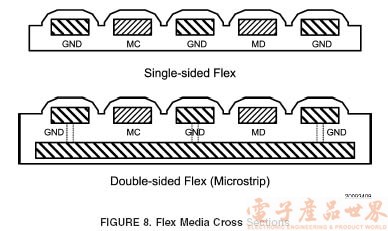

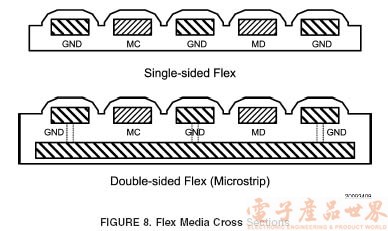

印刷電路板走線、柔性電纜或短的接線都可用作互連的線路。實際的互連線路的類型及配置要視乎系統的實際要求而定,例如互連線路的長短、機械性能的局限以及電磁兼容性 (EMC) 等要求。柔性電纜是一種成本較低的互連線路,因此經常用于小型的電子產品。單面的柔性電纜成本最低,但阻抗一般會較高,而且所提供的屏蔽保護極為有限。在正常的應用情況下,單面柔性電纜已很足夠,可以支持數據傳輸速度較慢及噪音較少的應用系統。雙面的柔性電纜 (即微帶Microstrip ) 可以提供阻抗更易受控制的通道,即使普通的大小也可輕易組成 50W 負載的線路。此外,這類電纜可為接地層提供屏蔽,若有需要,也可為線跡提供接地保護,這也是雙面柔性電纜的優點。系統至少采用三條信號傳輸線路,其中兩條供 MD 和 MC 線路使用,而另外一條是共用接地回流電路。MG 接地應在鏈路的兩端連接接地,以便將接地環路覆蓋面積減至最小。圖 8 所顯示的是單面及雙面柔性電纜的橫切面圖。

連接器的必要特性也取決于個別的應用。但由于 Plug 或 ZIF 連接器只會用其中一面 (并非柔性那一面),加上這類連接器體積較小,而且比管腳及插座式連接器更便宜,因此一般的系統都會采用 Plug 或 ZIF 連接器。

圖 8:柔性載體的橫切面圖

多長?多快?

在初期階段,MPL 的應用會朝著 40、80 及 160 Mbps 的速率邁進,但確實的傳輸率主要由照相機的陣列體積及時鐘頻率或顯示器的清晰度所決定。預計數據傳輸率將會倍增至 320 Gbps。據一些模擬測試顯示,傳輸率實際上可以高達千兆位 (Gigabit) 以上。數據傳輸率受多個不同因素影響,有關因素包括驅動電流、線路長短、載體素質及阻抗控制。大部分的顯示器設計若非采用單向的傳輸方式,便無需后排通道的支持。為了精簡系統設計,時鐘必須由主控器提供及傳送往從屬芯片。這個設計可以支持以單邊時脈進行半速操作的后排通道,以便提高時間的限制 (參看圖 4)。

MPL 的應用主要針對小型便攜式電子設備,其中包括移動電話及個人數字助理。這些電子產品的互連線路一般長達 5、10 以至 15 厘米 (相當于 2、4、8 英吋)。MPL 接口的總長度大致上不會超過 30 cm。正如上文所說,長度也與載體素質、數據傳輸率及驅動電流 (Idata) 設定有關。

MPL 鏈路的功耗

MPL 鏈路有多種不同的方法節省用電。例如,我們可以采用低電流數據傳送模式傳送數據,而電流甚至可以低至只有幾百 mA,但卻可確保系統能以幾百 Mbps 的速度傳送數據。低操作電流及低電源供應可以限制開關尖峰及噪音,并且只會帶給電路極微小的電壓波動。由于線路的電壓極低,因此無需像較大擺幅的信號傳輸電路一樣要先將線路/負載電容大量充電/放電,正因為充電/放電量較少,所以能夠節省較多能源。芯片組也設有節省用電 (連接中斷) 的功能,可以在沒有需要時將接口電流關閉,以便為系統節省更多用電。此外,由于數據及時鐘分開傳送,因此接收器以至發送器 (若已有高速時鐘的話) 便無需加設耗電量較大的鎖相環路區段或編碼器。

電磁干擾

基于以下的特性,MPL 鏈路只產生極微量的電磁干擾:

1)10mV 的傳輸電壓 (微弱的 dV/dT)

2)150/450 mA 的信號傳輸狀態

3)采用電流模式傳送信號,確保邊緣較為圓滑

4)信號線路及 MPL 接地之間的電路覆蓋較小面積

5)按照頻率時鐘操作

6)專用的電流回流路徑/細小的環狀天線

此外,根據過去的經驗顯示,WhisperBus 可以大幅降低平面顯示器的電磁干擾,以這方面來說,遠比 3V 單端信號傳送方式優勝。專為筆記電腦開發顯示器的廠商曾向美國國家半導體表示,采用 WhisperBus 接口的顯示器比采用 RSDS (低至 200mV 的更低擺幅 LVDS 信號傳輸) 技術的薄膜晶體管 (TFT) 平面顯示器產生更少電磁干擾。

EMS/射頻干擾 (RFI)

雖然 MPL 鏈路的電壓擺幅很小,而且電流也較低,但性能仍非常可靠。MPL 技術之所以有這個優點,完全是因為這種鏈路采用低阻抗終端連接接地以及低阻抗線路 (50W),這樣有助減少隨著接收信號潛入系統的噪音。

至于承受射頻干擾的能力問題,美國國家半導體正計劃進行各種有關的測試。以采用寬帶 (WB) 線路傳送數據以及利用 RSDS (LVDS) 技術傳送時鐘的大型平面顯示器為例來說,目前我們已完成這方面的初步測試。

EMS/射頻干擾 (RFI) (續)

進行測試時,移動電話天線放在指定的線跡 (trace) 上,位置則靠近 5W 的 CB 射頻系統 (49 MHz),而移動電話正在傳送語音。測試時, 采用測試模式的行驅動器錯誤率管腳顯示寬帶線路并無出現錯誤。最先出現錯誤的竟然是 RSDS/SVDS 線路!相信有關錯誤與傳輸電路與終端裝置有關。LVDS 線路很多時都采用 100W 的終端裝置,共模阻抗也較高,因此噪音很易進入線路,產生共模調制,最后甚至干擾接收器的檢測電路,令差分信號出現訛誤。此外,由于寬帶 (MPL) 線路的終端裝置連接阻抗較低的交流電接地點,因此需要較強的信號才可產生足夠電壓,翻轉有關的數據。此外,MPL 鏈路采用 50W 的阻抗與接地連接。相較之下,LVDS 技術的接地阻抗可能高達幾千W,確實的阻抗要視個別設計而定。(測試時采用的移動電話:兩個不同的 Samsung Sprint PCS 電話以及一個 Nokia 5190 電話。) 其它的因素也會影響系統承受射頻干擾的能力,有關因素包括系統接地、屏蔽及線路互連設計等。

MPL 標準

目前各大系統集成商、硅片供應商及其它有關方都加緊研究 MPL 鏈路的物理層 (MPL-0) 及連接層的特性。

內容提要

MPL 是專為便攜式視頻系統而設的鏈路,這是 MPL 技術與其它接口的最大分別,其主要特色如下:

·線路較少

·低功率

·低電磁干擾

·簡單的協議/低門數

·專為視頻應用而設

·雙向點至點的鏈路

·開放式標準/可以采用不同供應商的產品

·以低至只有幾 mW 的功率操作也可支持數以百萬計的像素

目前沒有一種線路互連標準可以完全符合小型手持式電子產品的嚴格要求。現有的接口技術如低電壓差分信號傳輸 (LVDS)、更低擺幅差分信號傳輸 (RSDS) 及 CMADS 雖然仍可滿足上一代筆記本計算機的要求,例如仍可節省舊式電子產品的用電,減少這類產品的互連線路,以及減低其電磁干擾,但對于正在開發中的新一代蜂窩式移動電話及個人數字助理來說,現有的接口技術便無法滿足其要求,因為新一代產品的設計要求更低的功率、更少互連線路以及更低的電磁干擾。移動像素鏈路 (MPL) 可為接收及發送視頻的輸入/輸出端口提供一個高性能的通信接口,而這種接口具有以下三大優點:更少的連線(只有兩條活躍線路)、功率低以及電磁干擾極為微弱。

MPL 鏈路

為了確保系統操作時可以充分發揮低功率及低電磁干擾的優點,MPL 鏈路技術利用較低的電流來傳送信號,而這兩個邏輯電平的高低取決于接收器傳送給發送器的電流究竟是強還是弱。這兩條電流可視為一條電流,在上層流動的是交流電電流,在下層流動的則是直流偏壓電流,上下層電流的典型值分別為 150mA 及 450mA。換言之,這兩條電流可分為一條在上層流動的交流電電流 (±150mA) 以及另一條在下層流動的直流電電流 (300mA)。

MPL 的技術規格對高低電流有清楚的界定,高電流 (即 450mA) 屬于邏輯低電平,而低電流 (150mA) 則屬于邏輯高電平。電流先由驅動器接收,然后通過 MG (MSSA) 管腳傳送回接收器。MPL 接地的附近應有一條低阻抗的路徑,而這條路徑應回到其起點 (即接收器)。此外,將接地設于信號傳送線路的附近有助縮小信號傳送線路的覆蓋面積,而且由于采用電流模式開關,加上電流量較低,以及較小的覆蓋面積,因此產生的電磁干擾也較少。

MPL 鏈路比其它信號傳輸標準更優勝,例如 MPL 鏈路傳送的電流比 LVDS 低 (前者為 300mA 而后者為 3.5mA);MPL 的 20mV 電壓擺幅也比 LVDS 的 350mv 低。這兩個優點有助減低功耗及噪音。鏈路通電時,從屬芯片隨即啟動,其電流由驅動器拉至適當的水平。這樣可以確保 MPL 鏈路無論從哪一個方向傳送信號,信號都可保持完整無缺,而且抵抗噪音干擾的能力也可獲得進一步加強。

美國國家半導體采用 WhisperBusÔ 技術作為 MPL 鏈路的物理層。一直以來,屏幕較大的薄膜晶體管 (TFT) 液晶顯示器都采用類似 WhisperBus 的技術,而便攜式電子產品也基于同樣的理由采用這種技術。MPL 鏈路除了保留 WhisperBus 物理層的基本功能之外,還設有自己的移動通信協議 (截至 2004 年有關協議仍在制定中),以及另外再添加節能 (睡眠) 模式及雙向數據傳輸功能。圖 1 所示的是基本的 MPL 鏈路。主控器設于主機 (BBP、微處理器或圖像處理器) 之旁,而從屬芯片則緊貼顯示器或目標裝置。

圖 1:MPL 鏈路總線的配置

MPL 線路驅動器

MPL 線路驅動器設有一個雙狀態的電流接收器。電流的大小取決于輸入的狀態 (LVCMOS)。線路的電壓由 MPL 鏈路上的接收器而非線路驅動器負責設定。由于線路驅動器可在廣闊的接收電壓范圍內操作,因此如有設計上的需要,線路驅動器及接收器可以分別由不同的供電干線為其提供電源。接收器的電源也可關閉,以便將線路電流調低至零,以支持極低功率的睡眠模式或 MPL 的關閉狀態。圖 2 所示的是已簡化的線路驅動器電路圖。若 DEnable* (內部信號) 處于邏輯低電平 (LOW),Idata 開關便與 MPL 信號線路連接一起,而驅動器會接收較強的電流 (Idata)。若 Din 內部信號處于邏輯低電平 (LOW),2Idata 也會通過開關輸入線路,令 3xIdata 的電流改由驅動器接收。若 Din 處于邏輯高電平,2xIdata 開關會斷開,以便進入另一狀態 (Idata)。若兩個開關都斷開 (DEnable* = High),驅動器會關閉,驅動器便不會接收任何電流。理論上,按照 MPL 標準的規定,邏輯低電平屬較高電流 (3 x Idata),而邏輯高電平則屬較低電流 (1 x Idata)。進行初步測試時,MPL 測試芯片 (LM2500) 的電流 (Idata) 可設定在 100mA 至 200mA 的范圍內。驅動器采用低電壓的設計,可以支持低至只有幾百 mV 的核心干線電壓。此外,電流會經過 MPL 接地 (MG) 直接回流。以驅動器的設計來說,MC (時鐘) 輸出與 MD (數據) 輸出實際相同。

圖 2:MPL 線路驅動器

MPL 接收器

MPL 接收器負責測定總線的電流狀態,并將電流轉為電壓,然后不管電路是否已通電,再將電壓提升至標準的邏輯電路電平。此外,接收器也有自己的線路終端裝置,因此系統無需加設外接的終端電阻,有助精簡系統設計,以及節省印刷電路板的板面空間。這款接收器也內置電流傳感電路,一旦感測到任何信號,傳感器會向從屬芯片發出信號,要求有關芯片開啟或關閉電源供應。如果線路連接已中斷,主控器會監控 MD 線路的電流,以便清楚知道從屬芯片是否已發出服務請求。

圖 3:MPL 接收器

MPL 收發器

線路驅動器及接收器可以集成一起,成為收發器。以主控器為例來說,一般會以線路驅動器為 MD 的預設裝設。系統會關閉接收器區段的電流供應,以減低其用電量。處理 Read_Data 時,系統也可關閉主控器的 MD 線路驅動器,以中斷驅動器與總線之間的聯系。讀取數據時,數據會逆向傳送,線路驅動器的電源供應也會隨即中斷。以從屬芯片為例來說,一般會以接收器為 MD 的預設裝置,但為了節省能源,MD 線路驅動器不會獲得電源供應。收到有關 Read_Command 之后,系統會進入時間較長的逆轉 (Turn Around) 階段,讓從屬芯片的 MD 線路驅動器有足夠時間通電。此時,從屬芯片可以中斷 MD 接收器與 MD 線路的聯系,或干脆中斷其電源供應。

MPL 總線配置

基本的 MPL 鏈路由兩條活躍信號線路及一條信號接地回送 (MG) 線路組成。時鐘屬于單向信號,而且一定由主控器提供。數據信號 (MD) 與主控器送往從屬芯片的時鐘同步,而主控器傳送時鐘時,會同時利用兩個時鐘邊緣。這樣有助降低時鐘速率,以減低功耗、噪音及電磁干擾。MD 數據信號通過半雙工的雙向線路傳送。為了支持數據輸入 (讀取)的執行,數據信號可以逆向傳送。以正常的配置為例來說,處理數據輸出 (寫入) 時,系統不會為主控器的 MD 接收器及從屬芯片的 MD 線路驅動器提供供電,以便節省能源。MD 線路的逆轉 (TA) 時間較長,以確保線路在必要時有足夠時間通電或斷電。

目前的系統普遍采用獨特的視頻路徑及點至點的設計, MPL 的技術標準已充分考慮這兩個因素。MPL 技術采用點至點的設計,讓鏈路可以充分發揮其電子特性。此外,MPL 鏈路有自己的內部終端裝置,因此工程師可以輕易設計高性能的傳輸線路,例如,無需顧慮線頭所產生的影響。此外,需要利用 MPL 鏈路建立互連的裝置如顯示器、照相機等一般都分別設于不同的地方,因此串行的點至點鏈路比多站式或多點式鏈路更適合這些裝置采用。此外,由于 MPL 鏈路只有兩條活躍導線,因此采用多個 MPL 接口比采用并行總線更符合成本效益,而且可以節省板面空間及減少管腳數目。

MPL 鏈路的數據傳輸率

當主控器將數據傳送往從屬芯片時,LM2500/1/2 收發器可以提供高達 160 Mbps 的基本數據傳輸率以作支持。由于這個模式可以同時利用時鐘的兩邊,因此數據傳輸率最高可達 160 Mbps (每段 6.25ns),而時鐘頻率則為 80 MHz。因為能夠同時利用時鐘的兩邊,所以可以傳送低頻的時鐘信號,而低頻操作則有助減低電磁干擾。相較之下,單單利用時鐘的一邊,會令時鐘信號高達 160 MHz。后排通道負責將數據由從屬芯片傳送往主控器。利用后排通道傳送數據時,從屬芯片只利用時鐘的上升邊緣控制數據的進出,使從屬芯片傳送數據往主控器時,可以有較多時間按照主控器提供的時鐘頻率進行取樣。系統只要能以 80 MHz 的時鐘頻率操作,后排通道便能以 80 Mbps 的傳輸率傳送數據。

目前的數據傳輸率一般都不超過 160 Mbps,但有足夠的空間可以提升至 200 Mbps 以至 400 Mbps。預計不久的將來物理層可以支持每秒高達千兆位 (Gbps) 以上的速度。但這些高速傳輸技術仍在研發中。

MPL 鏈路的數據傳輸率 (續)

圖 4:MPL 串行總線計時 – 雙及單邊計時

MPL 總線的不同階段

MPL 串行總線分為四個不同的總線階段,每一階段都由 MC 及 MD 線路的狀態決定,而其中的兩個階段有多個不同狀態可供選擇。圖表 1 “MPL鏈路的不同階段”顯示 MPL 總線的不同階段。

圖表 1:MPL 鏈路的不同階段

有關 MC/MD 線路狀態的詞語釋義:

O = 無線路電流 (關閉)

L = 邏輯低電平 -- MC 及 MD 線路電流的較高電平

H = 邏輯高電平 -- MC 及MD 線路電流的較低電平

X = 低或高

A = 動態時鐘

通電/斷電

采用省電模式 (關閉) 時,系統會關閉 MD 及 MC 驅動器,線路上的電流會完全中斷。主控器將傳送 A 點 12 個時鐘 (t1) 的 MC 線路驅動至低電平,以便通知從屬芯片建立連接。然后主控器將傳送 12 個時鐘 (t2) 的 MC 線路驅動至高電平。當低電平轉為高電平時 ( B 點),從屬芯片充分利用其電源供應,以便有更大的能力承受噪音干擾。最后,主控器將傳送 12 個時鐘 (t3) 的 MC 及 MD 線路驅動至穩定的低電平狀態。建立連接的階段需要 36 個周期才能完成。主控器直到現在才可傳送數據 (動態),將總線閑置,或重新回到連接中斷狀態。

以圖 5 為例來說,總線閑置階段的時間長度為 t4,之后總線保持其活躍狀態,而 MD 線路的“高電平”起始位會啟動數據的傳輸 (C 點)。

圖 5:MPL 鏈路提出建立連接的請求 -- 由主控器啟動

有一點需要留意,當連接中斷之后,主控器便會進入省電 (Power_Save) 模式,而正在操作的主控器鎖相環路 (PLL) 會根據其時鐘來源鎖定其相位 (不同的應用有不同的安排 -- 若主機可以提供高速時鐘,便無需作此安排)。

從屬芯片也可通知主控器啟動電源。過程如下:從屬芯片先將 MD 線路驅動至邏輯低電平,直至主控器作出回應,將同樣已驅動至邏輯低電平的 MC 信號傳回為止。主控器可以檢測 MD 線路是否有電流,并產生 INTR 信號,以便將從屬芯片提出建立連接的請求通知本地主機。

主機首先停止為 PS* 管腳作出程序測試假設,以便清除 INTR 信號,然后主控器才將傳送最少 12 個時鐘周期的 MC 線路驅動至低電平。從屬芯片可以檢測出 MC 線路是否處于低電平狀態,然后在 MC 線路由高電平轉為低電平之前關閉其 MD 驅動器。可以感測 MD 線路的主控器隨即關閉,然后將 MD 線路驅動至靜態的低電平。正如圖 6 所顯示,經過另一段長達 12 個時鐘周期的階段之后,總線階段此時正處于閑置狀態,而且可能繼續維持在閑置狀態之中,以便將電源關閉 (中斷連接),或重新操作。有一點需要留意,t3 的長短取決于系統 (主機) 的反應時間。

通電/斷電 (續)

圖 6:MPL 鏈路提出建立連接的請求 -- 由從屬芯片啟動

若從屬芯片及主控器同時啟動建立連接請求,便會出現圖 7 所顯示的時間序列。由于所需時間各不相同,因此各時段可能重疊,以這個情況來說,系統可以利用這個序列將 MPL 總線連接起來。當總線處于連接中斷階段時,MC 及 MD 線路上的電流會完全中斷。若主控器及從屬芯片差不多在同一時間啟動通電序列 (此時的 MC 及 MD 線路已驅動至低電平),從屬芯片會先行檢測主控器是否正在驅動 MC 線路,然后將其 MD 驅動器失效 (參看 MD)。主控器會檢測 MC 線路是否處于低電平,然后如圖 5 所示,啟動應由主控器啟動的標準通電序列。正如圖 7 所顯示,通電序列啟動后,總線階段會處于閑置狀態 (也可能處于活躍狀態),而且可能繼續維持在閑置狀態之中,以便將電源關閉,或重新操作。有一點需要留意,圖 7 并無顯示控制信號。

圖 7:MPL 連接 -- 兩方提出請求

線路互連的載體

印刷電路板走線、柔性電纜或短的接線都可用作互連的線路。實際的互連線路的類型及配置要視乎系統的實際要求而定,例如互連線路的長短、機械性能的局限以及電磁兼容性 (EMC) 等要求。柔性電纜是一種成本較低的互連線路,因此經常用于小型的電子產品。單面的柔性電纜成本最低,但阻抗一般會較高,而且所提供的屏蔽保護極為有限。在正常的應用情況下,單面柔性電纜已很足夠,可以支持數據傳輸速度較慢及噪音較少的應用系統。雙面的柔性電纜 (即微帶Microstrip ) 可以提供阻抗更易受控制的通道,即使普通的大小也可輕易組成 50W 負載的線路。此外,這類電纜可為接地層提供屏蔽,若有需要,也可為線跡提供接地保護,這也是雙面柔性電纜的優點。系統至少采用三條信號傳輸線路,其中兩條供 MD 和 MC 線路使用,而另外一條是共用接地回流電路。MG 接地應在鏈路的兩端連接接地,以便將接地環路覆蓋面積減至最小。圖 8 所顯示的是單面及雙面柔性電纜的橫切面圖。

連接器的必要特性也取決于個別的應用。但由于 Plug 或 ZIF 連接器只會用其中一面 (并非柔性那一面),加上這類連接器體積較小,而且比管腳及插座式連接器更便宜,因此一般的系統都會采用 Plug 或 ZIF 連接器。

圖 8:柔性載體的橫切面圖

多長?多快?

在初期階段,MPL 的應用會朝著 40、80 及 160 Mbps 的速率邁進,但確實的傳輸率主要由照相機的陣列體積及時鐘頻率或顯示器的清晰度所決定。預計數據傳輸率將會倍增至 320 Gbps。據一些模擬測試顯示,傳輸率實際上可以高達千兆位 (Gigabit) 以上。數據傳輸率受多個不同因素影響,有關因素包括驅動電流、線路長短、載體素質及阻抗控制。大部分的顯示器設計若非采用單向的傳輸方式,便無需后排通道的支持。為了精簡系統設計,時鐘必須由主控器提供及傳送往從屬芯片。這個設計可以支持以單邊時脈進行半速操作的后排通道,以便提高時間的限制 (參看圖 4)。

MPL 的應用主要針對小型便攜式電子設備,其中包括移動電話及個人數字助理。這些電子產品的互連線路一般長達 5、10 以至 15 厘米 (相當于 2、4、8 英吋)。MPL 接口的總長度大致上不會超過 30 cm。正如上文所說,長度也與載體素質、數據傳輸率及驅動電流 (Idata) 設定有關。

MPL 鏈路的功耗

MPL 鏈路有多種不同的方法節省用電。例如,我們可以采用低電流數據傳送模式傳送數據,而電流甚至可以低至只有幾百 mA,但卻可確保系統能以幾百 Mbps 的速度傳送數據。低操作電流及低電源供應可以限制開關尖峰及噪音,并且只會帶給電路極微小的電壓波動。由于線路的電壓極低,因此無需像較大擺幅的信號傳輸電路一樣要先將線路/負載電容大量充電/放電,正因為充電/放電量較少,所以能夠節省較多能源。芯片組也設有節省用電 (連接中斷) 的功能,可以在沒有需要時將接口電流關閉,以便為系統節省更多用電。此外,由于數據及時鐘分開傳送,因此接收器以至發送器 (若已有高速時鐘的話) 便無需加設耗電量較大的鎖相環路區段或編碼器。

電磁干擾

基于以下的特性,MPL 鏈路只產生極微量的電磁干擾:

1)10mV 的傳輸電壓 (微弱的 dV/dT)

2)150/450 mA 的信號傳輸狀態

3)采用電流模式傳送信號,確保邊緣較為圓滑

4)信號線路及 MPL 接地之間的電路覆蓋較小面積

5)按照頻率時鐘操作

6)專用的電流回流路徑/細小的環狀天線

此外,根據過去的經驗顯示,WhisperBus 可以大幅降低平面顯示器的電磁干擾,以這方面來說,遠比 3V 單端信號傳送方式優勝。專為筆記電腦開發顯示器的廠商曾向美國國家半導體表示,采用 WhisperBus 接口的顯示器比采用 RSDS (低至 200mV 的更低擺幅 LVDS 信號傳輸) 技術的薄膜晶體管 (TFT) 平面顯示器產生更少電磁干擾。

EMS/射頻干擾 (RFI)

雖然 MPL 鏈路的電壓擺幅很小,而且電流也較低,但性能仍非常可靠。MPL 技術之所以有這個優點,完全是因為這種鏈路采用低阻抗終端連接接地以及低阻抗線路 (50W),這樣有助減少隨著接收信號潛入系統的噪音。

至于承受射頻干擾的能力問題,美國國家半導體正計劃進行各種有關的測試。以采用寬帶 (WB) 線路傳送數據以及利用 RSDS (LVDS) 技術傳送時鐘的大型平面顯示器為例來說,目前我們已完成這方面的初步測試。

EMS/射頻干擾 (RFI) (續)

進行測試時,移動電話天線放在指定的線跡 (trace) 上,位置則靠近 5W 的 CB 射頻系統 (49 MHz),而移動電話正在傳送語音。測試時, 采用測試模式的行驅動器錯誤率管腳顯示寬帶線路并無出現錯誤。最先出現錯誤的竟然是 RSDS/SVDS 線路!相信有關錯誤與傳輸電路與終端裝置有關。LVDS 線路很多時都采用 100W 的終端裝置,共模阻抗也較高,因此噪音很易進入線路,產生共模調制,最后甚至干擾接收器的檢測電路,令差分信號出現訛誤。此外,由于寬帶 (MPL) 線路的終端裝置連接阻抗較低的交流電接地點,因此需要較強的信號才可產生足夠電壓,翻轉有關的數據。此外,MPL 鏈路采用 50W 的阻抗與接地連接。相較之下,LVDS 技術的接地阻抗可能高達幾千W,確實的阻抗要視個別設計而定。(測試時采用的移動電話:兩個不同的 Samsung Sprint PCS 電話以及一個 Nokia 5190 電話。) 其它的因素也會影響系統承受射頻干擾的能力,有關因素包括系統接地、屏蔽及線路互連設計等。

MPL 標準

目前各大系統集成商、硅片供應商及其它有關方都加緊研究 MPL 鏈路的物理層 (MPL-0) 及連接層的特性。

內容提要

MPL 是專為便攜式視頻系統而設的鏈路,這是 MPL 技術與其它接口的最大分別,其主要特色如下:

·線路較少

·低功率

·低電磁干擾

·簡單的協議/低門數

·專為視頻應用而設

·雙向點至點的鏈路

·開放式標準/可以采用不同供應商的產品

·以低至只有幾 mW 的功率操作也可支持數以百萬計的像素

電子發燒友App

電子發燒友App

評論