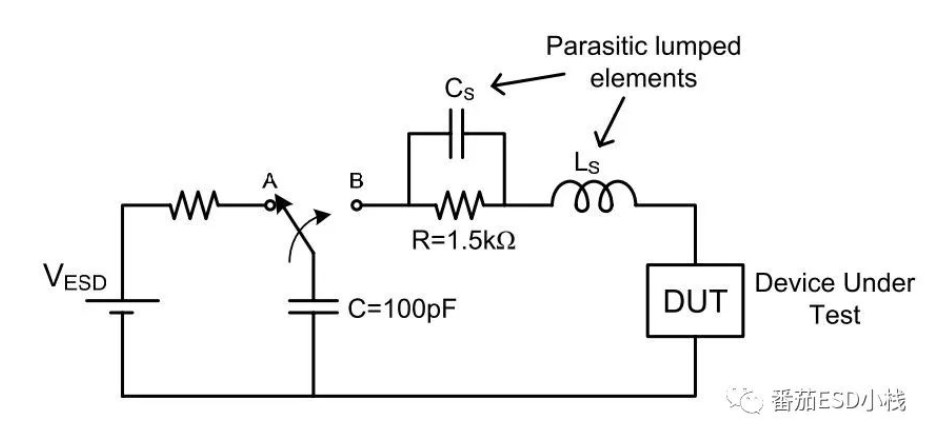

做, 使用TLP脈沖方波評估芯片的ESD性能,可以是Wafer,die或封裝后成品。? 通常0V打到fail ? ESD-gun 靜電槍測試? 模擬單板、系統外部接口在帶電插拔等情況下的ESD放電,板級、系統級

2021-11-24 10:48:32

ESD測試臺面搭建,圖中紅圈的電阻需要接嗎。水平和垂直耦合面是要接的,紅圈中為啥也有470k電阻?

2021-03-03 23:20:04

系統級ESD現象和器件級ESD現象有什么差異?ESD事件保護的系統級設計方法有哪幾種?

2021-06-08 07:20:49

能夠承受ESD的沖擊,并繼續正常工作。ESD保護方法為了給電子系統提供ESD保護,可以從不同的角度來著手。一種方法是在半導體芯片內建ESD保護架構。不過,日趨縮小的CMOS芯片已經越來越不足以承受進行

2011-07-05 14:19:03

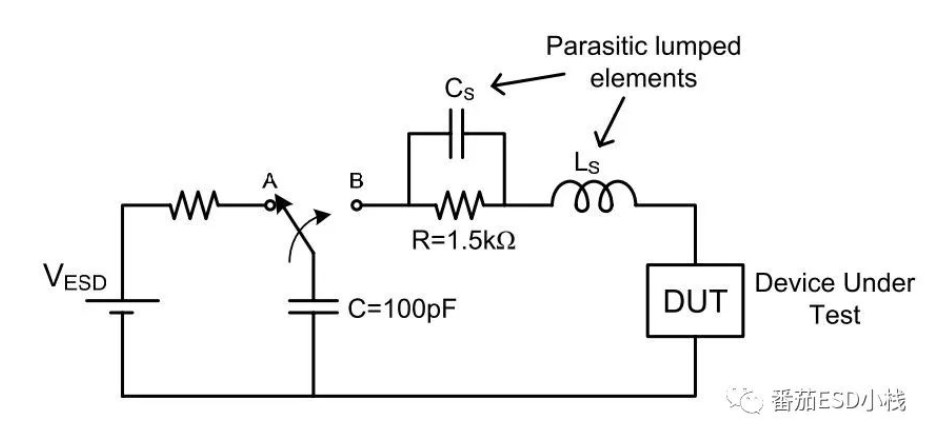

水平,以便使那些采用了對ESD越來越敏感的IC的終端產品保持高可靠性。 ESD波形 以系統級的方法來定義典型的ESD事件所采用的最常見的波形,是以其亞納秒上升時間和高電流電平(參見圖1)為顯著特征

2010-08-18 19:44:07

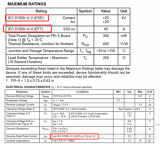

作者: TI專家 Bruce Trump翻譯: TI信號鏈工程師 Michael Huang (黃翔) 我們已經把芯片級的ESD性能寫入數據手冊多年,但這些參數僅適用于在芯片焊接到電路板前。那么在

2018-09-21 09:54:40

原理為了防止ESD損傷芯片,一般芯片內部各個引腳(除GND pin 或NC pin 外)都有對地二極管,簡單的等效電路如下圖所示:利用二極管的正向導通性測試芯片各引腳二極管特性,假設二極管因為ESD 或高壓被反向擊穿造成損壞,那么芯片對應管腳一般表現為對地短路。4)測試方法將萬用表紅表筆接地,黑表

2022-01-18 09:30:14

本帖最后由 testest 于 2020-5-17 20:51 編輯

芯片IC可靠性測試、靜電測試、失效分析芯片可靠性驗證 ( RA)芯片級預處理(PC)& MSL試驗

2020-05-17 20:50:12

芯片IC可靠性測試、靜電測試、失效分析芯片可靠性驗證 ( RA)芯片級預處理(PC) & MSL試驗 、J-STD-020 & JESD22-A113 ;高溫存儲試驗(HTSL

2020-04-26 17:03:32

芯片功能測試常用5種方法有板級測試、晶圓CP測試、封裝后成品FT測試、系統級SLT測試、可靠性測試。

2023-06-09 16:25:42

和功耗。晶圓級芯片級封裝(WLCSP)的運用對減小這些設備電子組件的尺寸起到了極大的助推作用。此類新型應用包括介入性檢測、醫學植入體和一次性便攜式監護儀。但是為了最大限度地發揮出WLCSP封裝在性能

2018-10-17 10:53:16

`看到這篇對GALAXY S5的拆解,感覺真是到位,所有的元器件都列出來了iFixit、ChipWorks是一對好基友網站,前者擅長拆解維修,后者專精芯片級分析與顯微觀察。對于某一款設備,通常都是

2014-04-14 23:06:26

本帖最后由 eehome 于 2013-1-5 09:54 編輯

芯片級拆解:剖析新型LED燈泡設計的藝術

2012-08-20 19:45:33

芯片級維修資料分享(一)關于臺式機主板維修分享

2019-08-28 14:47:21

AD7793,想請問一下INL的測試采用什么方法比較合理?

2023-12-01 07:30:13

的性能指標,設計有效的方法來測試。實際上入侵檢測系統的測試是一個難度較大的問題,也是一件費時耗力的工作。對于這一工作,許多研究機構都進行了相應的研究,給出了自己的測試方法和測試結果。例如MIT的林肯實驗室

2019-08-19 06:55:17

第二章 驗證flow驗證的Roadmap驗證的目標UVM驗證方法學ASIC驗證分解驗證策略和任務的分解AMBA可重用、靈活性、兼容性、廣泛支持一.驗證的Roadmap1.ASIC芯片項目流程市場需求

2021-11-01 06:28:47

晶圓級芯片級封裝; 49 bumps; 3.29×3.29×0.54mm(包括背面涂層)

2022-12-06 06:06:48

PCB布板時的ESD保護設計方法是什么?

2023-04-06 17:49:21

SiC SBD 晶圓級測試 求助:需要測試的參數和測試方法謝謝

2020-08-24 13:03:34

USB元件提供ESD保護。 業界制定了不少針對不同瞬態干擾的ESD標準,比如針對系統級ESD事件的IEC61000-4-2國際標準。另外還有一些元器件級的ESD敏感度測試標準,如人體模型(HBM)和機器

2013-12-27 16:21:39

【芯片級維修工程師】電腦主板維修范例大全 下載 (474.94 KB)2010-11-28 17:16 本帖隱藏的內容需要

2010-12-02 21:47:40

`iPhone4S手機芯片級拆解`

2012-08-20 21:09:03

Circuits第 3 頁 共 127 頁8.2 動態浮接閘級之ESD 防護技術

2011-02-24 09:55:18

。芯片級一般用HBM做測試,而電子產品則用IEC 6 1000-4-2的放電模型做測試。為對 ESD 的測試進行統一規范,在工業標準方面,歐共體的 IEC 61000-4-2 已建立起嚴格的瞬變沖擊抑制標準

2019-04-23 16:38:13

;該系統主要被用于產品的研發與測試分析 這一類ESD 可以理解為板級的ESD 3. 隨著中美貿易不斷升級,2017年開始國家加大半導體,芯片等相關公司的投資, 在武漢,廈門 合肥 南京 杭州成都等城市

2020-02-29 16:39:46

。生產嵌入式芯片的廠家也已有百家之多。然而,嵌入式芯片的應用開發方式基本上還是一直采用基于芯片級的應用開發方式。由于不同生產廠家生產的芯片其系統構架和指令系統不一樣,嵌入式芯片應用的多樣性和廣泛性導致

2012-11-19 11:53:48

進行芯片級拆解與比對,詳細的拆解進行橫向比較,為您更清楚地揭示其中的微妙差異。Nook Table這里我們為您呈現的是Nook Tablet,這個薄板有很酷的一個大夾子。同樣,它的內部也很酷,我們來看

2012-02-03 14:54:54

什么是EMI?ESD噪聲抑制方法有哪些?

2021-06-04 06:36:14

本帖最后由 eehome 于 2013-1-5 09:46 編輯

保護元件免受ESD的方法 為了給電子系統提供ESD保護,可以從不同的角度來著手。一種方法是在半導體芯片內建ESD保護架構

2013-01-04 14:58:24

為了給電子系統提供ESD保護,可以從不同的角度來著手。一種方法是在半導體芯片內建ESD保護架構。不過,日趨縮小的CMOS芯片已經越來越不足以承受進行內部2KV等級的ESD保護所需要的面積。真正有效

2014-02-14 10:30:16

時鐘頻率的不斷提高使相位噪聲和抖動在系統時序上占據日益重要的位置。本文介其概念及其對系統性能的影響,并在電路板級、芯片級和單元模塊級分別提供了減小相位噪聲和抖動的有效方法。

2019-06-05 07:13:30

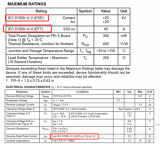

[/td][td=140]芯片級系統級上升時間2-10ns0.7-1ns峰值電流/KV0.66A3.75A2.測試設備不同MK2-芯片級靜電槍-系統級3.測試方法不同芯片級HBM測試需要對IC按照

2020-10-16 16:36:22

0.7-1ns峰值電流/KV0.66A3.75A2.測試設備不同,MK2芯片級,靜電槍系統級3.測試方法不同芯片級HBM測試需要對IC按照POWER,GND,IO進行分組測試系統級HBM測試分成兩種方式:1

2022-09-19 09:53:25

。芯片級一般用HBM做測試,而電子產品則用IEC 6 1000-4-2的放電模型做測試。為對 ESD 的測試進行統一規范,在工業標準方面,歐共體的 IEC 61000-4-2 已建立起嚴格的瞬變沖擊抑制標準

2021-08-10 07:00:00

我們已經把芯片級的ESD 性能寫入數據手冊多年, 但這些參數僅適用于在芯片焊接到電路板前。那么在電路板上的ESD性能如何呢?

2021-04-09 06:00:54

基于無線測試配置來研究和比較各種多DUT測試方案

2021-05-10 06:44:44

摘要:文中通過分析目前電子設備板級熱仿真建模技術存在的不足,基于設計數據共享技術,系統研究了PCB 板卡的疊層銅分布和熱過孔仿真建模對芯片溫度預測精度帶來的較大影響,并結合實際應用給出了仿真優化

2018-09-26 16:22:17

對于單顆的芯片,目的驗證其從封裝完成,經過儲存、運輸直到焊接到系統板之前的靜電防護水平,建議采用芯片級的測試方式,測試電壓通常在2000V左右。對于系統板和整機,為驗證其抗干擾的能力,建議用靜電槍測試,接觸式放電8KV,空氣放電15KV.

2022-09-19 09:57:03

過關,不過,對小型電子產品進行靜電屏蔽也比較容易,只需在機殼上面貼一層薄薄的導電薄膜(或涂一層可導電的油漆)即可,因此,對敏感器件進行靜電屏蔽是小型電子產品對付ESD測試比較常用的方法。

2021-01-08 16:08:07

脈沖有沒有正確送到CPU芯片的復位腳。 4.查總線 數據總線、地址總線、控制總線的任何一根開路或短路都可引發故障,可以通過測試平行總線的對地電阻比較某路有沒有故障來判斷,或者觀察各路總線的波形來判斷。 5.查接口芯片 接口芯片是壞得最多的一類元件,可通過代換或專用儀器檢測來判斷是否損壞

2012-04-18 16:31:12

的集成度。現在一塊單一的芯片就集成了從ADC轉換到中頻調制輸出的大部分功能。因此,模塊級和芯片級的射頻測試點會減少很多,發射器系統級和天線端的測試和故障分析就變得更加重要。

2019-06-28 07:44:08

Ramon Navarro簡介本應用筆記說明用于從印刷電路板(PCB)移除引線框芯片級封裝(LFCSP)的建議程序。LFCSP符合JEDEC MO-220和MO-229外形要求。本應用筆

2018-10-24 10:31:49

怎樣在IAP源碼的基礎上做芯片級的改動呢?STM32的啟動過程是怎樣的?

2021-11-02 06:13:23

面積,而硅片面積的增加增大了IC設計的成本。 當前,新的ESD設計技術解決了這個問題:鎮流電阻可以通過高效的面積使用方法來實現。新的設計方法能確保實現較小的I/O,更小的IC芯片尺寸,因而每一個晶圓上

2012-12-11 13:39:47

你好,我尋求CSG325 0.8mm間距BGA封裝的布局信息。我想找到類似于UG112第87和88頁中的建議,其中列出了焊盤尺寸,焊接掩模開口,焊盤尺寸等。是否有像CSG325這樣的芯片級封裝的類似

2019-04-12 13:51:20

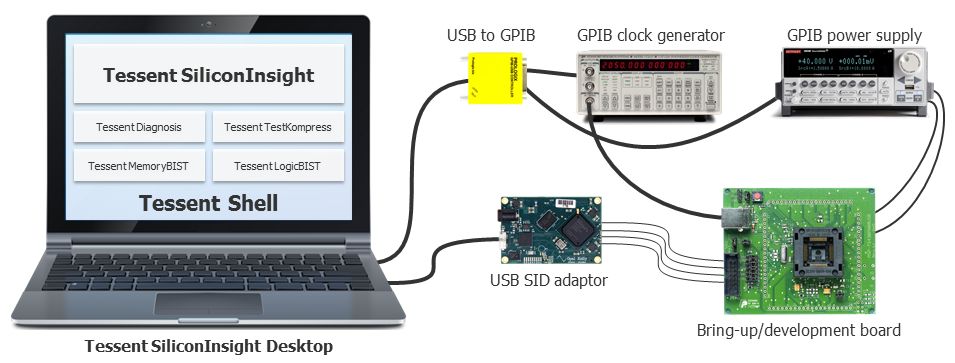

如何利用EDA工具去提高系統級芯片測試的效率?

2021-05-07 06:08:41

。這一規范的ESD保護電壓水平高很多,因此與HBM不兼容。HBM規范要求的測試集中在500V。另一方面,IEC中的空氣放電方法要求的測試可以超過15,000V。這意味著,在芯片組的ESD保護能力

2019-05-22 05:01:12

`淺析ESD 防護與ESD 防護器件中心議題:? 靜電釋放的危害和ESD 保護的重要性? 相對于壓敏MOV和聚合物PESD,硅基ESD 在ESD 保護方面的比較優勢解決方案:?硅基ESD采用硅芯片

2017-07-31 14:59:33

本帖最后由 llgzcts 于 2012-4-8 01:22 編輯

介紹一個關于電腦主板維修的好資料的下載地址:電腦硬件芯片級維修培訓實用資料大全(650M)實用資料打包下載網實用資料打包下載網

2012-04-08 01:03:34

。芯片級一般用HBM做測試,而電子產品則用IEC 6 1000-4-2的放電模型做測試。為對 ESD 的測試進行統一規范,在工業標準方面,歐共體的 IEC 61000-4-2 已建立起嚴格的瞬變沖擊抑制

2020-07-07 08:26:54

等。芯片級一般用HBM做測試,而電子產品則用IEC 6 1000-4-2的放電模型做測試。為對 ESD 的測試進行統一規范,在工業標準方面,歐共體的 IEC 61000-4-2 已建立起嚴格的瞬變沖擊

2018-10-23 16:08:45

。芯片級一般用HBM做測試,而電子產品則用IEC 6 1000-4-2的放電模型做測試。為對 ESD 的測試進行統一規范,在工業標準方面,歐共體的 IEC 61000-4-2 已建立起嚴格的瞬變沖擊抑制標準

2019-04-27 08:00:00

計算機芯片級維修中心(芯片級維修培訓教材)

2009-04-05 01:17:54

SRAM中晶圓級芯片級封裝的需求

2020-12-31 07:50:40

金屬觸點ESD測試問題像圖中這種串口通訊觸點(4.2V,TX,RX),如果還是不能通過空氣放電15KV,接觸放電8KV,然后板子空間有限,這種情況如何改善能一步通過ESD測試?

2023-02-02 11:01:38

飛凌干貨丨6步講解應對ESD基本方法ESD試驗作為EMC測試標準的一項基本測試項目,往往由硬件工程師來考慮。對于整機來說,ESD抗干擾能力不僅僅來自芯片的ESD耐壓和PCB的布局布線,與工藝結構也有

2021-02-07 13:22:05

(full-waverectifiers)等。 1 比較器的設計 本文設計的比較器是一個高增益的三級比較器,第一級為普通差分放大器,第二級為折疊式共源共柵差分放大器,第三級為共源極放大器和一個推挽式反向放大器

2011-08-18 09:20:12

摘要:介紹了一種研究器件和電路結構在EsD期間新的特性測試方法—一TLP法,該方法不僅可替代HBM測試,還能幫助電路設計師詳細地分析器件和結構在ESD過程中的運行機制,有目的

2010-04-29 10:48:53 29

29 福祿克DTX-1800維修維修內容:主機屏幕爆屏、無法開機、測試指標偏移、無法充電、適配器接口損壞更換、電池內阻增大更換、原廠校準、芯片級維修等,各種疑難雜癥。

2023-10-10 16:11:30

服務范圍大規模集成電路芯片檢測標準●JESD22-A103/ A104/ A105/ A108/ A110●J-STD-020●JS-001/002●JESD78檢測項目(1)芯片級可靠性驗證試驗

2024-03-14 16:28:30

論述了一種測試混合信號集成電路襯底噪聲波形的方法采用電壓比較器利用襯底電壓對比

較器狀態的影響對噪聲作出統計測試根據測試結果重建噪聲波形設計了一

2010-08-29 16:08:46 14

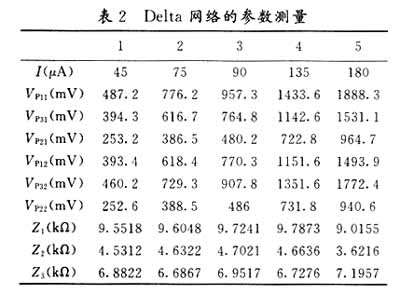

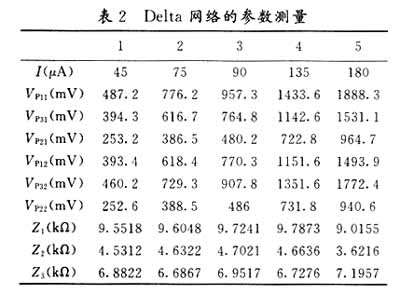

14 基于IEEE1149.4的測試方法研究

根據混合信號邊界掃描測試的工作機制,提出了符合1149.4標準的測試方法,并用本研究室開發的混合信號邊界掃描測試系統進行了測試

2009-05-04 22:29:18 1007

1007

測試一直是靜電與電磁防護研究的瓶頸. 針對ESD 輻射場 測試問題, 提出了能量有效帶寬和動態范圍有效帶寬的概念, 并根據IEC61000

2011-06-20 16:45:24 29

29 《開關電源維修技能實訓:芯片級》共8章,系統講解了電源中的各種元器件的檢測方法及常用維修工具的使用方法、基本電路、電腦電源分析與檢修、顯示器電源分析與檢修、UPS電源分

2011-10-21 17:10:14 0

0 清晰易懂 表明esd如何發生,如何避免esd

2016-02-22 18:05:45 0

0 蓄電池測試系統中SVPWM與SPWM的比較研究

2016-03-30 14:59:59 15

15 ESD模型和測試標準

2016-12-10 14:02:20 17

17 基于電壓比較器襯底噪聲的測試方法

2017-01-22 13:38:08 5

5 IT硬件能耗測試方法應用研究_黃植勤

2017-03-19 11:27:34 2

2 STUN協議的實現原理及測試方法研究_吳任國

2017-03-19 11:28:02 0

0 MEMS制造中精確測量薄膜厚度的方法研究與比較_陳莉

2017-03-19 18:58:18 2

2 翻譯: TI信號鏈工程師 Michael Huang (黃翔) 我們已經把芯片級的ESD性能寫入數據手冊多年,但這些參數僅適用于在芯片焊接到電路板前。那么在電路板上的ESD性能如何呢? 我們用多次電擊若干個芯片的每個引腳的方法來確保其ESD性能。它模擬了在觸摸和裝配過程中芯片遭遇的惡劣情景。

2017-04-08 04:09:11 2932

2932

CE標志測試以滿足歐共體理事會指令89/336/EEC要求測試根據EN 61000-4-2。EN 61000-4-2是由CENELEC和他們使用IEC標準IEC 61000-4-2作為ESD測試標準

2017-08-31 11:05:20 33

33 ADI公司的iCoupler產品提供了一種替代光耦合器的隔離 解決方案,具有出色的集成度、性能和功耗特性。一個 iCoupler隔離通道包括CMOS輸入和輸出電路與一個芯片級 變壓器(見圖1)。由于

2017-09-13 08:08:03 4

4 每一個輸入/輸出相對于其他所有的輸入/輸出的正向ESD脈沖測試。

2018-11-24 09:23:07 17325

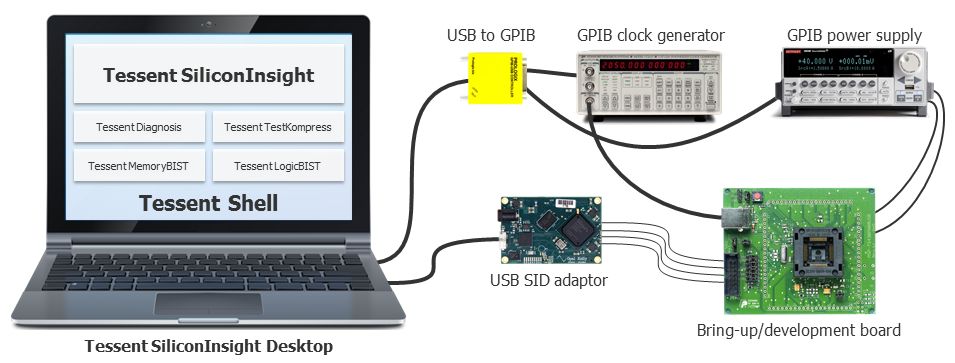

17325 盡管業界廣泛采用IJTAG(IEEE 1687)測試架構進行芯片級測試,但很多公司在芯片級測試向量轉換,以及自動測試設備 (ATE) 調試測試保留了非常不同的方法。因此,每個特定芯片必須由 DFT 工程師編寫測試向量,然后由測試工程師進行轉換,以便在每種測試儀類型上調試每個場景。

2019-10-11 15:36:23 3515

3515

芯片級守護 華為P30系列如何從底層保證通信安全?

2019-08-28 11:18:28 3901

3901 在做ESD放電測試時通常采用兩種方法:接觸放電和空氣放電。

2019-09-02 08:49:24 4173

4173

根據AEC-Q200-002,HBM的ESD測試流程如圖3所示,級分類如表1所示。根據圖3的流程進行測試,耐電壓的分級如表1所示進行分類。

2020-07-01 15:33:31 3731

3731

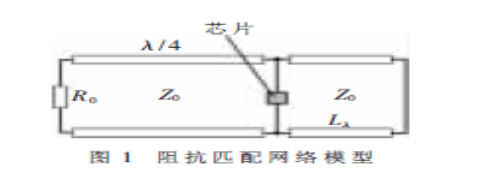

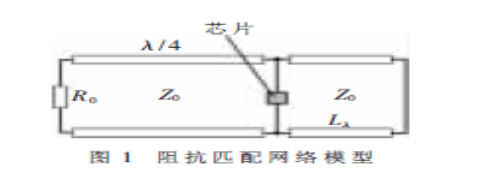

提出一種用于UHF無源RFID標簽芯片阻抗測試的新方法。利用ADS仿真軟件對測試原理進行了仿真并實際制作了測試板。利

2021-03-22 17:16:21 3021

3021

作者: TI專家 Bruce Trump

翻譯: TI信號鏈工程師 Michael Huang (黃翔)?

?

我們已經把芯片級的ESD性能寫入數據手冊多年,但這些參數僅適用于在芯片焊接

2021-11-22 16:13:17 2835

2835 Fairchild 模擬開關產品 ESD 測試方法概述

2022-11-14 21:08:28 0

0 ESD和浪涌問題往往是基帶工程師最頭疼的問題,因為測試標準嚴苛,問題神出鬼沒。特別是ESD問題,沒有解決問題的標準路徑,只能靠反復地構思方案并驗證。

2023-03-14 14:36:20 12660

12660 ESD按照發生階段主要分為兩類:1.發生在芯片上PCB板前的過程中(生產 、封裝、運輸、銷售、上板)這類ESD事件完全需要由芯片自己承受。

2023-05-16 16:21:31 7698

7698

芯片功能測試常用5種方法有板級測試、晶圓CP測試、封裝后成品FT測試、系統級SLT測試、可靠性測試。

2023-06-09 15:46:58 1666

1666

ESD靜電放電在芯片實際使用過程中越來越影響到芯片的可靠性,是影響芯片質量和性能的重要因素之一。因此,ESD抗干擾測試是非常重要的,防止ESD對芯片造成損壞。

2023-10-08 16:24:01 565

565 ESD和浪涌問題往往是基帶工程師最頭疼的問題,因為測試標準嚴苛,問題神出鬼沒。特別是ESD問題,沒有解決問題的標準路徑,只能靠反復地構思方案并驗證。

想要盡量避免以上問題,就必須選擇合適的防護器件,設計上做足防護措施。本文告訴你ESD和浪涌的測試標準,測試方法,以及如何選擇TVS器件。

2023-10-09 12:18:28 2401

2401

電子發燒友網站提供《IEC61967-2芯片級RE測試應用筆記.pdf》資料免費下載

2023-12-14 10:03:06 0

0

電子發燒友App

電子發燒友App

評論