Cadence系統(tǒng)芯片開發(fā)工具已經(jīng)通過(guò)臺(tái)積電(TSMC) 16納米 FinFET制程的設(shè)計(jì)參考手冊(cè)第0.1版與 SPICE 模型工具認(rèn)證,客戶現(xiàn)在可以享用Cadence益華電腦流程為先進(jìn)制程所提供的速度、功耗與面積優(yōu)勢(shì)。

2013-06-06 09:26:45 1236

1236 :00-16:00FSP 實(shí)例演示PSpice AA 高級(jí)分析工具的使用第二期:2013年04月09日14:00-16:00PCB過(guò)孔對(duì)信號(hào)傳輸?shù)挠绊懸约癡IA模型提取(I)PSpice模型的創(chuàng)建第三期

2013-01-11 11:23:33

分享最新的Cadence技術(shù)。詳情請(qǐng)參考會(huì)議日程和相關(guān)主題演講介紹。誰(shuí)應(yīng)該參加:? Cadence Allegro/Sigrity產(chǎn)品用戶? PCB設(shè)計(jì)工程師和管理者? 信號(hào)完整性分析工程師? 電源仿真及設(shè)計(jì)工

2015-05-19 10:19:07

制造等領(lǐng)域系統(tǒng)地、有機(jī)地進(jìn)行設(shè)計(jì)和仿真自動(dòng)化一直是許多設(shè)計(jì)、仿真人員和企業(yè)管理人員所面臨的難題。科通作為Cadence在中國(guó)區(qū)的代理商,現(xiàn)誠(chéng)邀您參加“ 2016 Cadence SPB17.2專題研討

2016-07-08 16:51:10

CADENCE PCB軟件介紹復(fù)雜的物理和電氣規(guī)則,高密度的元器件布局,以及更高的高速技術(shù)要求,這一切都增加了當(dāng)今PCB設(shè)計(jì)的復(fù)雜性,不管是在設(shè)計(jì)過(guò)程的哪一個(gè)階段,設(shè)計(jì)師都需要能夠輕松地定義,管理

2008-06-12 00:54:48

設(shè)計(jì)流程和方法。如何實(shí)現(xiàn)跨平臺(tái)、跨部門、跨工藝制造等領(lǐng)域系統(tǒng)地、有機(jī)地進(jìn)行設(shè)計(jì)和仿真自動(dòng)化一直是許多設(shè)計(jì)、仿真人員和企業(yè)管理人員所面臨的難題。科通作為Cadence在中國(guó)區(qū)的代理商,現(xiàn)誠(chéng)邀您參加

2016-07-06 13:18:36

我們對(duì)PCB市場(chǎng)的承諾。” Allegro PCB PI選項(xiàng)可吸收來(lái)自IC及IC封裝設(shè)計(jì)工具的封裝寄生現(xiàn)象、裸片電容和轉(zhuǎn)換電流,以精確建立完整的電源供應(yīng)系統(tǒng)。結(jié)合靜態(tài)IR降分析,Allegro PCB PI用戶可以快速判斷電源分配系統(tǒng)是否能維持規(guī)范所述參考電壓。:

2018-11-23 17:02:55

Cadence工具VirtusoDracula入門介紹Cadence工具Virtuso/Dracula入門介紹.... 21.使用 Virtuso/Diva/Dracula之前的準(zhǔn)備

2012-08-10 18:39:06

很多,規(guī)則等一時(shí)半會(huì)兒都不太會(huì)理解,相比于其他的一些電路板設(shè)計(jì)軟件,由于它的功能較多,這樣學(xué)習(xí)起來(lái)就可以規(guī)則化,在設(shè)計(jì)過(guò)程中,都是很嚴(yán)謹(jǐn)?shù)模啾扔谄渌浖瑫?huì)感覺(jué)比較繁瑣,但是只要學(xué)會(huì)用Cadence,很多PCB設(shè)計(jì)的問(wèn)題都可以使用它來(lái)解決了。

2019-01-22 15:47:53

Cadence設(shè)計(jì)系統(tǒng)有限公司宣布推出業(yè)界第一套完整的能夠推動(dòng)SiPIC設(shè)計(jì)主流化的EDA產(chǎn)品。Cadence解決方案針對(duì)目前SiP設(shè)計(jì)中依賴‘專家工程’的方式存在的固有局限性,提供了一套自動(dòng)化

2008-06-27 10:24:12

選項(xiàng)可吸收來(lái)自IC及IC封裝設(shè)計(jì)工具的封裝寄生現(xiàn)象、裸片電容和轉(zhuǎn)換電流,以精確建立完整的電源供應(yīng)系統(tǒng)。結(jié)合靜態(tài)IR降分析,Allegro PCB PI用戶可以快速判斷電源分配系統(tǒng)是否能維持規(guī)范所述

2018-08-28 15:28:45

來(lái)自IC及IC封裝設(shè)計(jì)工具的封裝寄生現(xiàn)象、裸片電容和轉(zhuǎn)換電流,以精確建立完整的電源供應(yīng)系統(tǒng)。結(jié)合靜態(tài)IR降分析,Allegro PCB PI用戶可以快速判斷電源分配系統(tǒng)

2008-06-19 09:36:24

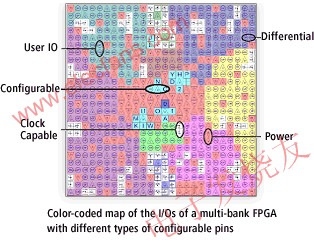

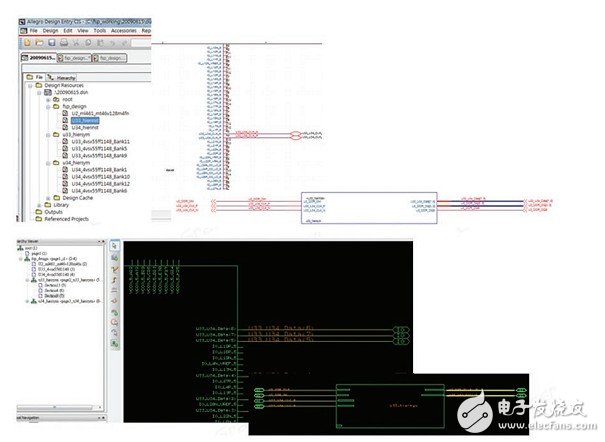

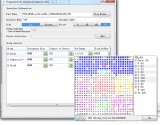

進(jìn)行自動(dòng)分配、信號(hào)標(biāo)準(zhǔn)監(jiān)督、簡(jiǎn)單拖放分配、支持操作對(duì)象集以及動(dòng)態(tài)篩選。總之,其可簡(jiǎn)化信號(hào)管腳分配操作流程。每次管腳分配更改均通過(guò) FPGA-PCB 流程管理,無(wú)論更改了哪些地方,均可保持一致。自動(dòng)化

2018-09-20 11:11:16

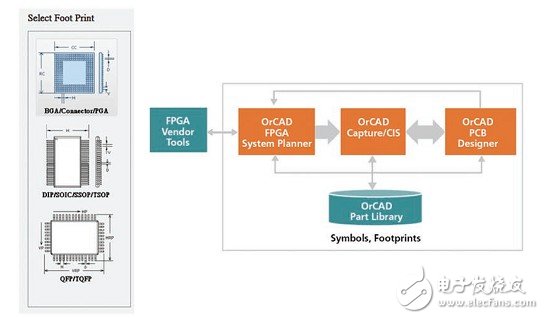

本帖主要介紹Cadence軟件FPGA System Planner(FSP)使用,以連載的方式提供。希望能給到大家一點(diǎn)幫助。FSP工具是cadence公司為了FPGA/PCB協(xié)同設(shè)計(jì)而推出的一個(gè)

2011-10-18 11:44:31

電子發(fā)燒友網(wǎng)訊:可編程邏輯廠商逐步開始從可編程邏輯芯片供應(yīng)商向可編程邏輯系統(tǒng)商完成華麗轉(zhuǎn)身,正對(duì)EDA工具供應(yīng)商提出更高的要求,如集成化和系統(tǒng)化程度越來(lái)越高、邏輯設(shè)計(jì)功能日趨復(fù)雜、對(duì)軟硬件驗(yàn)證

2013-04-17 11:20:14

作為一個(gè)負(fù)責(zé)FPGA企業(yè)市場(chǎng)營(yíng)銷團(tuán)隊(duì)工作的人,我不得不說(shuō),由于在工藝技術(shù)方面的顯著成就以及硅芯片設(shè)計(jì)領(lǐng)域的獨(dú)創(chuàng)性,FPGA正不斷實(shí)現(xiàn)其支持片上系統(tǒng)設(shè)計(jì)的承諾,那FPGA設(shè)計(jì)工具目前究竟發(fā)展到了什么程度呢?

2019-08-01 08:15:46

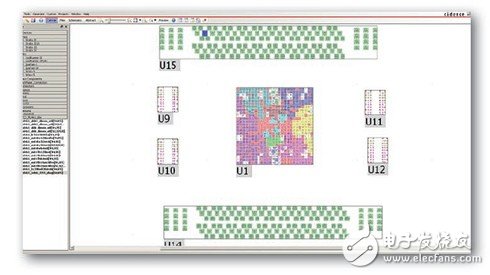

復(fù)雜度日益增加的系統(tǒng)設(shè)計(jì)要求高性能FPGA的設(shè)計(jì)與PCB設(shè)計(jì)并行進(jìn)行。通過(guò)整合FPGA和PCB設(shè)計(jì)工具以及采用高密度互連(HDI)等先進(jìn)的制造工藝,這種設(shè)計(jì)方法可以降低系統(tǒng)成本、優(yōu)化系統(tǒng)性能并縮短

2018-09-21 11:55:09

PCB設(shè)計(jì)所面對(duì)的挑戰(zhàn),以及作為一名PCB設(shè)計(jì)者在評(píng)估一個(gè)PCB設(shè)計(jì)工具時(shí)該考慮哪些因素。 下面是PCB設(shè)計(jì)者務(wù)必考慮并將影響其決定的幾點(diǎn)因素: 1.產(chǎn)品功能 A.籠蓋基本要求的基本功能,包括

2013-05-14 16:48:23

Cadence PCB設(shè)計(jì)仿真技術(shù)Cadence PCB設(shè)計(jì)仿真技術(shù)提供了一個(gè)全功能的模擬仿真器,并支持?jǐn)?shù)字元件幫助解決幾乎所有的設(shè)計(jì)挑戰(zhàn),從高頻系統(tǒng)到低功耗IC設(shè)計(jì),這個(gè)強(qiáng)大的仿真引擎可以容易地同

2008-06-12 00:57:27

;Cadence 包含的工具較多幾乎包括了EDA 設(shè)計(jì)的方方面面本小冊(cè)子<br/>旨在向初學(xué)者介紹Cadence 的入門知識(shí)所以不可能面面具到只能根據(jù)ASIC<

2008-07-12 23:11:21

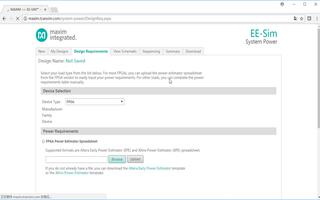

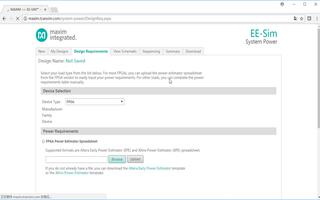

的,如果再加上英文差一點(diǎn)的,會(huì)掉入各種大坑,從而打消積極性,讓自己苦惱!本文為大家介紹一款TI的在線電源設(shè)計(jì)工具主要功能如下: 1.直觀可視化 2.可仿真...

2021-12-31 06:46:12

的廠家很多,但最有代表性的廠家為 Altera、Xilinx 和 Lattice 公司。CPLD/FPGA 的開發(fā)工具一般由器件生產(chǎn)廠家提供,但隨著器件規(guī)模的不斷增加,軟件的復(fù)雜性也隨之提高,目前由專門

2019-03-04 14:10:13

`現(xiàn)在電子發(fā)燒友推出的DigiPCBA——一款便捷高效硬件項(xiàng)目協(xié)同設(shè)計(jì)工具幫您實(shí)現(xiàn)專屬夢(mèng)想。一款便捷高效硬件項(xiàng)目協(xié)同設(shè)計(jì)工具,搶先體驗(yàn)免費(fèi)注冊(cè):https://digipcba.com/?hmsr

2021-03-18 11:04:29

;2<br/>序 言<br/>Cadence 軟件是我們公司統(tǒng)一使用的原理圖設(shè)計(jì)、PCB 設(shè)計(jì)、高速仿真、自動(dòng)布線的EDA 工具。本篇<

2009-08-17 14:00:19

下出按用途對(duì)IC設(shè)計(jì)軟件作一些介紹。IC設(shè)計(jì)工具很多,其中按市場(chǎng)所占份額排行為Cadence、Mentor Graphics和Synopsys。這三家都是ASIC設(shè)計(jì)領(lǐng)域相當(dāng)有名的軟件供應(yīng)商。其它

2012-01-10 10:07:31

設(shè)計(jì))2.FPGA-PCB一體化設(shè)計(jì),業(yè)界最先進(jìn),自動(dòng)優(yōu)化網(wǎng)絡(luò),提高效率(可由幾天減少到幾小時(shí)),減少錯(cuò)誤(內(nèi)嵌最新FPGA器件模型和信息)。(Cadence的工具比較初級(jí))3.仿真,HyperLynx仿真工具市場(chǎng)占有率

2014-10-28 14:06:53

接口,協(xié)同設(shè)計(jì))★庫(kù)和設(shè)計(jì)數(shù)據(jù)管理問(wèn)題★信號(hào)完整性,電源分布網(wǎng)絡(luò)及EMC解決方案★FPGA-PCB協(xié)同設(shè)計(jì)能力★設(shè)計(jì)規(guī)劃和布線新技術(shù)★深層次解讀PSpice新技術(shù) 會(huì)議地點(diǎn)安排:上海時(shí)間: 11月27

2012-10-26 11:18:34

系統(tǒng)FPGA的pin腳分配上達(dá)成一致。在這次研討會(huì)中,你將會(huì)了解FSP和Allegro結(jié)合xilinx平臺(tái)在短時(shí)間內(nèi)正確無(wú)誤的完成設(shè)計(jì),這樣既可以節(jié)省更多設(shè)計(jì)時(shí)間又可減少PCB設(shè)計(jì)層數(shù)。您將有什么收獲

2012-03-28 10:04:23

和應(yīng)用技巧的分享。全書共分17章,主要內(nèi)容以PCB設(shè)計(jì)流程為線索,以某項(xiàng)目實(shí)例為基礎(chǔ),介紹從原理圖設(shè)計(jì)、設(shè)計(jì)環(huán)境定義、封裝庫(kù)建立、數(shù)據(jù)導(dǎo)入,到PCB的布局、布線、疊層阻抗設(shè)計(jì)、約束管理器使用、多人協(xié)同

2017-08-11 17:11:31

本帖最后由 lee_st 于 2017-11-2 15:01 編輯

《FPGACPLD設(shè)計(jì)工具──Xilinx+ISE使用詳解》第 1 章 ISE 系統(tǒng)簡(jiǎn)介

2017-11-02 10:02:32

零知PCB是零知實(shí)驗(yàn)室出品的一款PCB設(shè)計(jì)工具,包含了原理圖設(shè)計(jì)、PCB布局,并自帶豐富的封裝和符號(hào)庫(kù)。針對(duì)當(dāng)前一些PCB軟件收費(fèi)、版權(quán)、使用復(fù)雜等問(wèn)題,我們?cè)O(shè)計(jì)了此PCB設(shè)計(jì)工具,具有高效、便捷

2019-09-09 10:20:25

消費(fèi)類產(chǎn)品中日益增長(zhǎng)的模擬器件數(shù)量、當(dāng)今的設(shè)計(jì)規(guī)模以及先進(jìn)工藝節(jié)點(diǎn)所面臨的愈加復(fù)雜的制造約束,使得模擬設(shè)計(jì)領(lǐng)域?qū)ψ詣?dòng)化設(shè)計(jì)工具的企盼更加迫切。 自動(dòng)化設(shè)計(jì)工具的目標(biāo)是使模擬版圖設(shè)計(jì)人員能夠簡(jiǎn)單自動(dòng)

2019-07-08 06:00:51

和具體操作方法。最后通過(guò)一個(gè)完整的案例全面展示對(duì)整個(gè)單板進(jìn)行系統(tǒng)化信號(hào)完整性設(shè)計(jì)的執(zhí)行步驟和操作方法。課程對(duì)象從事硬件開發(fā)部門主管、硬件項(xiàng)目負(fù)責(zé)人、SI工程師、硬件開發(fā)工程師、PCB設(shè)計(jì)工程師、測(cè)試

2016-05-05 14:26:26

`再談設(shè)計(jì)工具FPGA的優(yōu)勢(shì)FPGA最大的優(yōu)勢(shì)特點(diǎn)就是能夠縮短開發(fā)所需時(shí)間。 換句話說(shuō),通過(guò)使用FPGA,設(shè)計(jì)人員可以有效地利用每一分鐘進(jìn)行開發(fā)。例如,在開發(fā)過(guò)程中使用FPGA與否,可以導(dǎo)致開發(fā)時(shí)間

2012-02-24 17:26:23

Cadence PCB設(shè)計(jì)仿真技術(shù)提供了一個(gè)全功能的模擬仿真器,并支持?jǐn)?shù)字元件幫助解決幾乎所有的設(shè)計(jì)挑戰(zhàn),從高頻系統(tǒng)到低功耗IC設(shè)計(jì),這個(gè)強(qiáng)大的仿真引擎可以容易地同各個(gè)Cadence PCB原理圖

2019-10-10 23:01:33

器分冊(cè):主要闡述用Allegro SPB15.2 的PCB Router 對(duì)PCB 進(jìn)行自動(dòng)布線的過(guò)程。還包括一篇總論,在總論中介紹了Cadence 的系統(tǒng)組成和設(shè)計(jì)環(huán)境、安裝步驟和庫(kù)管理等內(nèi)容。每

2013-06-20 17:10:06

摘要:簡(jiǎn)要介紹了軟硬件協(xié)同仿真技術(shù),指出了在大規(guī)模FPGA開發(fā)中軟硬件協(xié)同仿真的重要性和必要性,給出基于Altera FPGA的門級(jí)軟硬件協(xié)同仿真實(shí)例。 關(guān)鍵詞:系統(tǒng)級(jí)芯片設(shè)計(jì);軟硬件協(xié)同仿真

2019-07-04 06:49:19

如何使用半自動(dòng)化設(shè)計(jì)工具。這些工具對(duì)于電源設(shè)計(jì)工程師新手和專家都很有價(jià)值。

2021-09-29 10:51:53

如何實(shí)現(xiàn)一體化芯片-封裝協(xié)同設(shè)計(jì)系統(tǒng)的設(shè)計(jì)?如何優(yōu)化封裝和芯片接口設(shè)計(jì)?

2021-04-21 07:01:10

EDA技術(shù)是在電子CAD技術(shù)基礎(chǔ)上發(fā)展起來(lái)的計(jì)算機(jī)軟件系統(tǒng),是指以計(jì)算機(jī)為工作平臺(tái),融合了應(yīng)用電子技術(shù)、計(jì)算機(jī)技術(shù)、信息處理及智能化技術(shù)的最新成果,進(jìn)行電子產(chǎn)品的自動(dòng)設(shè)計(jì)。利用EDA工具,可以將

2018-10-17 11:48:12

工程師離不開的那些電路設(shè)計(jì)工具,你用過(guò)幾個(gè)? EDA技術(shù)是在電子CAD技術(shù)基礎(chǔ)上發(fā)展起來(lái)的計(jì)算機(jī)軟件系統(tǒng),是指以計(jì)算機(jī)為工作平臺(tái),融合了應(yīng)用電子技術(shù)、計(jì)算機(jī)技術(shù)、信息處理及智能化技術(shù)的 最新成果

2020-04-21 15:02:31

洗牌,上面的幾家公司進(jìn)行了重組! 從市場(chǎng)占有率來(lái)說(shuō).Mentor公司現(xiàn)在最高,Cadence公司第二,Zuken 公司第三。單個(gè)的PCB工具,Allegro在中國(guó)高端用戶中軟件占有率應(yīng)該是最高的,其次

2015-02-02 14:19:37

潛在風(fēng)險(xiǎn),仿真及設(shè)計(jì)控制等多種手段并用。總之,系統(tǒng)化信號(hào)完整性設(shè)計(jì)方法,是設(shè)計(jì)PCB而不是簡(jiǎn)單仿真PCB。文章轉(zhuǎn)載于博士信號(hào)完整性網(wǎng)站http://www.sig007.cn關(guān)注于博士信號(hào)完整性微信公眾號(hào) zdcx007了解更多PCB設(shè)計(jì)知識(shí)

2017-06-23 11:52:11

國(guó)內(nèi)后開始加大盜版打擊力度。官方網(wǎng)站:官方軟件下載官方提供的庫(kù)文件和設(shè)計(jì)資源下載CadenceOrCad:歷史很悠久的經(jīng)典PCB設(shè)計(jì)工具,可有全功能的免費(fèi)版本做體驗(yàn),都是Cadence旗下的工具,應(yīng)該跟

2019-08-29 17:58:29

Cadence Allegro SPB16.5版本安裝后各工具介紹,工具太多了,對(duì)于初學(xué)者的我有些茫然。請(qǐng)大家給個(gè)介紹。Cadence 公司旗下有兩個(gè)產(chǎn)品鏈,一個(gè)是IC產(chǎn)品,一個(gè)是PCB產(chǎn)品。PCB

2012-07-08 22:59:53

、 機(jī)電協(xié)同將電子和機(jī)械協(xié)同設(shè)計(jì)這一傳統(tǒng)挑戰(zhàn)轉(zhuǎn)化為我們的競(jìng)爭(zhēng)優(yōu)勢(shì),在不喪失設(shè)計(jì)意圖的溝通和交流時(shí)間的情況下無(wú)縫地跨領(lǐng)域工作。ECAD 和 MCAD 工具之間的雙向數(shù)據(jù)傳輸可輕松與您的機(jī)械團(tuán)隊(duì)協(xié)作,并共享

2021-04-13 18:10:51

EDA技術(shù)是在電子CAD技術(shù)基礎(chǔ)上發(fā)展起來(lái)的計(jì)算機(jī)軟件系統(tǒng),是指以計(jì)算機(jī)為工作平臺(tái),融合了應(yīng)用電子技術(shù)、計(jì)算機(jī)技術(shù)、信息處理及智能化技術(shù)的 最新成果,進(jìn)行電子產(chǎn)品的自動(dòng)設(shè)計(jì)。利用EDA工具,可以將

2020-06-28 10:49:47

在PCB上加層又不想增加整個(gè)設(shè)計(jì)時(shí)間。Cadence FPGA設(shè)計(jì)平臺(tái)正是為了應(yīng)對(duì)如此挑戰(zhàn)。FPGA設(shè)計(jì)者,硬件設(shè)計(jì)師以及PCB設(shè)計(jì)人員致力于整個(gè)系統(tǒng)FPGA的pin腳分配上達(dá)成一致。在這次研討會(huì)中,你將會(huì)

2012-03-28 11:48:59

16.6中的最新技術(shù),包括:★ PCB設(shè)計(jì)的趨勢(shì)(小型化,設(shè)計(jì)中的IP應(yīng)用,吉比特接口,協(xié)同設(shè)計(jì))★ FPGA-PCB協(xié)同設(shè)計(jì)能力★ 庫(kù)和設(shè)計(jì)數(shù)據(jù)管理問(wèn)題★ 設(shè)計(jì)規(guī)劃和布線新技術(shù)★ 信號(hào)完整性,電源分布

2012-11-08 09:51:32

本文介紹了一種PCB設(shè)計(jì)復(fù)用方法,它是基于Mentor Graphics的印制電路板設(shè)計(jì)工具Board Station進(jìn)行的。

2021-05-06 07:10:13

本帖最后由 eehome 于 2013-1-5 09:47 編輯

前記:在很多電子網(wǎng)站上看到很多介紹IC或者FPGA設(shè)計(jì)工具系統(tǒng)的資料,但是感覺(jué)都不是很綜合。所以這里嘗試做一個(gè)2012

2012-12-28 17:00:22

隨著通信系統(tǒng)中高速板設(shè)計(jì)復(fù)雜性的日益提高,依賴某一種特定的CAD工具已經(jīng)無(wú)法在可接受的精度范圍內(nèi)完成整個(gè)設(shè)計(jì)仿真。PCB設(shè)計(jì)工程師和信號(hào)完整性(SI)設(shè)計(jì)工程師需要采用各種仿真工具。除了價(jià)格、性能

2014-12-12 16:14:49

:00FSP 庫(kù)管理介紹PSpice AA 高級(jí)分析工具的使用第二期:2013年08月13日14:00-16:00Speed2000_同步開關(guān)分析SSOPSpice模型的創(chuàng)建第三期:2013年08月20日

2013-05-28 21:31:14

cadence中文教程:Cadence 是一個(gè)大型的EDA 軟件它幾乎可以完成電子設(shè)計(jì)的方方面面包括ASIC 設(shè)計(jì)FPGA 設(shè)計(jì)和PCB 板設(shè)計(jì)與眾所周知的EDA 軟件Synopsys相比Cadence 的綜合工具略為遜色然

2008-07-12 09:33:38 0

0 Allegro分冊(cè)為《EDA工具手冊(cè)》的第二分冊(cè),Allegro是Cadence的PCB設(shè)計(jì)工具,此分冊(cè)通過(guò)從PCB環(huán)境設(shè)置到生成光繪文件的全套流程的學(xué)習(xí),可以使EDA的新員工能夠獨(dú)立進(jìn)行PCB設(shè)計(jì)。本

2008-08-05 14:23:41 0

0 提供全面的PCB解決方案的設(shè)計(jì)工具– 提供通用的同時(shí)并行設(shè)計(jì)系統(tǒng)– 提供綜合的電路設(shè)計(jì)環(huán)境– 可以輸出各種netlist,供其他工具使用

2009-04-25 16:27:57 0

0 FPGACPLD設(shè)計(jì)工具——Xilinx ISE使用詳解的主要內(nèi)容:第1章 ISE系統(tǒng)簡(jiǎn)介第2章 工程管理器與設(shè)計(jì)輸入工具第3章 ModelSim仿真工具第4章 ISE中集成的綜合工具第5章 約束第6章

2009-07-24 16:06:58 197

197 論述了微機(jī)電系統(tǒng)設(shè)計(jì)工具的發(fā)展概況,并針對(duì)微機(jī)電系統(tǒng)的多樣性對(duì)設(shè)計(jì)工具的需求提出了一種可支持任意流程的微機(jī)電系統(tǒng)設(shè)計(jì)工具架構(gòu)。該架構(gòu)以系統(tǒng)級(jí)行為建模與仿真、器

2009-11-16 13:52:34 24

24 工程師試用,與為昕一起推動(dòng) EDA 軟件國(guó)產(chǎn)化盡一份力!試用得有禮!具體產(chǎn)品介紹如下:產(chǎn) 品 介 紹 為昕 PCB 設(shè)計(jì)工具-Mars 是一款完全自主

2023-03-06 16:32:21

大多數(shù) Cadence 工具使用同樣的庫(kù)模型,庫(kù)結(jié)構(gòu)按目錄結(jié)構(gòu)組織數(shù)據(jù),這利于不同工具之間的數(shù)據(jù)交互和一致操作

2010-11-01 17:01:48 0

0 隨著PCB設(shè)計(jì)復(fù)雜程度的不斷提高,設(shè)計(jì)工程師對(duì) EDA工具在交互性和處理復(fù)雜層次化設(shè)計(jì)功能的要求也越來(lái)越高。Cadence Design Systems, Inc. 作為世界第一的EDA工具供應(yīng)商,在這些方

2010-11-24 15:15:48 0

0 摘 要:在FPGA開發(fā)的各個(gè)階段,市場(chǎng)為我們提供了很多優(yōu)秀的EDA工具。面對(duì)眼花繚亂的EDA工具,如何充分利用各種工具的特點(diǎn),并規(guī)劃好各種工具的協(xié)同使用,對(duì)FPGA

2009-06-20 10:51:14 692

692 FPGA設(shè)計(jì)工具淺談

作為一個(gè)負(fù)責(zé)FPGA企業(yè)市場(chǎng)營(yíng)銷團(tuán)隊(duì)工作的人,我不得不說(shuō),由于在工藝技術(shù)方面的顯著成就以及硅芯片設(shè)計(jì)領(lǐng)

2009-10-10 07:46:04 429

429 OrCAD FPGA系統(tǒng)規(guī)劃

創(chuàng)新的FPGA - PCB協(xié)同設(shè)計(jì)

該Cadence ®的OrCAD ® FPGA系統(tǒng)提供了一個(gè)完整的策劃,為FPGA - PCB協(xié)同設(shè)計(jì),使用戶能夠創(chuàng)建可擴(kuò)展解決方案的

2010-08-30 17:49:26 1748

1748

Cadence是一個(gè)大型的EDA軟件,它幾乎可以完成電子設(shè)計(jì)的方方面面,包括ASIC設(shè)計(jì)、FPGA設(shè)計(jì)和PCB板設(shè)計(jì)。與眾所周知的EDA軟件Synopsys相比,Cadence的綜合工具略為遜色。然而Cadence在仿真電路

2011-05-11 18:26:43 0

0 Cadence OrCAD Capture 具有快捷、通用的設(shè)計(jì)輸入能力,使Cadence OrCAD Capture 線路圖輸入系統(tǒng)成為全球最廣受歡迎的設(shè)計(jì)輸入工具。它針對(duì)設(shè)計(jì)一個(gè)新的模擬電路、修改現(xiàn)有的一個(gè) PCB 的線路圖

2011-05-22 11:50:23 0

0 簡(jiǎn)要闡述了高速PCB設(shè)計(jì)的主要內(nèi)容, 并結(jié)合Cadence軟件介紹其解決方案比較了傳統(tǒng)高速設(shè)計(jì)方法與以Cadence為代表的現(xiàn)代高速PCB設(shè)計(jì)方法的主要差異指出在進(jìn)行高速設(shè)計(jì)過(guò)程中必須借助于

2011-11-21 16:53:58 0

0 完整性高的FPGA-PCB系統(tǒng)化協(xié)同設(shè)計(jì)工具 Cadence OrCAD and Allegro FPGA System Planner便可滿足較復(fù)雜的設(shè)計(jì)及在設(shè)計(jì)初級(jí)產(chǎn)生最佳的I/O引腳規(guī)劃,并可透過(guò)FSP做系統(tǒng)化的設(shè)計(jì)規(guī)劃,同時(shí)整合logic、

2013-04-08 11:07:53 0

0 PCB設(shè)計(jì)工具Protel DXP下載

2015-01-26 11:49:17 68

68 HDL 原理圖設(shè)計(jì)工具、約束管理器、

Allegro PCB 設(shè)計(jì)工具和 SPECCTRA 布線工具的功能和設(shè)計(jì)技巧。在介紹工具和命令的同時(shí),還提供了大量

的范例以及習(xí)題,以方便讀者更好地理

2016-01-20 16:03:56 0

0 收藏的PCB設(shè)計(jì)工具分享出來(lái)

2017-02-15 23:04:23 23

23 TI各種模擬設(shè)計(jì)工具介紹

2017-10-16 12:56:45 7

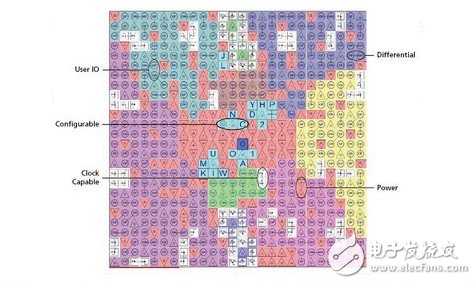

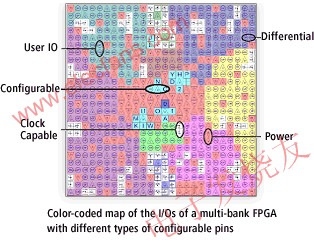

7 FPGA 功能強(qiáng)大且管腳數(shù)目極大,可為工程師提供大量機(jī)會(huì)來(lái)提升特性和功能,同時(shí)還能降低產(chǎn)品成本。隨著復(fù)雜度增加,將這些器件集成到印刷電路板也成為了一項(xiàng)嚴(yán)峻的挑戰(zhàn)。數(shù)百個(gè)邏輯信號(hào)需映射到器件的物理管腳

2017-11-16 15:51:36 735

735 Cadence OrCADFPGA System Planner為FPGA和PCB之間的協(xié)同設(shè)計(jì)提供了一種全面的、可擴(kuò)展的解決方案,它能使用戶創(chuàng)建一個(gè)正確的、最優(yōu)的引腳分配。FPGA的引腳分配是根據(jù)

2017-11-17 20:36:09 5453

5453

Cadence 是一個(gè)大型的EDA 軟件,它幾乎可以完成電子設(shè)計(jì)的方方面面,包括ASIC 設(shè)計(jì)、FPGA 設(shè)計(jì)和PCB 板設(shè)計(jì)。Cadence 在仿真、電路圖設(shè)計(jì)、自動(dòng)布局布線、版圖設(shè)計(jì)及驗(yàn)證等方面有著絕對(duì)的優(yōu)勢(shì)。Cadence 包含的工具較多幾乎包括了EDA 設(shè)計(jì)的方方面面。

2018-02-07 13:44:36 18492

18492 Cadence 是一個(gè)大型的EDA 軟件,它幾乎可以完成電子設(shè)計(jì)的方方面面,包括ASIC 設(shè)計(jì)、FPGA 設(shè)計(jì)和PCB 板設(shè)計(jì)。Cadence 在仿真、電路圖設(shè)計(jì)、自動(dòng)布局布線、版圖設(shè)計(jì)及驗(yàn)證等方面

2018-02-07 17:11:21 26525

26525

在摩爾定律的作用下,FPGA產(chǎn)品的門數(shù)量不斷增加,性能與專門功能逐漸加強(qiáng),使得FPGA在電子系統(tǒng)領(lǐng)域能夠取代此前只有ASIC和ASSP才能發(fā)揮的作用。不過(guò),說(shuō)到底,FPGA必須要有適當(dāng)?shù)脑O(shè)計(jì)工具輔助,讓設(shè)計(jì)人員充分發(fā)揮其作用,否則再好的產(chǎn)品也毫無(wú)意義。

2018-05-19 10:26:00 1186

1186 TI WEBENCH 的設(shè)計(jì)工具們:時(shí)鐘架構(gòu)工具、有源濾波器設(shè)計(jì)工具、電源設(shè)計(jì)工具、LDC設(shè)計(jì)工具、發(fā)光二極管(LED)設(shè)計(jì)工具、傳感器設(shè)計(jì)工具! TI WEBENCH 設(shè)計(jì)工具,讓設(shè)計(jì)輕松一點(diǎn)~

2018-06-13 05:25:00 5523

5523 電源系統(tǒng)設(shè)計(jì)工具

2018-08-13 00:01:00 4921

4921 電源系統(tǒng)設(shè)計(jì)工具

2018-08-06 01:13:00 3978

3978 美高森美公司(Microsemi Corporation)宣布推出最新11.7版本Libero系統(tǒng)級(jí)芯片(SoC),這是用于美高森美現(xiàn)場(chǎng)可編程邏輯器件(FPGA)產(chǎn)品的全面FPGA設(shè)計(jì)工具套件

2018-08-08 14:28:00 1388

1388 Cadence軟件是我們公司統(tǒng)一使用的原理圖設(shè)計(jì)、PCB設(shè)計(jì)、高速仿真、自動(dòng)布線的EDA工具。本篇Cadence使用手冊(cè)是一本基于Allegro SPB V15.2版本的Cadence軟件

2018-09-21 08:00:00 0

0 時(shí)間 美高森美公司(Microsemi) 宣布SmartFusion 2 SoC FPGA用戶現(xiàn)在可以獲益于其新近發(fā)布的系統(tǒng)創(chuàng)建器(System Builder)設(shè)計(jì)工具。System Builder

2018-09-25 09:07:01 513

513 EE-Sim系統(tǒng)電源設(shè)計(jì)工具介紹及實(shí)戰(zhàn)講解。

2020-05-30 11:07:00 1745

1745

的物理管腳輸出,同時(shí)還需保持設(shè)計(jì)的電氣完整性。FPGA 復(fù)雜度增加也需要高級(jí)合成技術(shù),如此才能更快達(dá)到時(shí)序收斂,最大程度地減少設(shè)計(jì)變更的影響以及解決特定應(yīng)用要求。 通過(guò)使用可選的 FPGA-PCB 優(yōu)化技術(shù),即將 HDL 合成和先進(jìn)的 FPGA-PC

2018-10-26 11:54:01 233

233 世界三大EDA廠商一般指的是Cadence, Synopsys, Mentor Graphics,四強(qiáng)的話好包括Springsoft。就我個(gè)人的理解,Synopsys主要是強(qiáng)在前端,DC和PT是公認(rèn)的標(biāo)準(zhǔn)。Cadence牛在后端,無(wú)論是RF, 數(shù)字,亦或是PCB級(jí),它的后端布線工具都用的挺廣的。

2018-11-18 09:06:25 5517

5517 本文章主要詳細(xì)介紹了pcb版圖設(shè)計(jì)工具,分別有FreePCB、MentorPADS、MentorWG2005。

2019-04-24 17:47:05 2082

2082 更好地了解哪種功能很重要在PCB設(shè)計(jì)工具中,讓我告訴你我發(fā)現(xiàn)的最有用的東西。我正在使用AltiumDesigner?版本18,這是一個(gè)完整的PCB設(shè)計(jì)平臺(tái)解決方案,可以將您的設(shè)計(jì)從原理圖捕獲一直到PCB布局。

2019-07-23 09:56:07 6476

6476 隨著多設(shè)計(jì)級(jí)集成,PCB設(shè)計(jì)工具供應(yīng)商還需要投入更多精力進(jìn)行電路板測(cè)試。

2019-08-14 08:55:00 1533

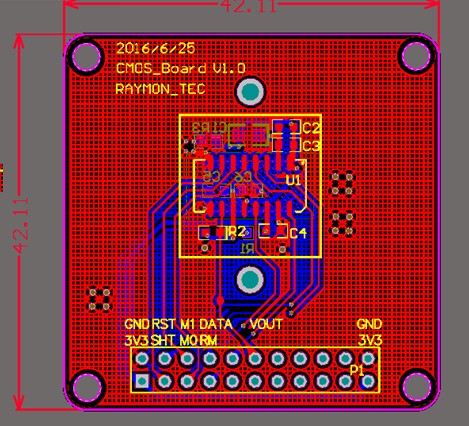

1533 區(qū)別于altium的一庫(kù)走天下,cadence的PCB套件流程中,PCB封裝的制作需要單獨(dú)制作pad,然后繪制封裝。這兩步的工具分別為Padstack和PCB Editor

2019-11-02 09:32:55 9632

9632

Cadence工具包含IC設(shè)計(jì)組件和PCB設(shè)計(jì)組件,從現(xiàn)在開始學(xué)習(xí)PCB設(shè)計(jì)組件,并對(duì)比曾經(jīng)的Altium(Protel)

2019-11-02 09:01:00 2788

2788

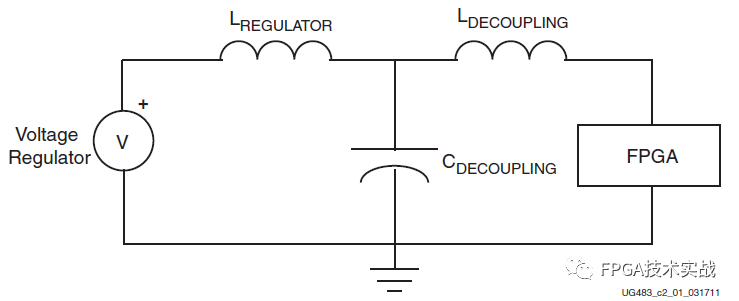

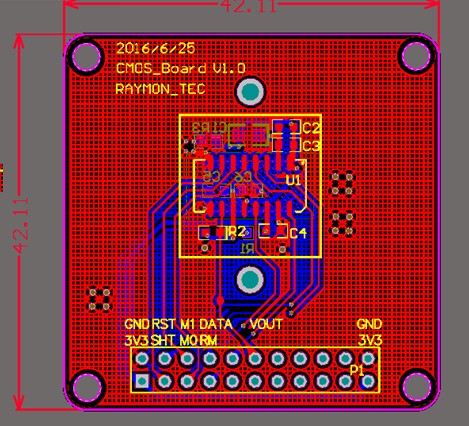

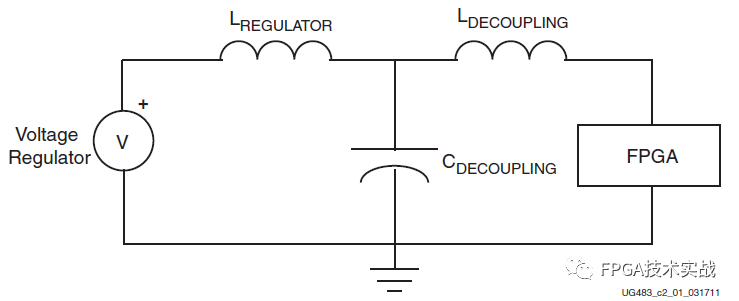

引言:我們繼續(xù)介紹FPGA PCB設(shè)計(jì)相關(guān)知識(shí),本章介紹7系列FPGA的配電系統(tǒng)(PDS),包括去耦電容器的選擇、放置和PCB幾何結(jié)構(gòu),并為每個(gè)7系列FPGA提供了一種簡(jiǎn)單的去耦方法。另外,還介紹

2021-03-12 14:42:45 3505

3505

新一代Sigrity可以與Clarity 3D Solver場(chǎng)求解器同步運(yùn)行,并與Cadence Allegro? PCB Designer設(shè)計(jì)工具和Allegro Package Designer Plus封裝設(shè)計(jì)工具緊密集成。

2021-03-17 11:33:48 1922

1922 EDA工具CADENCE原理圖與PCB設(shè)計(jì)說(shuō)明

2021-07-15 09:38:12 50

50 什么優(yōu)勢(shì)? ? 這里就簡(jiǎn)單分享一下相關(guān)的內(nèi)容。 ? 01 ? 介紹 ? AD、PADS、Cadence三大工具是什么? ? 硬件開發(fā)工具,主要是“畫原理圖”+“畫PCB圖” ? AD: Altium

2023-05-11 10:17:00 4169

4169

,2023 年 6 月 30 日——楷登電子(美國(guó)? Cadence ?公司,NASDAQ:CDNS)近日宣布,基于 AI 的 Cadence?Virtuoso?Studio 設(shè)計(jì)工具和解決方案已獲得 Samsung Foundry 認(rèn)證。 雙方的共同客戶可以放心利用 Virtuoso Studio 和

2023-06-30 10:08:30 681

681 如今,FPGA 功能強(qiáng)大且管腳數(shù)目極大,可為工程師提供大量機(jī)會(huì)來(lái)提升特性和功能,同時(shí)還能降低產(chǎn)品成本。隨著復(fù)雜度增加,將這些器件集成到印刷電路板也成為了一項(xiàng)嚴(yán)峻的挑戰(zhàn)。數(shù)百個(gè)邏輯信號(hào)需映射到器件

2023-09-21 09:11:40 407

407

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論