隨著物聯(lián)網(wǎng) (IoT) 逐漸需要執(zhí)行更為復(fù)雜的任務(wù),物聯(lián)網(wǎng)端點的存儲器需求隨之增加,尤其是執(zhí)行高級邊緣計算的端點。不過,片上微控制器閃存的上限約為 1 兆位 (Mbit),而許多高端物聯(lián)網(wǎng)端點的存儲器需求通常是其數(shù)倍之多。

傳統(tǒng)的解決方案是利用外部閃存芯片擴展微控制器的程序存儲器,但是存儲器要求高達 8 Mbit 或更大時,往往就必須使用片外存儲器。

因此,在許多情況下,設(shè)計人員最好干脆忽略片上閃存,而使用無閃存微處理器(即無 ROM 微控制器),搭配外部高速八線 SPI 芯片內(nèi)執(zhí)行 (XiP) 閃存芯片,從而顯著降低微控制器成本,同時加強可擴展性以提高設(shè)計保障。由于增加了高速八線存儲器接口,因而無需再擔(dān)心存儲器訪問時間。

本文介紹了無 ROM 微控制器和外部存儲器,探討了在需要大容量程序存儲器的物聯(lián)網(wǎng)端點和嵌入式系統(tǒng)中如何使其成為可行選擇。此外,本文還以 NXP Semiconductors 的無 ROM 微控制器和 Adesto Technologies 的八線 SPI XiP 閃存芯片為例,介紹了如何應(yīng)用這一概念。

物聯(lián)網(wǎng)邊緣端點的存儲器擴展

中低性能的物聯(lián)網(wǎng)端點大多使用微控制器來管理端點,固件存儲在片上閃存中。由于增加了額外的應(yīng)用代碼、無線 IP 通信堆棧和增強安全代碼,因而固件也需擴展。代碼擴展可以在開發(fā)階段進行,也可在現(xiàn)場更新時實現(xiàn)。

如今,部分物聯(lián)網(wǎng)端點需要執(zhí)行更多計算功能。這些物聯(lián)網(wǎng)端點需要執(zhí)行傳感器融合算法、數(shù)據(jù)插值、模式或圖像識別,以及日益復(fù)雜的人工智能 (AI) 計算等復(fù)雜任務(wù),而非只是通過網(wǎng)絡(luò)將原始或部分處理的傳感器數(shù)據(jù)傳輸至中央計算機進行處理。

因此,中央計算機僅僅只接收物聯(lián)網(wǎng)節(jié)點的本地處理結(jié)果,而非原始傳感器數(shù)據(jù)的所有字節(jié),從而減少無線網(wǎng)絡(luò)流量。射頻發(fā)射器可能是物聯(lián)網(wǎng)端點中功耗最大的組件,因此邊緣計算往往可以延長電池供電端點的電池續(xù)航時間。

除此之外,需要現(xiàn)場更新的系統(tǒng)還面臨其他存儲器挑戰(zhàn)。常規(guī)系統(tǒng)的存儲器需求至少是預(yù)估程序存儲空間的兩倍,以便處理現(xiàn)場更新。這樣既能包含現(xiàn)有的程序存儲器,又可處理所有無線 (OTA) 更新。某些系統(tǒng)可能需要預(yù)估程序存儲空間的三倍,剩余的存儲器分配給只讀出廠固件鏡像。若檢測到黑客攻擊或出現(xiàn)固件鏡像損壞等特定類型的系統(tǒng)故障,系統(tǒng)則可以加載出廠固件鏡像以恢復(fù)系統(tǒng)。

對于某些應(yīng)用,存儲器擴展很快就會超過 1 Mbit 的嵌入式閃存上限,因而必須擴展外部存儲器。過去采用的解決方案是添加外部并行閃存芯片。不過,這一方案的缺陷是會占用微控制器約 36 個外部引腳,否則這些引腳就可用于應(yīng)用 I/O。此外,這也浪費了印刷電路板空間,增加了電路板電磁干擾 (EMI) 的可能性。

SPI 程序存儲器擴展

除了使用并行總線外,還可使用串行外設(shè)接口 (SPI) 擴展程序存儲器。傳統(tǒng) SPI 只用一條數(shù)據(jù)線路進行半雙工單比特傳輸,但是近年來,該接口已發(fā)展為支持兩條和四條數(shù)據(jù)線路,從而使數(shù)據(jù)吞吐量相應(yīng)增加,最終使得連接大容量外部 SPI 閃存芯片成為可行之舉。

對于程序存儲器應(yīng)用,傳統(tǒng)的雙線或四線 SPI 使用陰影閃存配置,將外部數(shù)據(jù)閃存復(fù)制到嵌入式靜態(tài)隨機存取存儲器 (SRAM),再映射至程序存儲空間。這樣既能輕松擴展程序存儲器,又可由高速 SRAM 運行以提高執(zhí)行速度。雖頗具優(yōu)勢,卻也不乏缺點。由于閃存將根據(jù)需要復(fù)制到內(nèi)部 SRAM,而內(nèi)部 SRAM 容量有限,因此存儲器需以分頁模式訪問。盡管增加片上 SRAM 能克服這一瓶頸,但對于任何半導(dǎo)體而言,SRAM 都是最昂貴的模塊之一,因而此舉的缺點在于會顯著增加微控制器成本。

近來,SPI 已經(jīng)演變成 XiP。SPI XiP 允許微控制器 CPU 直接通過外部 SPI 閃存執(zhí)行固件代碼。在 SPI XiP 接口添加緩存可大幅提高程序執(zhí)行速度。

最近,SPI XiP 的廣泛應(yīng)用促使演化出支持八條數(shù)據(jù)線路的接口。這種八線 SPI XiP 接口的吞吐量顯著提高,運行速度遠(yuǎn)高于片上閃存,高達 100 Mbit/s 以上。

SPI 存儲器革命

這引發(fā)了一場倒退 30 年的不尋常演變。試想一下,某系統(tǒng)具有 1 Mbit 的片上閃存,以及可由八線 SPI XiP 接口訪問的 32 Mbit 外部程序閃存。容量如此小的片上程序存儲器引出了一個問題:若移除片上微控制器閃存,仍算是高性價比的系統(tǒng)嗎?

一直以來,人們普遍認(rèn)為相較于具有外部閃存芯片的無閃存微控制器,使用閃存微控制器的中等性能系統(tǒng)性價比更高。直到近年,這一觀念才有所轉(zhuǎn)變。

如果移除片上閃存,自然會降低微控制器成本。經(jīng)深入研究調(diào)查表明,若不再需要片上閃存,則僅用于閃存的工藝技術(shù)特性也可舍棄,從而降低制造工藝成本,進一步降低微控制器成本。于是,大約 30 年前推出的“無 ROM”微控制器又重現(xiàn)于世。現(xiàn)如今,我們稱之為無閃存微控制器。

(重新)引入無閃存微控制器

NXP Semiconductors 的 MIMXRT1052DVL6B (RT1052) 是一款能夠充分利用閃存速度的高性能無閃存微控制器。RT1052 是 NXP 的 i.MX RT1050 處理器系列產(chǎn)品之一,基于 600 MHz 的 Arm? Cortex?-M7,具有 32 KB 的指令緩存和 32 KB 的數(shù)據(jù)緩存。這款微控制器移除了閃存,采用高速 CMOS 工藝技術(shù)不受內(nèi)部閃存限制,從而實現(xiàn) 600 MHz 的時鐘速度。RT1052 具有高達 512 KB 的大容量 SRAM,可分區(qū)作為程序或數(shù)據(jù)存儲器使用。

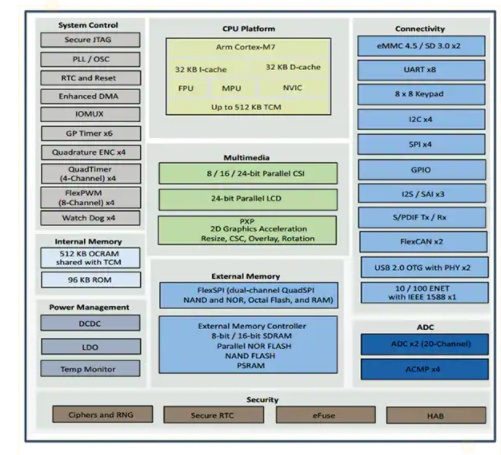

該微控制器具有各種高端外設(shè),包括 LCD 接口、支持高端相機的數(shù)碼相機傳感器接口 (CSI) 和像素處理流水線 (PXP)、用于數(shù)字音頻的 SPDIF 接口、兩個 USB OTG 接口、兩個 eMMC/SD 閃存卡接口、兩個 20 通道模數(shù)轉(zhuǎn)換器 (ADC) 和一個加密模塊。完整的外設(shè)列表如框圖所示(圖 1)。

圖 1:NXP 的 RT1052 具有各種高端外設(shè),包括 SPI XiP 串行接口并支持?jǐn)?shù)據(jù)加密。(圖片來源:NXP)

另一個選擇是 NXP 的 MIMXRT1051DVL6B (RT1051)。這款微控制器的功能與 RT1052 完全相同,但不具備 LCD 接口、CSI 和 PXP。

RT1052 具有 FlexSPI 接口,可使用雙線、四線或八線 SPI XiP 閃存接口執(zhí)行代碼。為了增加固件的安全性,該微控制器支持通過 SPI XiP 連接加密程序存儲器,Adesto Technologies 的 ATXP032-CCUE-T 就是一個典型的加密存儲器實例。

新型 XiP 閃存操作

Adesto 的 ATXP032-CCUE-T 是一款 32 Mbit 八通道閃存芯片,八條數(shù)據(jù)線路支持雙通道傳輸速率 (DTR) 模式下數(shù)據(jù)傳輸高達 266 MB/s,遠(yuǎn)高于片上微控制器閃存。該閃存由 1.8 V 單電源供電,典型八線模式待機電流為 35 μA,支持的最高 SPI 時鐘速度為 133 MHz。

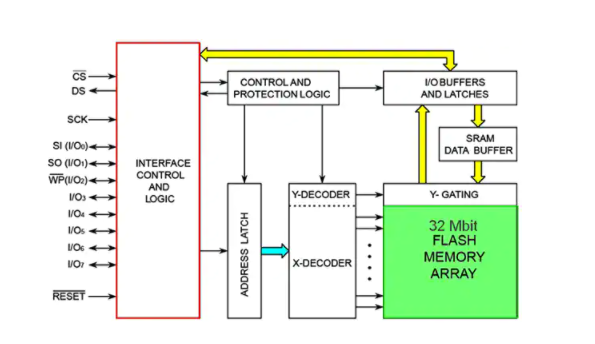

圖 2:Adesto 的 ATXP032-CCUE-T 閃存使用八線 SPI(I/O0 至 I/O7)與微控制器連接。SRAM 寫數(shù)據(jù)緩沖區(qū)可提高寫入閃存操作的性能。(圖片來源:Adesto Technologies)

在有效讀取閃存期間,ATXP32 電流消耗為 142 μA/MHz,外加 1 mA 電流開銷(典型值)。八線模式下,最高 SPI 時鐘速度為 133 MHz,電流消耗僅為 19.9 mA。

此外,ATXP032-CCUE-T 還支持標(biāo)準(zhǔn) SPI 模式 0 和 3,以及四線 SPI 模式。256 字節(jié)的安全寄存器包含 128 字節(jié)出廠設(shè)置的唯一標(biāo)識符,以及 128 字節(jié)的一次性可編程 (OTP) 存儲器,后者可用于存儲以太網(wǎng)介質(zhì)訪問控制 (MAC) 地址或安全密鑰等設(shè)備信息。

ATXP032-CCUE-T 的存儲器布局值得注意,共分為四個存儲體,單個容量為 8 Mbit。內(nèi)部邏輯已預(yù)先配置,因此主機微控制器可在某個存儲體中執(zhí)行代碼,而在另一個存儲體中編程或擦除。這項操作對主機微控制器是透明的,無需特殊配置設(shè)置。

此外,ATXP032-CCUE-T 還有三個狀態(tài)和控制寄存器,可用于配置低功耗模式等器件工作參數(shù),啟用或禁止 DTR 模式,以及設(shè)置標(biāo)準(zhǔn)、四線或八線 SPI 模式(默認(rèn)為標(biāo)準(zhǔn) SPI)。通過讀取狀態(tài)寄存器,可以指示編程或擦除操作狀態(tài)、低功耗狀態(tài),以及是否有任何存儲器設(shè)置為寫保護。

將無閃存微控制器與外部 XiP 連接在一起

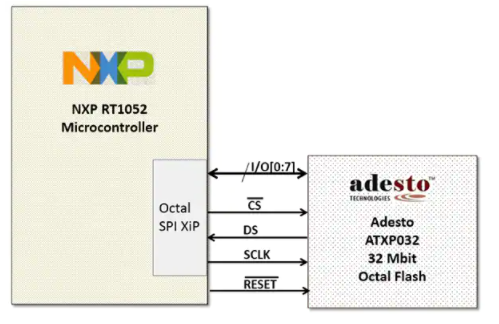

將 RT1052 與 ATXP032-CCUE-T 連接在一起相當(dāng)簡單(圖 3)。上電后,RT1052 開始在 96 KB 的片上引導(dǎo) ROM 中執(zhí)行代碼。引導(dǎo) ROM 讀取 14 個引導(dǎo)模式配置引腳的狀態(tài),這些引腳可用于選擇 RT1052 多個外部存儲器接口之一以連接程序存儲器。可選接口包括外部 eMMC 卡、micro SD 卡、常規(guī)外部并行接口和 SPI XiP(本例中使用 Adesto 的 ATXP032-CCUE-T)。

圖 3:NXP RT1052 無閃存微控制器具有八線 SPI XiP 接口,可輕松連接 Adesto ATXP032-CCUE-T。八線 SPI XiP 接口的操作對 Arm 內(nèi)核是透明的。(圖片來源:Digi-Key Electronics)

RT1052 引導(dǎo)選項還包括從 USB OTG 或 UART 下載代碼并由 SRAM 執(zhí)行。此外,在制造過程中,也可通過熔斷 RT1052 的內(nèi)部保險絲來設(shè)置引導(dǎo)模式選項,而非使用引導(dǎo)模式配置引腳。只要 RT1052 的引導(dǎo) ROM 啟用八線 SPI XiP 接口用于程序存儲器執(zhí)行,程序就會立即執(zhí)行。接著,Arm 內(nèi)核會從 Adesto ATXP032-CCUE-T 執(zhí)行固件,其方式與從外部并行閃存設(shè)備或內(nèi)部閃存相同。

由于涉及高速數(shù)據(jù)傳輸,八通道串行閃存應(yīng)放置在印刷電路板上盡可能靠近微控制器八線 SPI XiP 端口的地方。為了減少干擾,印制線長度不應(yīng)超過 120 mm。與時鐘信號的距離應(yīng)至少是印刷電路板印制線寬度的三倍,并且遠(yuǎn)離其他信號以避免干擾。I/O[0:7] 雙向數(shù)據(jù)信號間距應(yīng)保持在 10 mm 以內(nèi),以避免偏移。

總結(jié)

鑒于對邊緣計算、OTA 更新及相關(guān)存儲器擴展性的需求,物聯(lián)網(wǎng)端點的存儲器需求隨之增加。在某些情況下,設(shè)計人員可能會發(fā)現(xiàn)在這些端點設(shè)備中使用無閃存微控制器是不錯的選擇。

如上所述,無閃存微控制器、高速接口和八線 SPI XiP 閃存芯片的進步,為開發(fā)人員提供了構(gòu)建高性能、高性價比的物聯(lián)網(wǎng)端點或嵌入式系統(tǒng)的新選項,從而替代傳統(tǒng)基于閃存的微控制器方法。

電子發(fā)燒友App

電子發(fā)燒友App

評論