全球存儲器產業已進入一個必須尋求新興替代技術的時代。在多樣化的次世代存儲器技術中,為何電阻式存儲器,在類神經仿生運算的應用上值得期待?其更被業界認為是最有機會成為下一代通用存儲器的選擇,同時也是目前投入研發廠商最多之技術?本篇將帶您一探究竟。

本文是閎康科技特別邀請在電阻式內存研究領域頂尖學者 王永和教授撰文介紹此新興內存組件的發展概況與技術趨勢,與讀者分享此一重要科技領域的學術研究進展。

邁入尋求全新嵌入式非揮發性存儲器技術的時代

全球內存產業已進入一個必須尋求新興替代技術的時代了。近年來由于物聯網、移動裝置、高速計算機和智能汽車等產業的快速發展,大幅推升了人工智能 (AI) 及邊緣計算 (Edge Computing) 等巨量運算架構的應用需求,也因此既有高容量存儲組件例如 DRAM 及 NAND Flash,其在耗電量及數據訪問速度上已無法跟上需求的腳步。并且,隨著半導體工藝線寬縮微已超越 14nm、晶體管發展主流遷移到 FinFET 或 GAA 等先進結構,長期應用于 CMOS 芯片上存儲的嵌入式 NOR Flash 礙于「閃存縮放限制 (Flash Memory Scaling Limit)」問題,也已無法跟上 SoC 芯片整合工藝的發展要求,必須要有全新的嵌入式非揮發性內存技術,才能搭配下一世代以先進工藝所制造的 ASIC 和 MCU。?

電阻式存儲器為何備受期待?

過去數十年來在世界各國合力開發下,已初略成形的次世代非揮發性內存技術包括鐵電內存 (FRAM)、相變化內存 (PRAM)、磁阻式內存 (MRAM)、以及電阻式內存 (RRAM) 等。這些候選的新興技術,不僅讀寫速度都比 NAND Flash 要快 1,000 倍以上,并且皆能夠在納安培 (nA) 的極低電流下操作。同時,也都具有潛力可突破 von Neumann 架構瓶頸,實現內存內運算 (In-memory Computing) 之能力。?

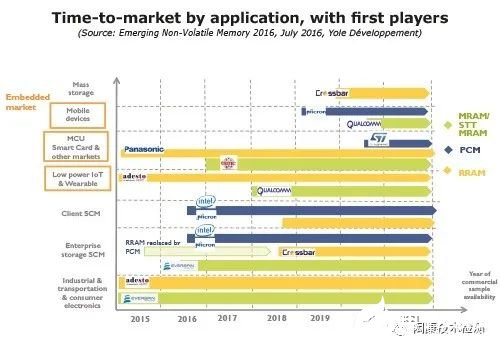

在多樣化的次世代內存技術中,電阻式內存由于相對具有讀寫快速、低耗能、結構簡單、數據儲存時間長、重復操作可靠度佳與成本便宜等產品優勢,以及適合應用于類神經仿生運算的電導 (電阻) 漸變模擬特性,被業界認為是最有機會成為下世代通用內存的選擇,同時也是目前投入研發廠商最多之技術,包含 Adesto (2020年已被Dialog并購)、Crossbar、Samsung、Panasonic、Micron、Hynix 及 Intel 等公司,都各別擁有不同的電阻式內存技術。盡管電阻式內存應用潛力巨大,但至今大多數仍然處于開發階段,至目前為止有對外供貨的公司僅 Crossbar、Panasonic 與 Adesto 三家而已。甚至該技術在其電阻變化的物理機制研究與最佳材料選定上,至今也仍未有定論。然而,業界普遍認為,隨著人工智能應用的疾速發展、市場需求商機涌現,必然將帶動電阻式內存在未來 3 至 4 年內迎來快速成長。產官學界都應及早進行策略布局、掌握此新興內存的產業契機,創造下一個半導體奇跡。

電阻式內存由來

電阻式內存 (Resistive Random Access Memory, RRAM) 結構為簡單的金屬-絕緣層-金屬 (Metal-Insulator-Metal, MIM),其原理為施予電壓或電流操作,利用物質電阻改變組件的高低電阻狀態,達成數字訊號儲存效果。

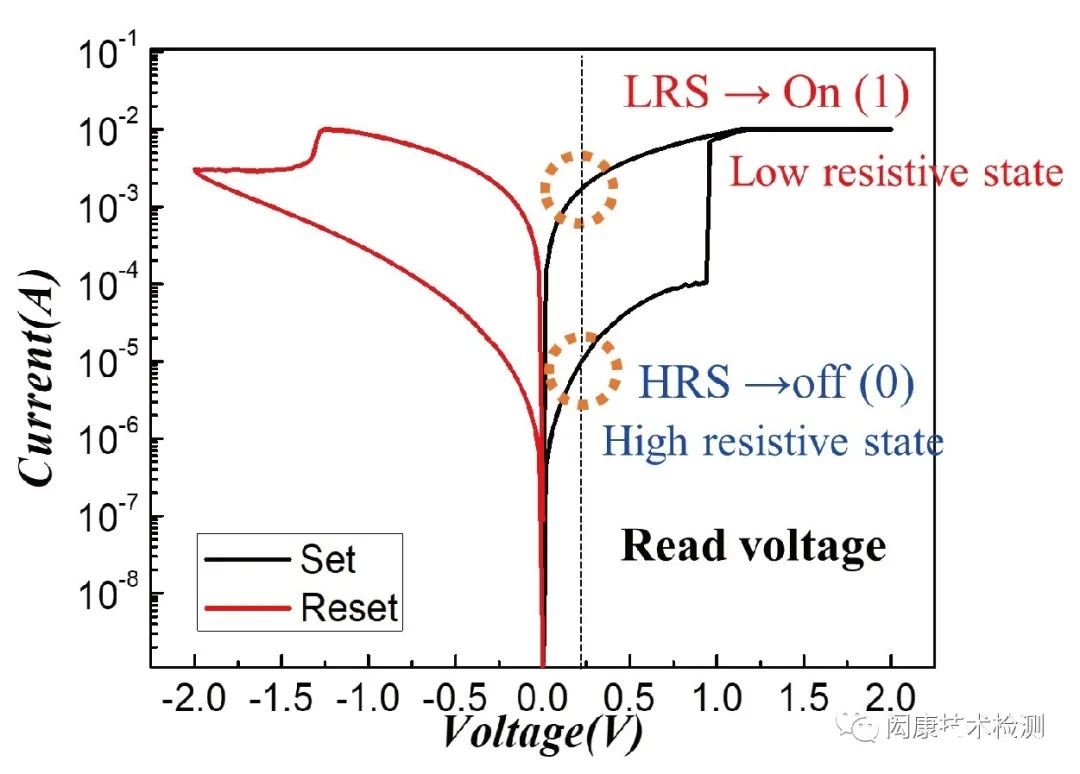

電阻式內存最早起源自 1960 年代,研究學者 Hickmott 發現氧化鋁 (AlOx)?材料經過電壓或電流操作后,其電阻狀態會因此改變[1];近年來,研究發現氧化鎳 (NiO)[2-5]、氧化鈦 (TiOx)[6-9]、氧化鉿 (HfOx)[10-13]等絕緣體材料,亦可用于 RRAM 的中間絕緣層。RRAM 可利用特定的電壓來讀取不同狀態的電阻值 (電流值),進而判讀組件 ”1” 和 ”0” 的邏輯狀態。此外,RRAM 具有良好的非揮發性記憶特性,其訊號儲存狀態可在不施加外在偏壓的情況下,保存至下一次訊號的寫入或抹除。?

RRAM 物理機制與操作特性

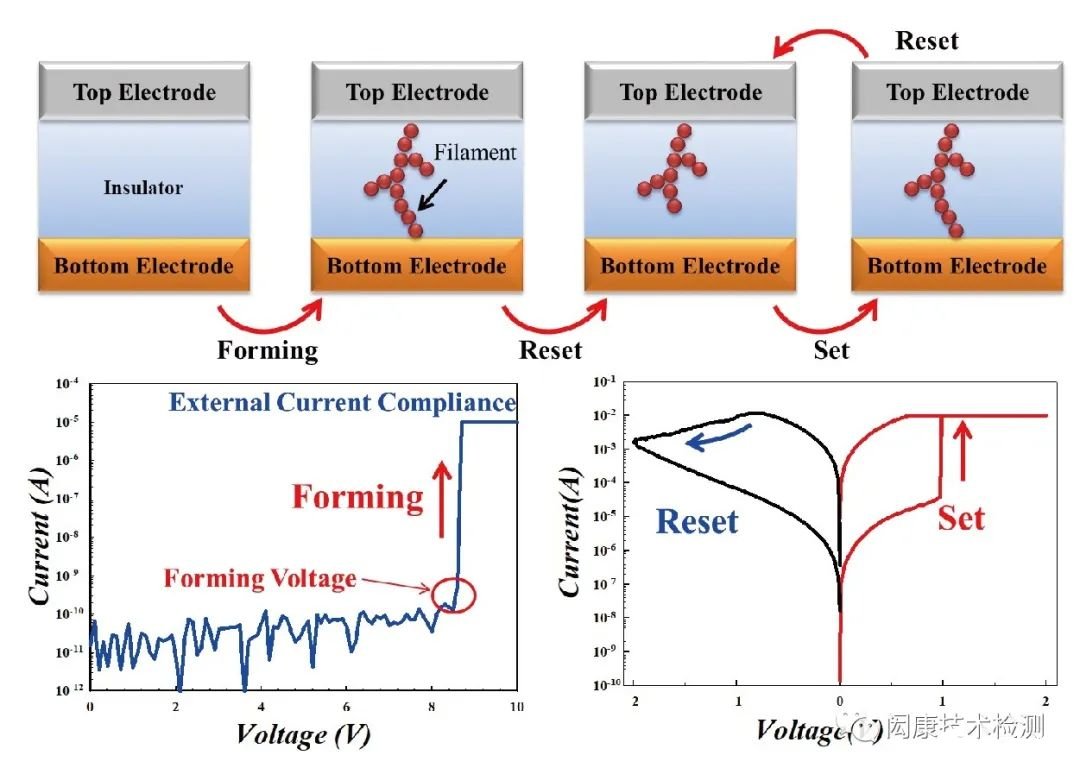

RRAM 的物理機制目前較受到注目的是燈絲理論 (Filament Theory)[14-16],普遍認為 RRAM 的操作方式是在一開始時給予組件一較大的外加偏壓,使氧化物絕緣層內部形成導通路徑,此時絕緣層會變為低阻態 (Low Resistance State, LRS),此過程通常需要限制電流 (Compliance Current),避免電流過大反應劇烈使組件永久崩潰,此步驟稱之為 Forming。接著以組件偏壓控制氧離子與氧空穴復合,使導通路徑阻斷,進而從低電阻態 (LRS) 回到高電阻態 (High Resistance State, HRS),此過程稱為 Reset;而再次給予小于 Forming 所需的電壓,即可將阻斷的導通路徑重新連接,從高阻態 (HRS) 再次回到低阻態 (LRS),此步驟稱為 Set。?

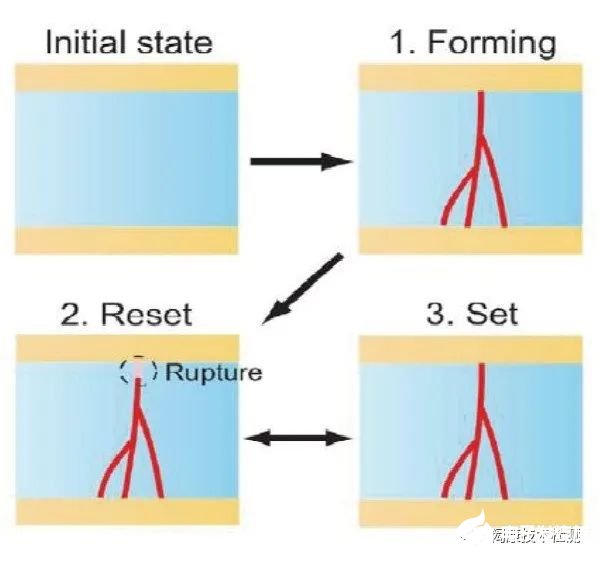

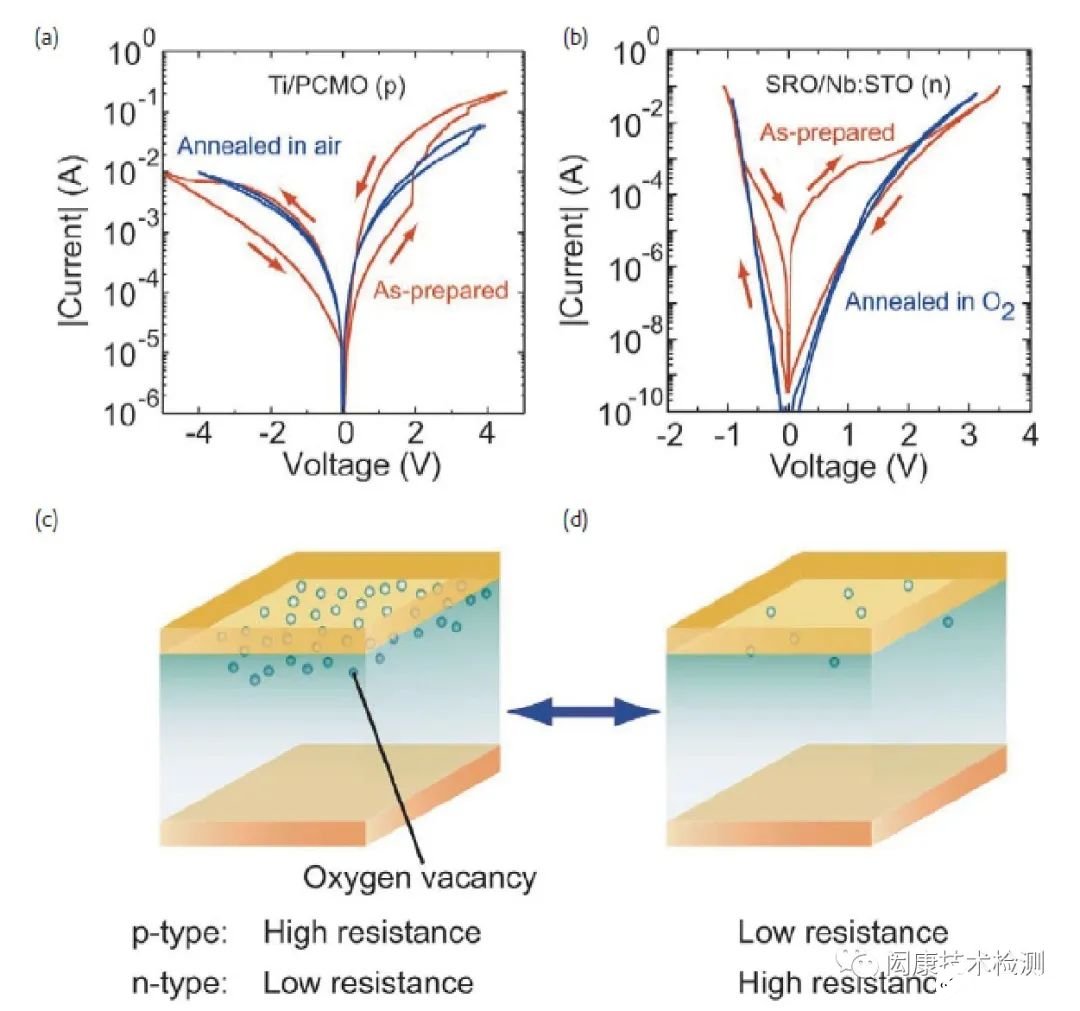

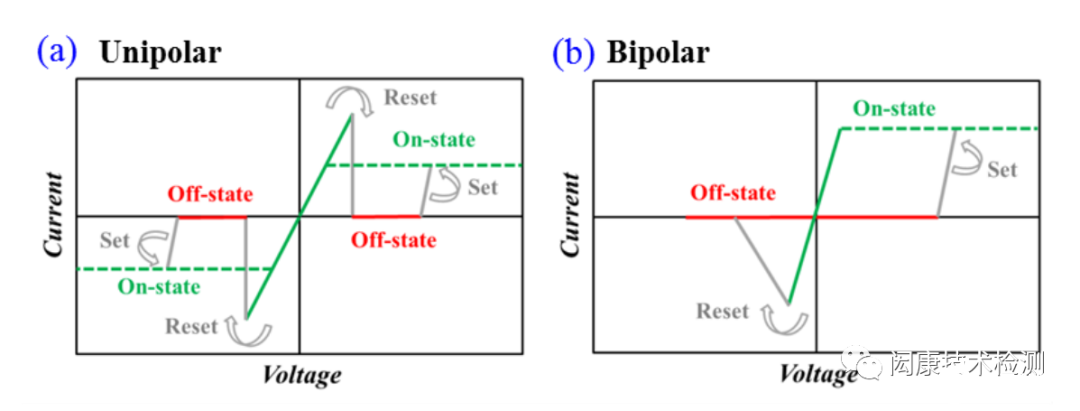

來回操作 Set 與 Reset process 就可以達成 RRAM 的寫入與抹除,RRAM 的操作流程如圖一所示,而在讀取方面主要是藉由一微小的讀取電壓來判讀不同的電阻值,以分辨數字訊號 0 和 1(圖二)。RRAM 依阻值狀態變化的不同可區分為阻絲型與界面型,阻絲型 RRAM 即于上下兩電極間有一連續傳導路徑(圖三),也是目前 RRAM 在傳導機制中較受到廣泛認同的類型;另一為界面型 RRAM (圖四),透過施加外部電壓,使絕緣體層中形成氧空穴或載流子電荷進行電子傳遞使其阻態改變,當氧空穴或載流子電荷變多,其電流增大,因此組件電極間的絕緣體層面積大小會影響阻態變化。

圖一 RRAM 切換流程與電性輸出圖

圖二 RRAM 用于數字內存判讀方式

圖三 燈絲型 RRAM 操作過程[14]

圖四 界面型 RRAM 輸出特性曲線與操作原理[14]

RRAM 操作方式分為兩種特性:

單極性?(Unipolar):如圖五(a)所示,此種可藉由單一方向的電壓即可作 Set 與 Reset 操作,Reset 過程以焦耳熱 (Joule Heating) 造成電阻燈絲熔斷使得阻態變化。

雙極性?(Bipolar):指的操作電壓需相反才能進行 Set 與 Reset,而阻態能切換的原因則主要認為來自于氧離子移動,對電阻燈絲進行氧化還原作用,使其有高低阻態變化,如圖五(b)所示。

圖五 RRAM 操作方式?(a)單極性操作?(Unipolar)、(b)雙極性操作 (Bipolar)[17]

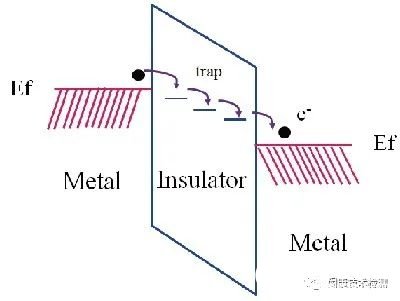

理想的金屬 / 絕緣體 / 金屬結構中,中間的絕緣層在施加偏壓時并不會有電流通過,但實際上當組件受到過大電場或溫度時,載流子能在絕緣層中移動傳導,而有漏電流的產生,進而讀出 HRS。其中電流的移動機制可利用電流-電壓進行電流機制擬合 (Current-Fitting) 評估在絕緣層間電流主要透過何種機制進行移動,其傳輸機制主要可分為以下幾種:

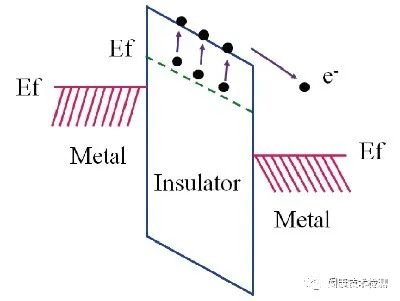

1.歐姆傳導機制?(Ohmic Conduction):

主要以位于導帶 (Conduction Band) 的自由電子 (Free Electron) 與價帶 (Valence Band) 的空穴當作載流子傳輸的機制,在一小電壓下電阻為常數,與電流呈線性關系。圖六為 RRAM 結構的歐姆傳導能帶示意圖,材料中的載流子受到外加電場的作用移動,進而產生電流[18]。

圖六 歐姆傳導之能帶圖

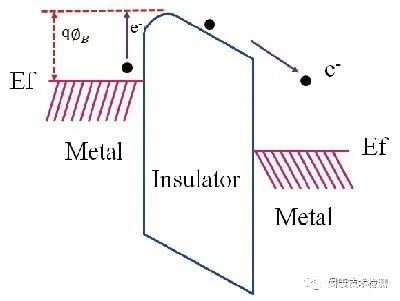

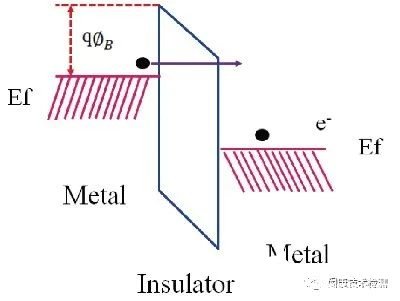

2.肖特基發射?(Schottky Emission):

一般金屬與絕緣體的結面會存在著勢壘高度 (Barrier Height),此勢壘高度指的是絕緣體電子親和力與金屬功函數之間差值。圖七所示為一 RRAM 之能帶圖,施加外加電場情形下與電子通過金屬表面時產生的鏡像電荷,使勢壘高度下降,電子透過熱激發影響越過勢壘高度,電子能在絕緣體的傳導帶上傳遞,而產生電流稱為肖特基發射 (Schottky Emission)[19]。

圖七 肖特基發射之能帶圖

3.法蘭克-普爾發射 (Frenkel- Poole Emission):

此傳導機制與肖特基發射類似,同樣受到外加電場影響,電子因熱激發獲得能量,且載流子跳至價帶或導帶的勢壘高度降低,使載子能越過能障高度跳至價電帶或導電帶,進而由導帶傳遞產生電流。

此時的勢壘高度指的是在沉積絕緣體或半導體薄膜時,薄膜所產生的懸浮鍵或是缺陷,這些缺陷會在靠近價電帶或導電帶的邊緣形成缺陷能級,而缺陷能級到價帶或導帶之間的差值,即為法蘭克-普爾發射 (Frenkel-Poole Emission) 所需越過之勢壘高度[20],如圖八所示其能帶圖。

圖八 法蘭克-普爾發射之能帶圖

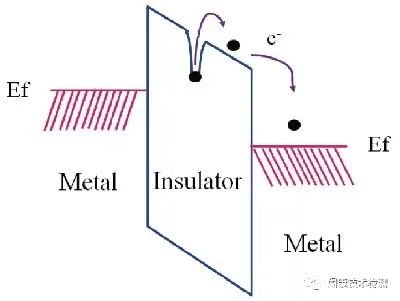

4.跳躍傳導?(Hopping Conduction):

若薄膜之中含有許多連續缺陷存在時,這些連續缺陷會在絕緣體中產生連續缺陷能級,此時不需將電子激發至導電帶,而是藉由彼此相近的缺陷能階進行跳躍傳遞,進而產生電流。當缺陷彼此間距離越小時,其電子跳越能階所需之活化能越小,稱為跳躍傳導 (Hopping Conduction),其能帶圖如圖九所示[21]。

圖九 跳躍傳導之能帶圖

5.穿隧傳導?(Tunneling):

主要是當外加電場過大時,能帶圖 Ec、Ev 更傾斜 (兩側電壓差更大),使得絕緣體能帶變薄,電子可直接穿隧過絕緣層至另一側產生電流,其能帶圖如圖十所示[22]。

圖十 穿隧傳導之能帶圖

6.空間限制電流傳導?(Space Charge Limited Current):

當絕緣體單邊或雙邊形成歐姆接觸時,電極能不間斷地提供載流子,當接觸電極將電子注入至絕緣體或半導體的傳導帶時,由于載流子注入速率大于復合速率,電荷會在絕緣體內慢慢累積,進而影響電流流動,此為空間限制電流傳導 (Space Charge Limited Current),能帶圖如圖十一所示[23]。

圖十一 空間限制電流之能帶圖

交叉數組架構的內存雖擁有較高的組成密度,卻會產生使組件讀取誤判的潛行電流,由 RRAM 與晶體管組成的 1T1R 架構雖具備解決此問題的能力,且已被廣泛應用,為何卻仍不是最終答案?

提高密度的交叉陣列結構,以及解決潛行電流的1T1R 架構

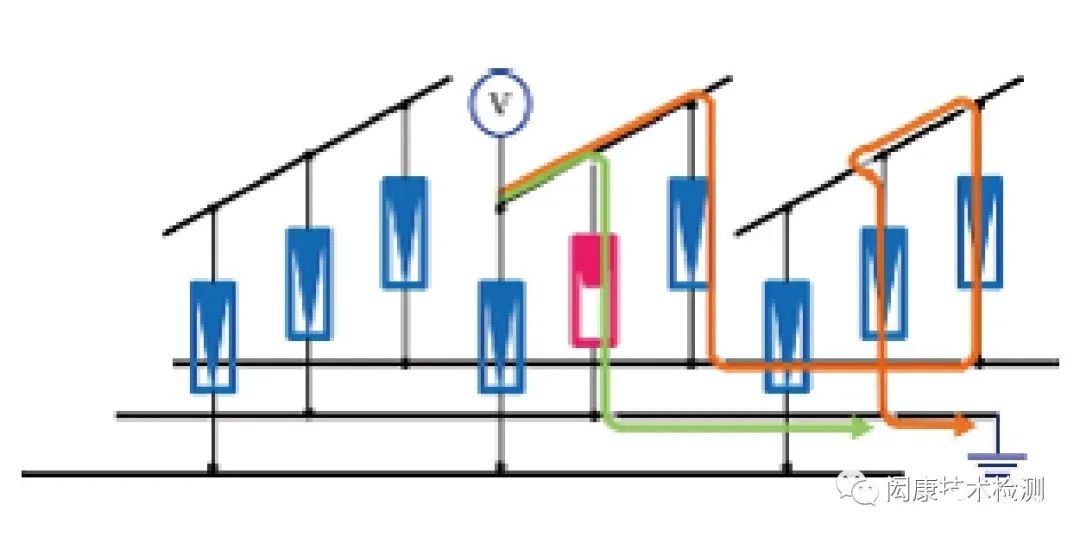

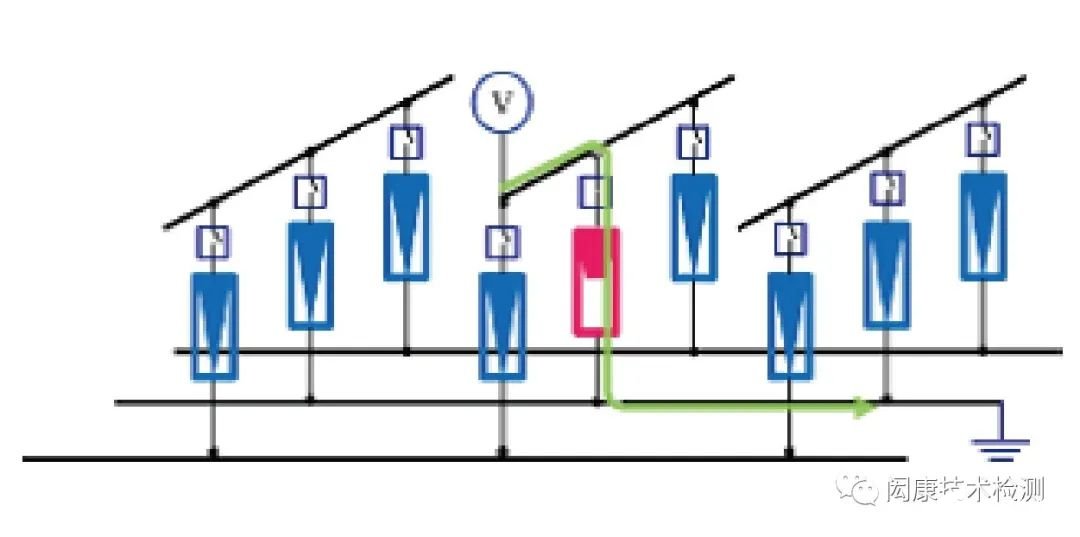

內存為提高集成電路上的密度,發展出一種排列結構方式,稱為交叉數組 (Crossbar Array) [24-26],這種方式雖擁有較高的組成密度,但采用交叉數組結構會產生一個很大的問題,即潛行電流 (Sneak Path Current) 的產生 (如圖十二所示),造成在讀取特定組件狀態時,受鄰近組件影響導致狀態誤判。?

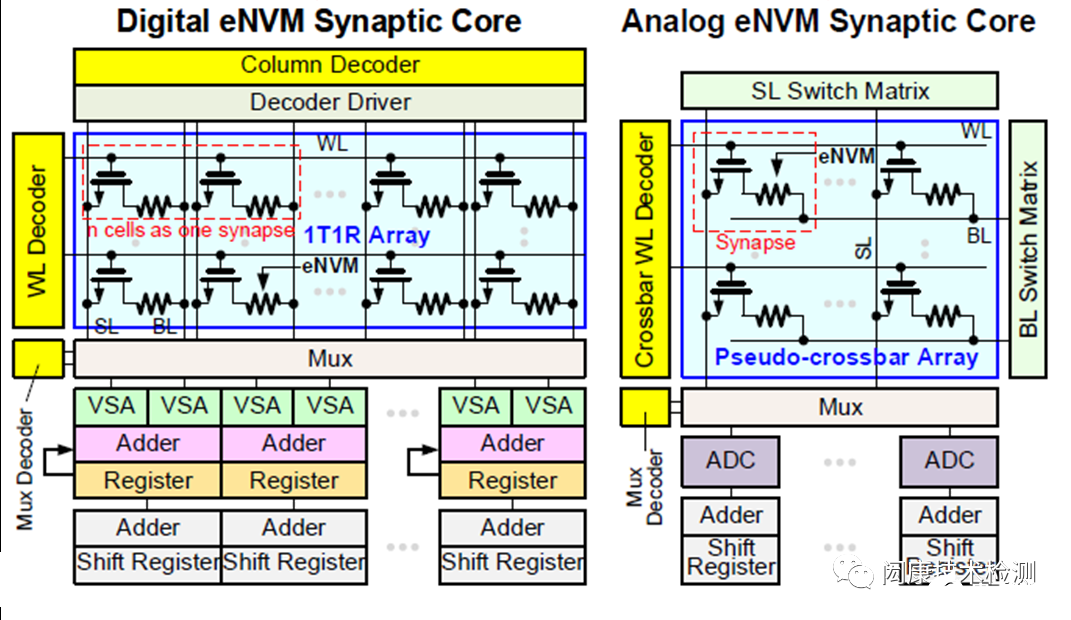

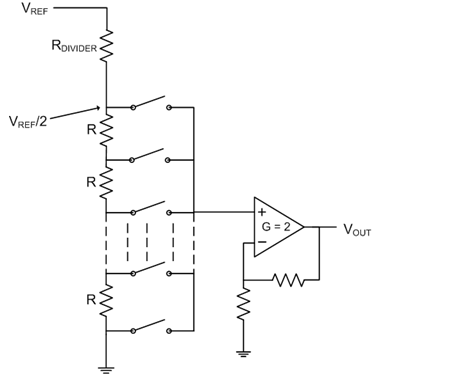

為了解決潛行電流的問題,現今 RRAM 組件已發展出多種架構以解決潛行電流的問題 (圖十三),包括將 RRAM 與晶體管 (Transistor) 組成的 1T1R 架構[26-27],或是 RRAM 與選擇器 (Selector) 組成的 1S1R[28-29] 架構等方式。其中 1T1R 架構因結構簡單且兼容于現今 CMOS 工藝受到廣泛重視,目前多用于強調操作速度與低成本的嵌入式內存 (Embedded Memory) 上,并與微控制器 (Microcontroller Unit) 相互結合,進一步提升其效能。

圖十二 RRAM 形成數組因潛行電流造成組件讀取誤判

圖十三 RRAM 搭配一開關可解決潛行電流問題

然而在晶體管尺寸持續微縮的狀況下,其能承受的電壓將越來越小,這將使 RRAM 可能面臨到操作電壓不足的問題,為解決此問題勢必需從結構與材料著手,因此近年來在 1T1R 架構組件的發展上,更衍生出相關仿生與邏輯運算等重要的新穎應用[30-32]。

生物世界歷經數十億年不斷演化,為了適應多變生態系環境,生物往往發展出十分精致且節能的功能,電子組件利用仿效大腦神經的仿生技術,將為未來電子科技帶來突破性發展。

RRAM 元件近年衍生的新穎應用

由于人工智能 (Artificial Intelligence, AI) 的快速發展,其相關應用包括影像辨識、語音識別、智能監控、智慧駕駛等均受到廣泛矚目,而深度學習等技術亦具備龐大發展潛能。在 AI 相關技術中,最被廣為應用的即是機器學習,機器學習乃是利用多層次人工神經網絡 (Artificial Neural Networks, ANN) 進行數據學習,RRAM 組件因具備非揮發性 (Non-Volatility) 與多位存儲 (Multi-Bit Storage) 之特性,加上低耗能、高操作速度等優點,近年來產生許多新穎應用,包括類神經型態 (Neuromorphic) 與非范紐曼 (Non-Von-Neumann) 架構的智能運算。

因此基于先前研究成果,在薄膜晶體管結合 RRAM 組件所成為的 1T1R 架構下,透過組件數組運用于智能運算的主要架構,其中欲探討并解決的問題有三項:

1. 結合組件特性與工藝,實現仿生 RRAM 數組結構。

2. 利用 RRAM 組件數組結構進一步實現邏輯運算。

3. 最終于 RRAM 組件數組實現人工神經網絡的智能運算。?

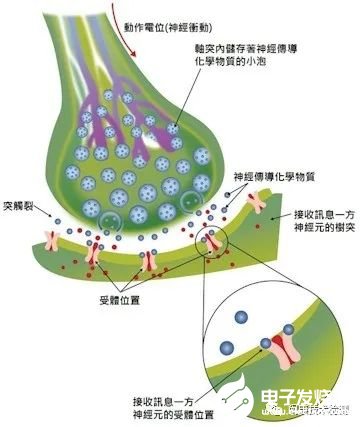

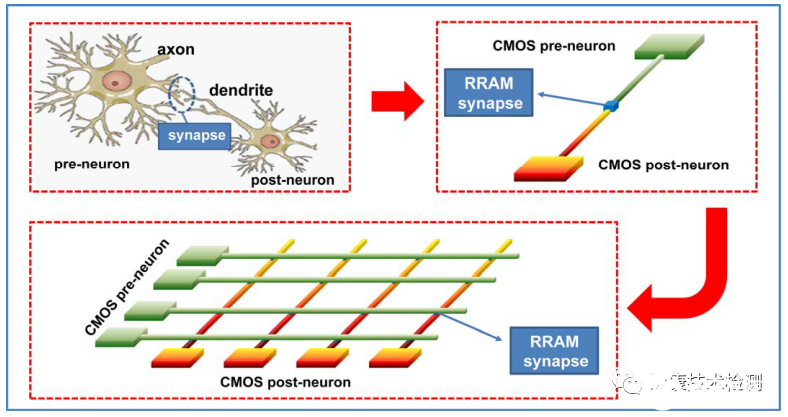

何謂仿生技術?

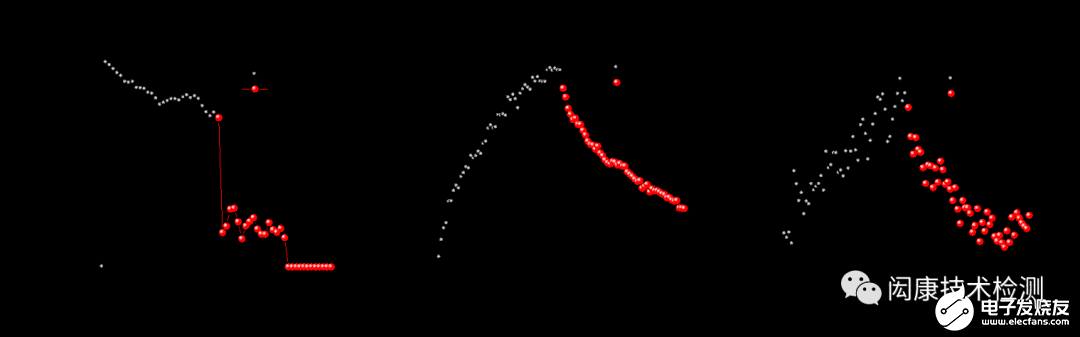

仿效生物能力以提升科學技術稱之為仿生 (Bionic),人類的大腦即是相當好的例子。大腦是一個高效率且低功耗的系統,不只能夠傳遞訊息,且具有學習與記憶的能力。人腦神經元間的連結稱為突觸 (Synapse) (圖十四),突觸間的傳導行為在訊息傳遞的過程中扮演相當重要的角色。突觸間的連接強度具有可調性,稱為脈沖時序依賴可塑性 (Spike-timing-dependent plasticity, STDP),藉由調節進行增益 (Potentiation) 或抑制 (Depression)[33],進行整合后再依體內電位變化,決定是否藉由突觸輸出神經傳導物質至下個神經元中,STDP 同時也是神經生物學中被認為是構成記憶和學習的重要基礎。

圖十四 人腦神經元及突觸示意圖

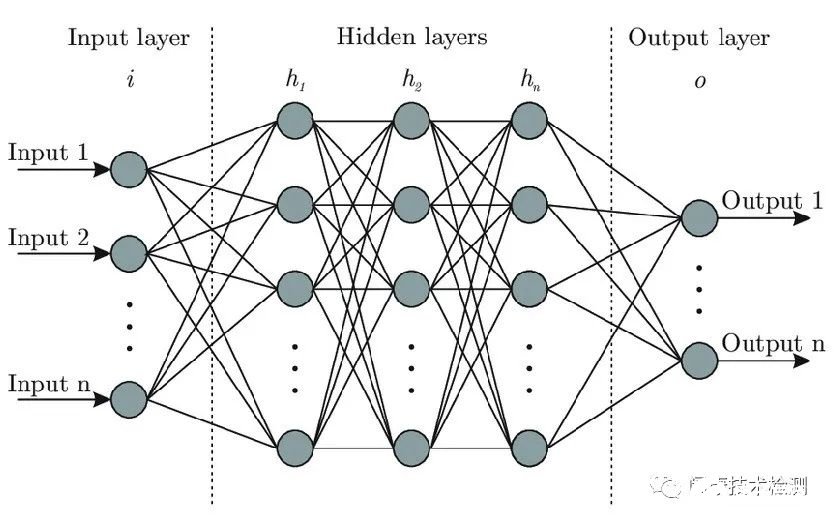

圖十五 人工神經網絡架構示意圖[34]

未來利用電子組件仿效大腦神經訊息傳遞與學習記憶方式,將使電子科技與應用產生突破性發展。現代計算機儲存記憶系以 0 和 1 的數字訊號來進行運算與記憶,而人腦不同于計算機是以模擬訊號來進行傳遞訊息與儲存記憶,藉由對人類中樞神經系統的觀察進而啟發 ANN 概念。如同大腦中神經元 (Neurons) 構成人類的神經網絡,ANN 是由許多節點運算單元 (Nodes) 互相鏈接 (圖十五),通常可區分成三個部分,即輸入層、隱藏層 (通常可為多層) 與輸出層。每一層的所有節點皆與前、后層的節點連結[34],彼此連接形成類神經網絡結構,藉數學計算模型對函式進行估算近似而得輸出結果,使 ANN 在人腦所擅長如圖像語音識別、分類、預測、記憶等領域具備高度發展潛力。

RRAM 元件于仿生技術的應用

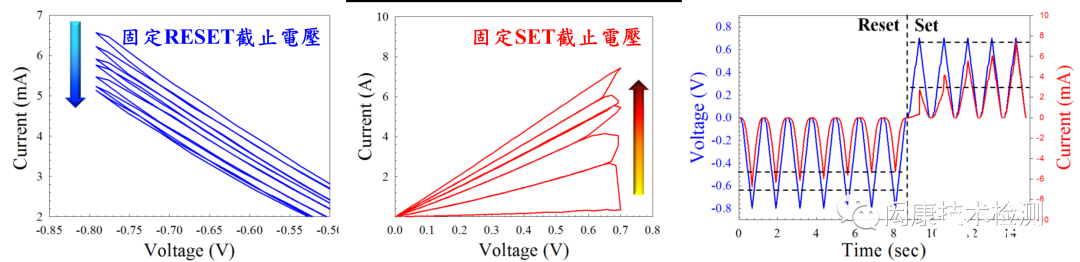

要了解RRAM 元件如何于此領域的應用,則需了解RRAM 元件的多重組態特性(Multi-level ResistanceCharacteristics),其相關研究與控制方法近年已受到廣泛重視[35-37],對于單顆元件的多重阻態操作方式為:當元件在Set 過程時,設定不同的限制電流使元件LRS 阻值可分為多重阻態;而Reset 過程則利用不同截止電壓范圍,使得HRS 可得不同階層變化的阻值,如此即可在單一存儲器元件上擁有多位元存取的能力。

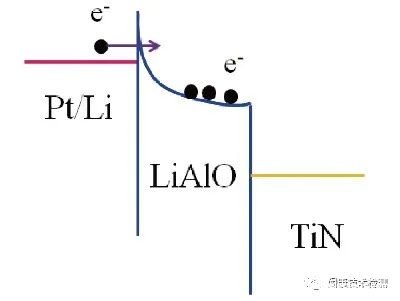

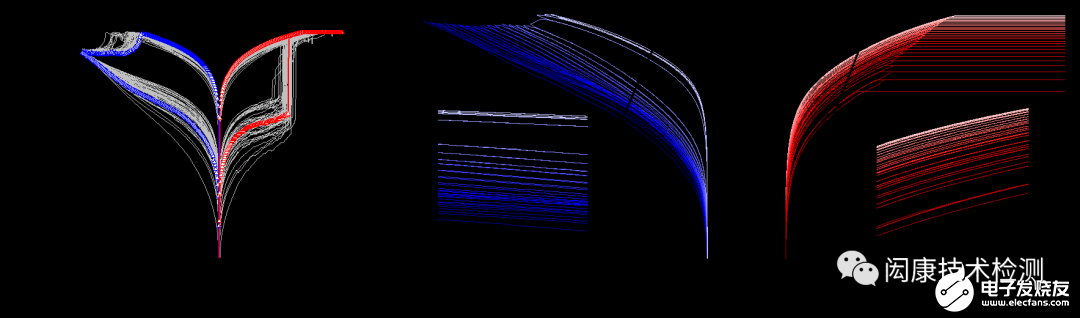

圖16 為一Pt/LiSiO x/TiN 元件,具有良好多位元儲存功能,我們操作在不同的Reset 截止電壓與Set 限制電流條件下,可以使元件阻值變化狀態成為連續態形式,此電阻變化形式又稱為模擬式(Analog)電阻轉換特性。

圖十六 Pt/LiSiOx/TiN 組件直流特性、Reset 與 Set 過程之漸進變化情形

由于上述的操作方式在電路設計與運用上相當復雜,故將 RRAM 組件產生類式的連續態形式尚有另一種操作方法,即利用固定截止電壓對組件進行連續掃描 (Consecutive Voltage Sweeping),藉由電壓掃描方式漸進式地操作改變組件電阻狀態。如圖十七所示,當 Pt/LiSiOx/TiN 組件以 DC 操作時,若輸入一個小于 Reset 電壓并連續操作狀態下,其電流會緩慢下降而阻態會漸漸上升;反之,若輸入一個小于 Set 電壓并連續操作,其電流會緩慢上升阻態會漸漸下降。若將操作電壓與電流對時間軸作圖,即可發現組件的阻值狀態亦呈現漸進方式轉換。上述除利用電阻值或電流參數呈現組件切換特性外,一般研究則多以電導 (Conductance) 變化呈現組件阻值變換特性。?

圖十七 Pt/LiSiOx/TiN 組件已連續定電壓掃描下,阻值呈漸進方式變化

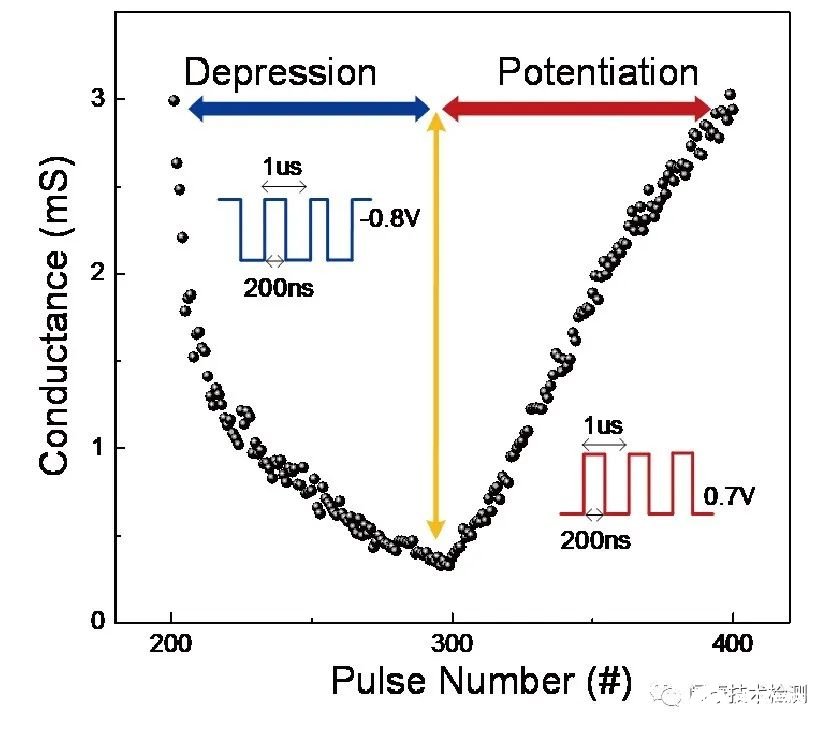

RRAM 組件如欲仿效突觸的行為,則需利用組件電導 (電阻) 的漸變特性模擬突觸權重的連續調節,進而模擬突觸的可塑性,因此相關 RRAM 組件的突觸特性關鍵參數相當重要,包括:

Linearity:電導調節線性度

Precision:權重 (電導值) 調節精度

ON/OFF Ratio:在脈沖操作下組件可調節的最大與最小電導值范圍

Variation:組件的 Cycle-to-Cycle & Device-to-Device 變化度

Defective Rate:組件數組良率 (Yield) 與阻態保持 (Retention) 特性

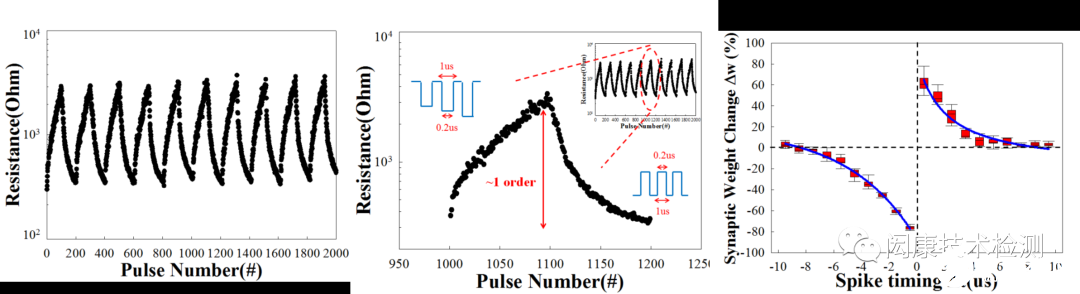

圖十八系將 Pt/LiSiOx/TiN 組件利用連續脈波操作,以驗證組件仿真神經元突觸的仿生特性,藉由調整脈波電壓大小、脈沖時間、脈波次數,即可改變組件阻態與導電性,使組件組態由 LRS 連續緩升至 HRS,再從 HRS 緩降至 LRS,以連續正負電壓脈波操作仿真電阻增益 (Potentiation) 及抑制 (Depression) 行為。

圖十八 Pt/LiSiOx/TiN 組件以連續脈波操作下阻值逐漸變化與 STDP 測試結果

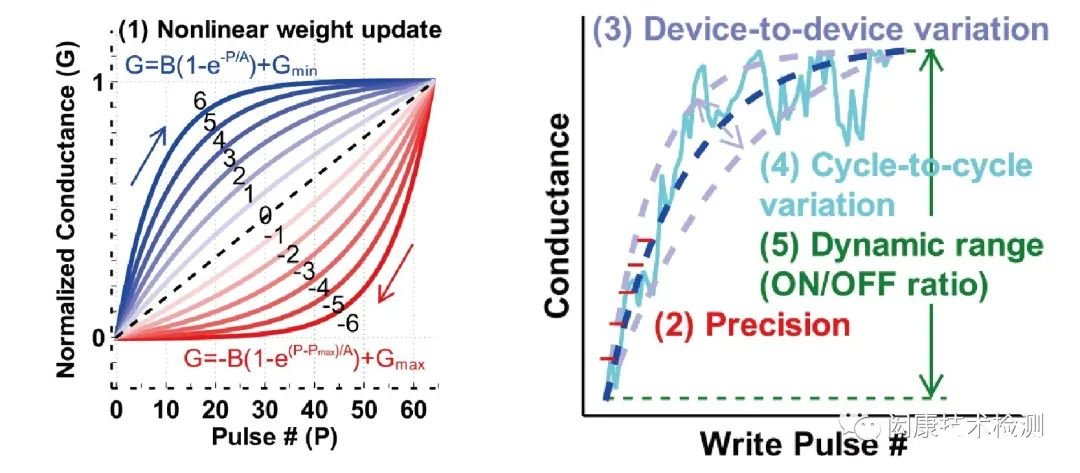

由 STDP 實驗結果顯示,此組件仿效大腦突觸行為將有助于類神經網絡的發展。RRAM 欲作為仿生組件使用,則其阻值變化狀態須具備連續態形式,藉以反復設定多種突觸權重數值應用于類神經運算。理想的 RRAM 組件運用于突觸操作的需求包括[38] (圖十九、圖二十):

穩定多階的電導狀態數

在脈沖操作下,擁有線性且對稱的組件電導值變化

良好的組件均勻度,減小 Cycle-to-Cycle、Device-to-Device 的變化

足夠的組件電導變化范圍 (ON/OFF Ratio)

圖十九 RRAM 組件有效電導狀態

圖二十 RRAM 組件的突觸特性關鍵參數[38]

通常界面型 RRAM 組件的阻態變化雖較為線性,但是因其記憶窗口、持久性 (Retention) 與耐讀寫度 (Endurance) 的可靠度較差,實際運用上有相當難度,故尋求阻值變化具高度線性的 RRAM 組件對于仿生組件操作相當重要。先前研究結果顯示,RRAM 組件中間絕緣層若含有高氧空穴密度,容易形成導電路徑,其電阻轉換多為突升或突降,意味著電阻切換行為如同數字訊號的 0 與 1,無法表現出模擬式的電阻漸變切換行為;而絕緣層中含氧空穴密度的 RRAM 組件,可能較有機會表現出模擬式電阻切換特性,同時能兼具較佳的可靠度[38-39]。除了 LiSiOx 材料外,先前實驗結果亦發現基于 HfOx 材料結合不同電極或迭層組合,也可具備模擬式電阻轉換特性 (圖二十一)。

圖二十一 HfOx 材料結合不同電極或迭層組合實現模擬式電阻切換特性

圖二十二 模擬式 RRAM 組件由單一組件進而形成數組組件,對于仿生電子組件發展有相當重要性[35]

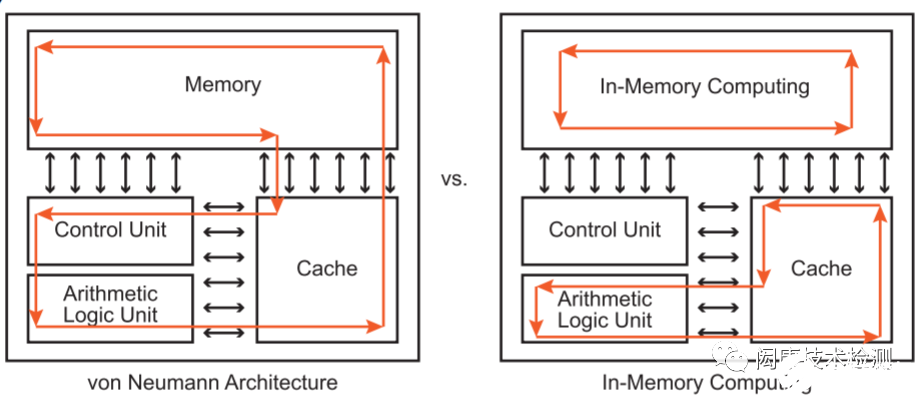

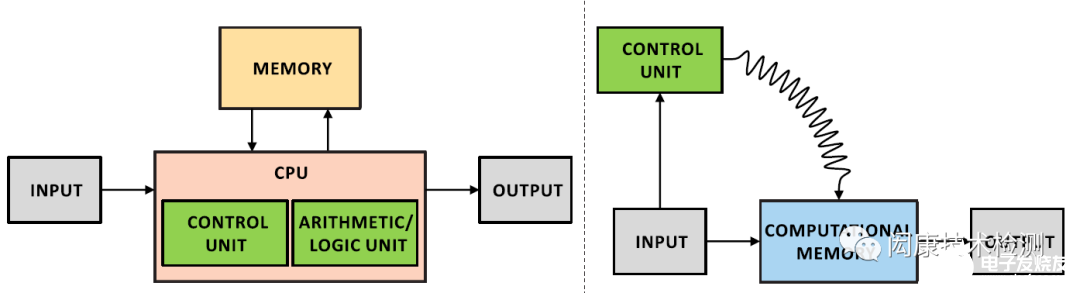

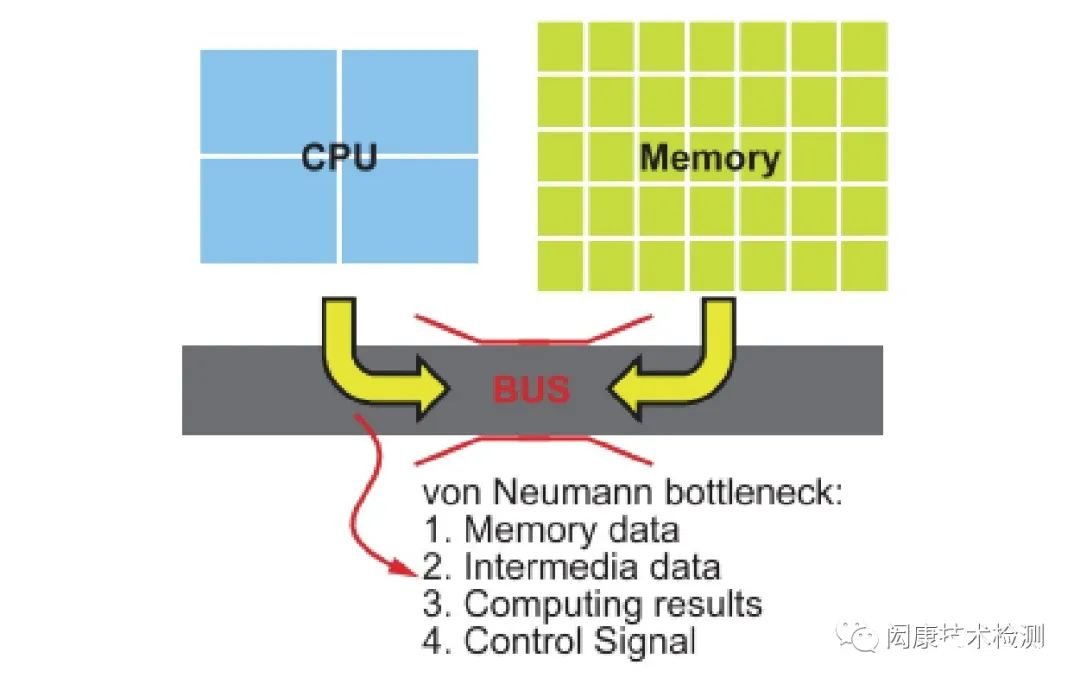

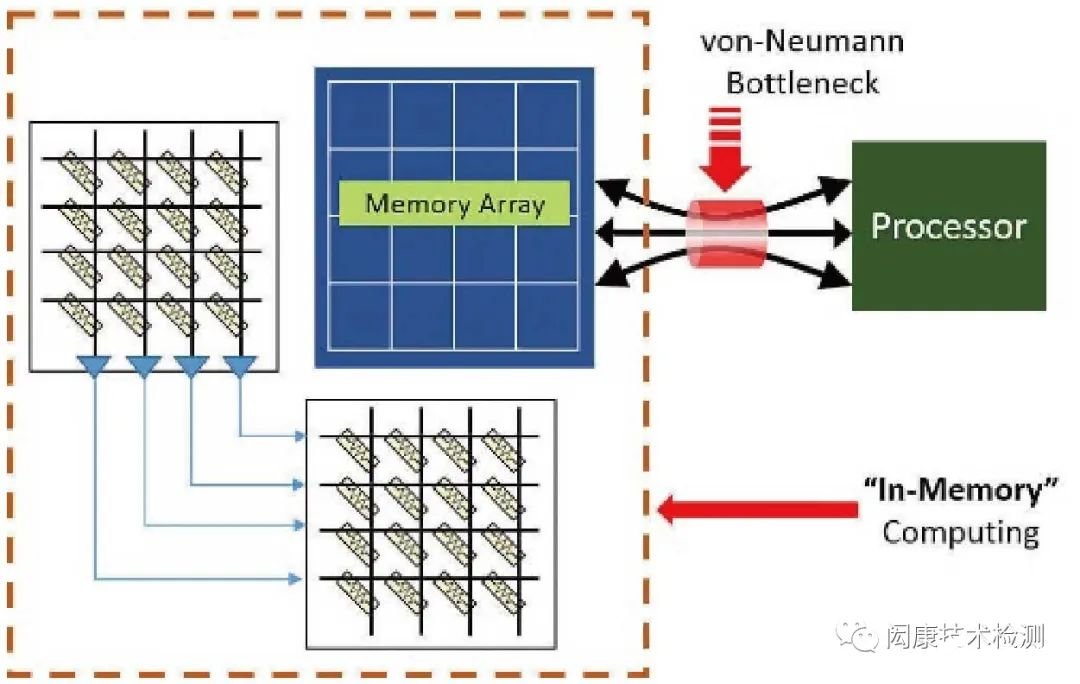

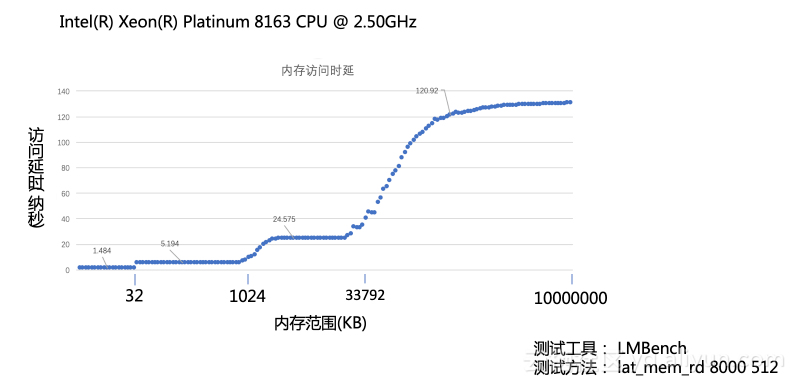

現今計算機均采用馮紐曼型架構 (Non-Von-Neumann),即信息處理和存儲為分立架構 (圖二十三),這樣的方式使總線傳輸速度限制了數據的存儲和指令周期。而計算機邏輯運算的實現系基于互補式金屬氧化物半導體 (Complementary Metal-Oxide-Semiconductor, CMOS) 架構,邏輯電路的輸入與輸出系依賴電壓的高或低電位來執行運作,但是邏輯運算結果通常需仰賴外加電路或裝置才能進行儲存。而利用馮紐曼 (Non-von-Neumann) 計算架構,可以實現內存內運算 (Computing in Memory),實際運算過程是經過內存的數據數據,直接在內存內先行運算,再將結果傳送至處理器進行后續分析,能以低功耗、高效率的方式,提升計算機運作效能[40]。

圖二十三 馮紐曼型架構與內存內運算之系統架構[38]

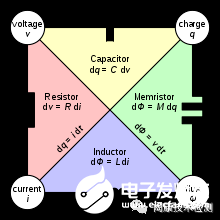

除了電阻、電感與電容組件外,RRAM 被視為是第四種基本被動組件 (圖二十四)[41],RRAM 組件兼具非揮發特性與類神經運算的功能,使其可在單一組件上結合計算與儲存之功能,實現內存內計算 (In-Memory Computing) 架構,因此非常有機會做為馮紐曼 (Non-von-Neumann) 計算架構之核心組件 (如圖二十五)。

圖二十四 RRAM 是第四種被動組件[41]

圖二十五 馮紐曼計算架構可單一組件結合計算與儲存功能

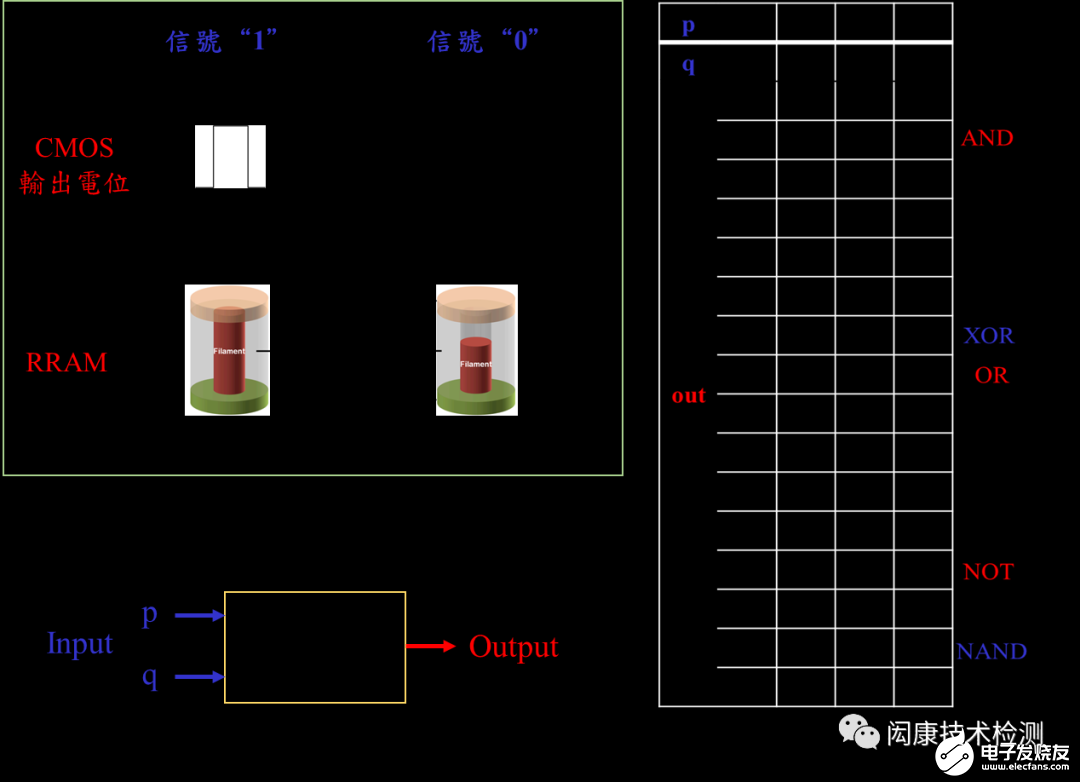

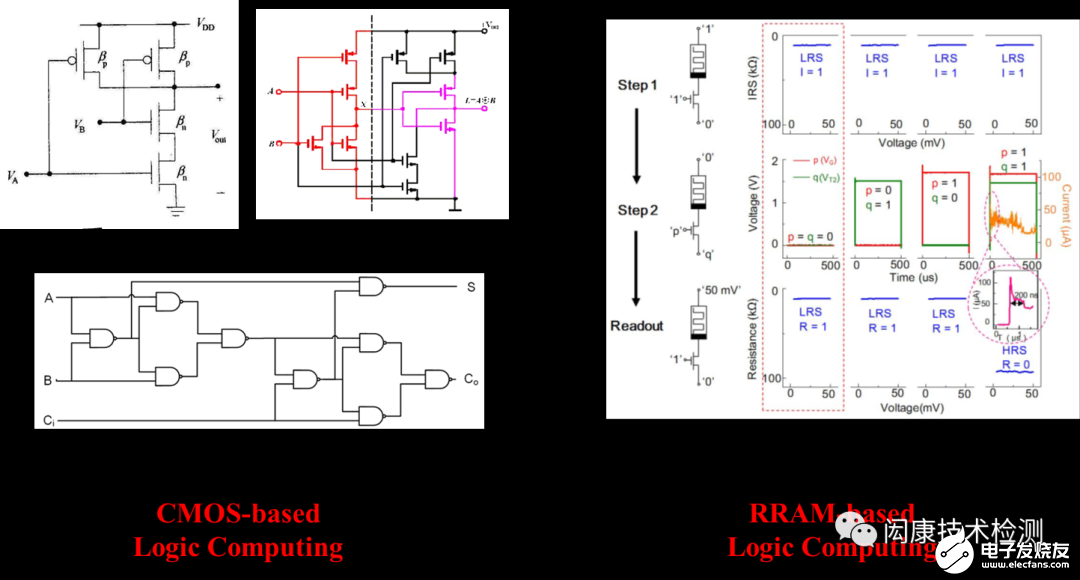

利用 RRAM 組件取代邏輯電路中的晶體管,可以有效節省組件面積。以 RRAM 做為邏輯組件運算時,分別以 HRS 與 LRS 代表數字訊號的 0 與 1,透過操作組件的 HRS 或 LRS 狀態改變來實現邏輯運算。而在多 R 數組組件中,即可將組件阻值狀態改變做為參數以實現邏輯運算(圖二十六),并將結果直接儲存在 RRAM 組件中,這種兼具數字訊號存儲與邏輯計算的功能,省去了一般傳統計算機架構之緩存器功能,可以有效降低數據傳輸的負荷,得以提高處理速度和效率,且具備低功耗的優點[42-43]。但是相較于傳統 CMOS 電路,如何基于不同的 RRAM 組件結構,完整實現邏輯運算中的邏輯完整性 (Functional completeness)、計算復雜度 (Computation complexity) 以及邏輯的可重構性 (Reconfigurability),關系著 RRAM 組件是否能運用于馮紐曼計算架構,值得我們持續深入研究探討其他可能的運用 (圖二十七)。

圖二十六 利用 RRAM 組件高低阻值狀態做為輸入端,可運用于布爾邏輯運算

圖二十七 CMOS 電路基于晶體管架構實現邏輯運算,而 RRAM 組件可利用 1T1R 結構實現邏輯運算

展望

RRAM 可以藉由交叉數組的形態實現內存數組架構,以極低功耗實現內存內計算技術,在各種 AI 技術發展龐大的應用潛力,極有機會整合目前已面臨發展瓶頸的各式內存組件,成為未來通用內存。

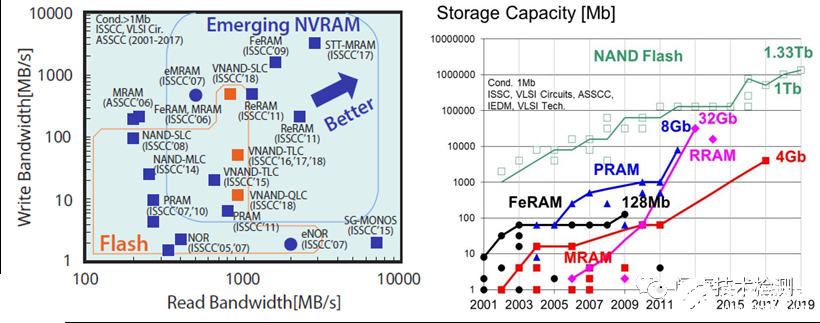

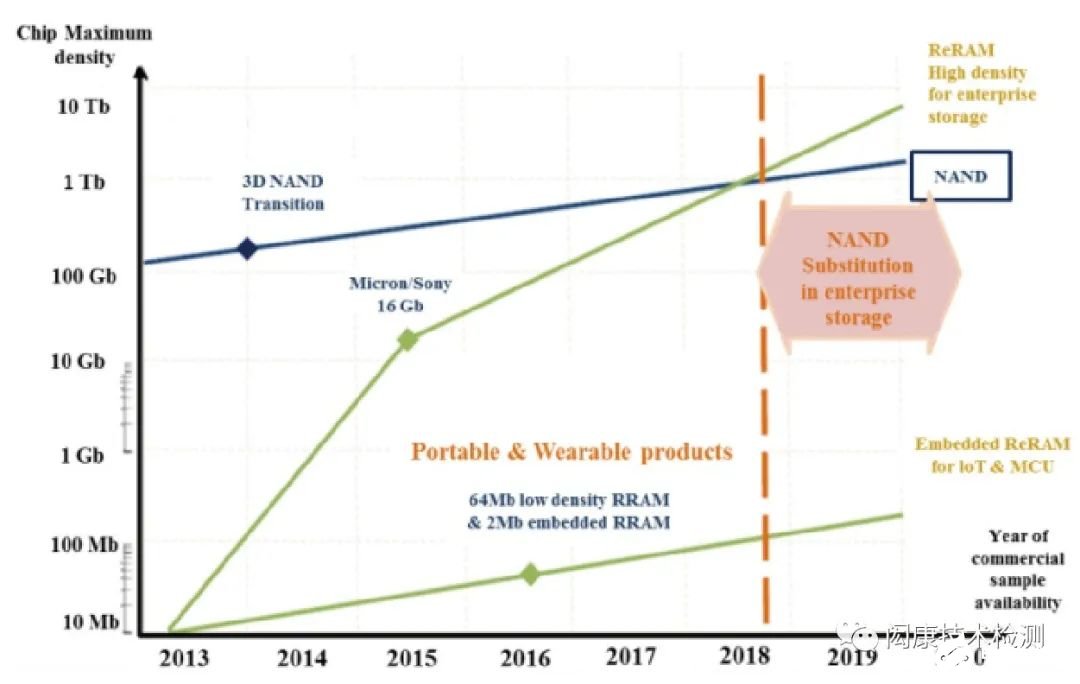

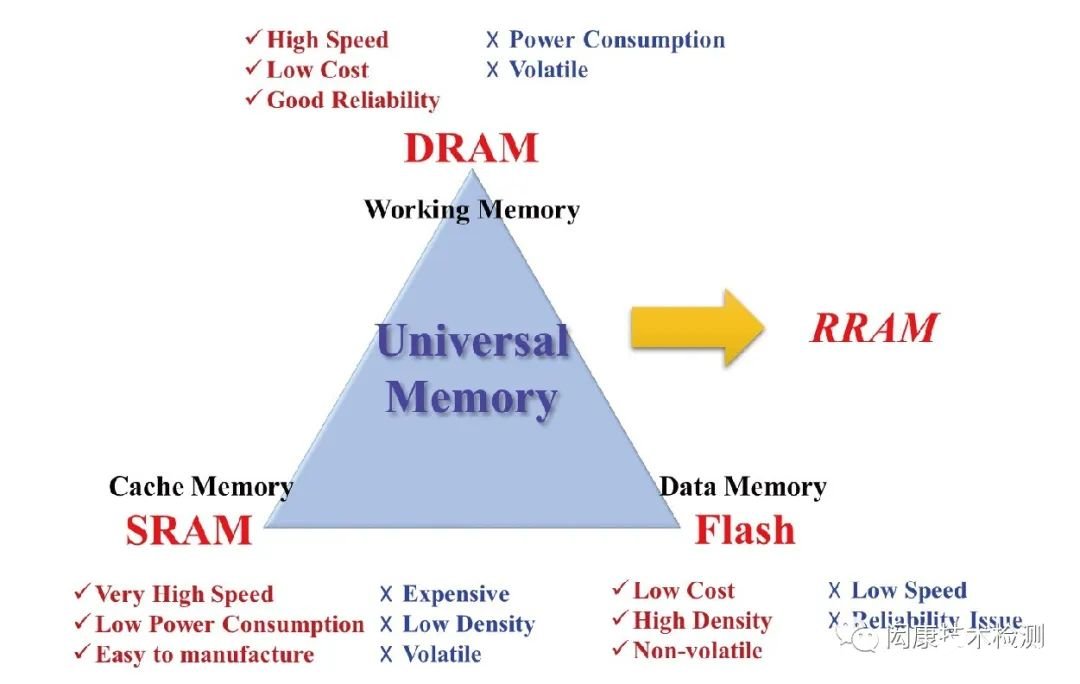

目前傳統浮動柵極結構 (Floating-Gate Structure) 內存遭遇到微縮的困境,對此各方開始極力發展次世代內存,期能透過全新的儲存方式或內存結構取代 Flash 內存。除了希望能提升組件操作的帶寬及可靠度之外,同時也希望能透過簡單的交點式結構 (Cross-point Structure) 達成高度組件微縮,增加內存儲存容量 (如圖二十八所示)。而 RRAM 組件擁有低操作電壓、低功耗、操作速度較 NAND Flash 快 1000 倍以上的特性,還兼具低成本、非揮發性及高度可微縮性的優點[44],除可作為工作內存 (Working Memory) 外,還有制作高密度內存潛力。除了上述優點外,RRAM 的材料與工藝與目前 CMOS 后段工藝 (Back end of line, BEOL) 具有高度兼容性,所以 RRAM 相當具有實際產品化潛力與可行性 (圖二十九)[45],極有機會整合目前已面臨發展瓶頸的各式內存組件,成為通用內存 (Universal Memory)(圖三十

。

圖二十八 不同新興內存的操作帶寬以及內存的存儲容量[44]

圖二十九 RRAM 未來的發展趨勢[45]

圖三十 RRAM 有機會整合內存成為通用內存

近年利用 RRAM 組件結合人工智能運算的應用受到廣泛矚目,AI 即是基于 ANN 結構運用在圖像識別、語音識別等場合,不同的神經網絡 (如卷積神經網絡 CNN、循環神經網絡 RNN) 亦可用于人工智能核心,提供如智能監控、智能駕駛等相關應用。在大多數情況下,ANN 能在外界信息基礎上改變內部結構,是一種具備學習 (Learning) 功能的自適應系統。?

AI 的運作就是基于 ANN 架構模仿人類大腦神經進行學習動作,透過輸入大量已知答案數據對計算機進行訓練,若結果出現錯誤則調整突觸間權重 (Weight),重復進行直到輸出結果接近于正確答案,最終使計算機在接受輸入訊息后,能夠根據先前的學習經驗做出判斷結果。為了得到正確的輸出結果,ANN 系統需進行大量反復矩陣乘法運算 (Iterative Matrix Multiplication Operation),故如何使計算機進行快速運算且得到正確結果,同時又能降低能量消耗,這對未來人工智能系統發展至關重要。?

現代計算機架構主要采用范紐曼架構 (Von Neumann Architecture) 中央處理器負責運算,CPU 從儲存數據的內存中取得數據進行運算,再將結果回傳至內存儲存。由于內存讀寫速度遠較 CPU 運算來得慢,故于處理大量的數據運算時,不斷地來回讀取會大幅限制計算機的處理速度 (如圖三十一所示)。近年來基于非揮發性內存的人工神經網絡運算引起了許多關注,RRAM 可以藉由交叉數組 (Crossbar) 的形態實現內存數組架構,并以極低功耗進行運算,而數組結構更可用于向量與矩陣乘法運算,實現內存內計算 (In-memory Computing) 技術,在未來對于各種 AI 技術發展有很大的應用潛力[46] (圖三十二)。

圖三十一 馮紐曼計算架構之瓶頸[40]

圖三十二 馮紐曼計算架構有機會突破計算與儲存間的架構瓶頸[46]

一個新興內存技術的興起,將帶動全球的 IT 產業,影響的產業層面相當廣 (圖33),從產業鏈上游的 Microprocessor Unit、Fabless Companies 與Integrated Device Manufacturers (IDM) 公司,到中間的半導體制造產業 (Foundries),最后至應用端,而其中還包含了很多設備產業的參與。根據調查報告,未來幾年是 RRAM 發展最關鍵的時期,各國際大廠與新興公司都分別針對 MCU、Mass Data Storage 以及以內存為中心的全新運算架構等運用,制定出明確的 RRAM 開發 Roadmap (圖三十四)。大數據結合 AI 科技的應用持續推動內存技術,需要更密切結合系統運算資源,無論是從性能或效率方面來看,當今多核心處理架構已無法滿足未來實時運算需求。在這個關鍵時期,利用 1T1R 組件數組的仿生特性與邏輯運算,拓展組件在智能運算的發展與實際運用價值已顯而易見 (圖三十五)。

圖三十三 新興內存技術所影響的諸多產業鏈[45]

圖三十四 相關半導體大廠對 RRAM 的開發 Roadmap[45]

圖三十五 基于 1T1R 組件數組架構基礎上實現智能運算功能[38]

內存在整個半導體產業中占據極重要的地位,目前全球內存市場仍是以 DRAM 與 NAND Flash 為主流,其在內存應用領域的占比超過 90%。然而,近年來隨著半導體產業持續朝更小的技術節點邁進,DRAM 與 NAND Flash 嚴重面臨到尺寸微縮挑戰,DRAM 目前已接近微縮極限、而 NAND Flash 則全力朝 3D 架構轉型;除此之外,此兩者在高速運算的進階應用上也遭遇到阻礙。在人工智能、物聯網、5G 強勢崛起的數字時代下,數據處理需求量暴增,半導體業者皆加大對新興內存技術的研發與投資力道,開始尋求成本更佳、速度更快、效能更好的儲存解決方案。?

目前已開發的次世代內存例如 FRAM、PRAM、MRAM、及 RRAM 等,無論是在尺寸縮微、操作能耗、讀寫速度、運作次數等方面,皆完勝現今穩固的 DRAM 及 NAND Flash 存儲架構。與 DRAM 相比,其可以降低至少 20% 的功耗,并且由于它們都可以在不擦除資料的情況下直接覆蓋舊數據,此可節省閃存 (Flash Memory) 所需的高擦除能耗、及因擦除數據導致的時間延遲,并減少或消除了其對電荷泵的需求。而所有新內存技術都能夠對于儲存地址的數據隨機存取,也無須如目前內存的架構作法,采用個別保留兩個數據副本在閃存及 DRAM 的動作來實現單次存取目的。上述這些功能特點,都將帶來顯著的功率節省以及性能提升效果。此外,新興內存技術也具有實現芯片內嵌設計的潛力,可將邏輯 IC 與內存組件整合在同一顆芯片中。這樣的設計不僅可以達成最佳的傳輸性能,同時也縮小了芯片體積。以單一芯片就能達成運算與儲存的功能,這對于物聯網或人工智能裝置、經常需要大量數據運算與數據儲存來說,非常具有吸引力。?

然而,盡管有許多新興的存儲組件技術已經研發出來,但在這競爭激烈的規模產業中,只有極少數有機會成功。就目前次世代內存的發展現況來看,仍沒有一種新型內存速度可以像 SRAM 及 DRAM 那樣快。并且,在未來幾年之內,也沒有任何一款設計架構可以在成本上與 NAND Flash 競爭。在具有經濟規模的供需基礎下,NAND Flash 制造價格非常便宜,此將致使多數芯片供貨商愿意接受閃存復雜的寫入過程與高耗能代價來換取低成本優勢,以滿足消費者的期望。因此,如何在低成本前提下來實現小尺寸、高計算能力、以及超低功耗等目標,將是次世代內存在激烈的市場競爭中勝出之關鍵。?

「電阻式內存」目前是取代現有內存應用技術最具吸引力的方案。相對于其它新興存儲技術而言,電阻式內存除了在功耗與速度方面有相當的優勢之外,由于其結構特別簡單,而電阻材料也可采用半導體工藝通用的二元金屬氧化物例如二氧化鈦、氧化鉿、氧化鎳等來制作,因此也能具有低成本的產品特點。根據市調機構 GII 預測,全球電阻式內存市場自 2018 至 2023 年期間成長率 CAGR 將高達 29.9%。就市場投入的情形來看,晶圓代工大廠臺積電和三星的競爭,近年來由邏輯芯片快速擴及到內存市場,兩家公司皆將電阻式內存列為重點技術開發目標。而半導體設備大廠美商應用材料公司 (Applied Materials Inc.) 也于 2019 年發布其 Endura Impulse PVD 平臺,可精確沉積并控制電阻式內存中使用的多種材料。此外,2020 年初電阻式內存制造商 Crossbar 和其他幾家公司也共同成立了一個名為 SCAiLE 的 AI 聯盟,致力于提供高速且節能的 AI 平臺。該聯盟的主要工作是將電阻式內存、先進的計算器硬件、以及優化的神經網絡算法作結合,用以提供低功耗的智慧運算解決方案。隨著眾多半導體廠及設備供貨商相繼投入推動,相信電阻式內存勢必會快速崛起,成為次世代內存的市場主流技術。?

本篇文章針對電阻式內存的技術架構及其應用提供了全面性介紹,同時也清楚闡述了該組件運作時電阻非線性變化的物理機制,可有效幫助讀者快速地學習了解此最具市場潛力的前瞻技術。成大王永和教授的研究領域十分廣泛,包括半導體組件及物理、微波集成電路、以及光電組件等,其團隊發表的學術期刊及會議論文超過 400 篇、獲證的相關專利超過 100 件。此外,王教授于 2007 年至 2020 年期間,曾先后擔任中國臺灣重要科研單位副院長及院長,對于建構臺灣地區的研發平臺、支持學術研究、推動前瞻科技、及培育科技人才等,也都有極大的貢獻。

總結

內存在整個半導體產業中占據極重要的地位,目前全球內存市場仍是以 DRAM 與 NAND Flash 為主流,其在內存應用領域的占比超過 90%。然而,近年來隨著半導體產業持續朝更小的技術節點邁進,DRAM 與 NAND Flash 嚴重面臨到尺寸微縮挑戰,DRAM 目前已接近微縮極限、而 NAND Flash 則全力朝 3D 架構轉型;除此之外,此兩者在高速運算的進階應用上也遭遇到阻礙。在人工智能、物聯網、5G 強勢崛起的數字時代下,數據處理需求量暴增,半導體業者皆加大對新興內存技術的研發與投資力道,開始尋求成本更佳、速度更快、效能更好的儲存解決方案。?

目前已開發的次世代內存例如 FRAM、PRAM、MRAM、及 RRAM 等,無論是在尺寸縮微、操作能耗、讀寫速度、運作次數等方面,皆完勝現今穩固的 DRAM 及 NAND Flash 存儲架構。與 DRAM 相比,其可以降低至少 20% 的功耗,并且由于它們都可以在不擦除資料的情況下直接覆蓋舊數據,此可節省閃存 (Flash Memory) 所需的高擦除能耗、及因擦除數據導致的時間延遲,并減少或消除了其對電荷泵的需求。而所有新內存技術都能夠對于儲存地址的數據隨機存取,也無須如目前內存的架構作法,采用個別保留兩個數據副本在閃存及 DRAM 的動作來實現單次存取目的。上述這些功能特點,都將帶來顯著的功率節省以及性能提升效果。此外,新興內存技術也具有實現芯片內嵌設計的潛力,可將邏輯 IC 與內存組件整合在同一顆芯片中。這樣的設計不僅可以達成最佳的傳輸性能,同時也縮小了芯片體積。以單一芯片就能達成運算與儲存的功能,這對于物聯網或人工智能裝置、經常需要大量數據運算與數據儲存來說,非常具有吸引力。?

然而,盡管有許多新興的存儲組件技術已經研發出來,但在這競爭激烈的規模產業中,只有極少數有機會成功。就目前次世代內存的發展現況來看,仍沒有一種新型內存速度可以像 SRAM 及 DRAM 那樣快。并且,在未來幾年之內,也沒有任何一款設計架構可以在成本上與 NAND Flash 競爭。在具有經濟規模的供需基礎下,NAND Flash 制造價格非常便宜,此將致使多數芯片供貨商愿意接受閃存復雜的寫入過程與高耗能代價來換取低成本優勢,以滿足消費者的期望。因此,如何在低成本前提下來實現小尺寸、高計算能力、以及超低功耗等目標,將是次世代內存在激烈的市場競爭中勝出之關鍵。?

「電阻式內存」目前是取代現有內存應用技術最具吸引力的方案。相對于其它新興存儲技術而言,電阻式內存除了在功耗與速度方面有相當的優勢之外,由于其結構特別簡單,而電阻材料也可采用半導體工藝通用的二元金屬氧化物例如二氧化鈦、氧化鉿、氧化鎳等來制作,因此也能具有低成本的產品特點。根據市調機構 GII 預測,全球電阻式內存市場自 2018 至 2023 年期間成長率 CAGR 將高達 29.9%。就市場投入的情形來看,晶圓代工大廠臺積電和三星的競爭,近年來由邏輯芯片快速擴及到內存市場,兩家公司皆將電阻式內存列為重點技術開發目標。而半導體設備大廠美商應用材料公司 (Applied Materials Inc.) 也于 2019 年發布其 Endura Impulse PVD 平臺,可精確沉積并控制電阻式內存中使用的多種材料。此外,2020 年初電阻式內存制造商 Crossbar 和其他幾家公司也共同成立了一個名為 SCAiLE 的 AI 聯盟,致力于提供高速且節能的 AI 平臺。該聯盟的主要工作是將電阻式內存、先進的計算器硬件、以及優化的神經網絡算法作結合,用以提供低功耗的智慧運算解決方案。隨著眾多半導體廠及設備供貨商相繼投入推動,相信電阻式內存勢必會快速崛起,成為次世代內存的市場主流技術。?

本篇文章針對電阻式內存的技術架構及其應用提供了全面性介紹,同時也清楚闡述了該組件運作時電阻非線性變化的物理機制,可有效幫助讀者快速地學習了解此最具市場潛力的前瞻技術。成大王永和教授的研究領域十分廣泛,包括半導體組件及物理、微波集成電路、以及光電組件等,其團隊發表的學術期刊及會議論文超過 400 篇、獲證的相關專利超過 100 件。此外,王教授于 2007 年至 2020 年期間,曾先后擔任中國臺灣重要科研單位副院長及院長,對于建構臺灣地區的研發平臺、支持學術研究、推動前瞻科技、及培育科技人才等,也都有極大的貢獻。

審核編輯:黃飛

電子發燒友App

電子發燒友App

評論