本文最初于 DesignCon 大會上發表并獲得了最佳論文獎提名,其中研究了DDR4 的偽漏極開路驅動器,以及其使用對接收器的功耗和 Vref 電平而言的意義。

DDR4 是 JEDEC DRAM 部件系列的下一階段,旨在滿足市場對更高速度和更低功耗的需求。這些因素構成了 DDR4 的新特性以及設計 DDR4 系統時需要予以考慮的新要求。

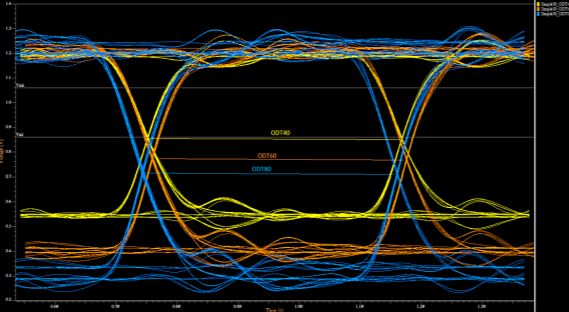

相比以前的 DDR 技術,新的 DDR4 標準除了數據速率更快以外,還包含其他變化,而這些變化將會對電路板設計工程師產生影響。DDR4 中的新因素,例如不對稱端接方案、數據總線反轉和利用眼圖模板驗證信號等,都需要通過仿真驗證設計的新方法。

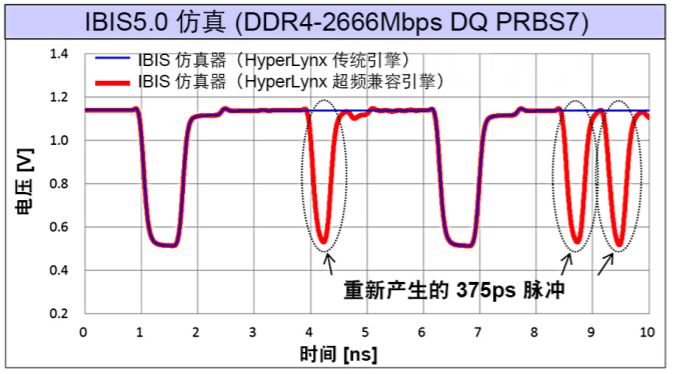

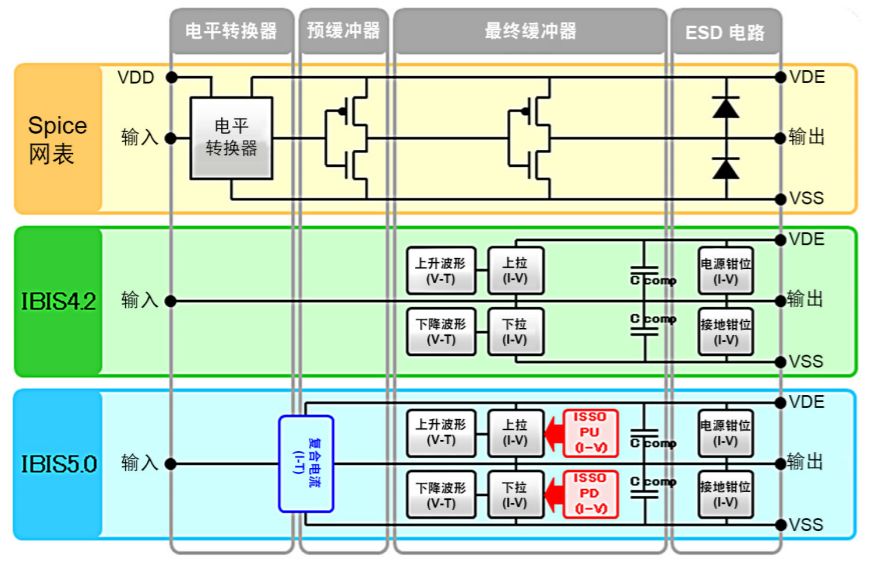

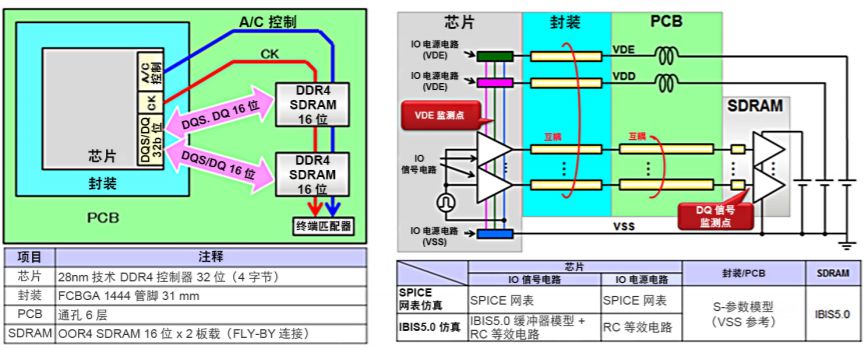

本文研究了 DDR4 偽漏極開路 (POD) 驅動器對數據總線信號傳輸的影響,并介紹了動態計算 DRAM 內部 VrefDQ 電平以進行數據眼圖分析的方法論,生成和驗證數據眼圖的方法論,以及將寫入均衡和校準整合到仿真中的方法。此外,通過將電源完整性效應納入信號完整性分析來評估同步開關噪聲 (SSN),對于電路板設計和時序收斂也很重要,本文將借助示例加以闡述。本文還將描述一個采用 IBIS 5.0 功耗分析模型的系統設計示例,其中包括比較了 IBIS 結果與晶體管級模型以研究仿真精度。風,毫無預兆地席卷整片曠野,撩動人的思緒萬千。

-

驅動器

+關注

關注

54文章

8655瀏覽量

149547 -

接收器

+關注

關注

15文章

2566瀏覽量

73681

原文標題:技術白皮書 | DDR4 電路板設計與信號完整性驗證挑戰

文章出處:【微信號:gh_1a93bb3ab6f3,微信公眾號:Mentor明導PADS】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

如何使DDR4降低系統功耗?要借助POD電平

介紹DDR3和DDR4的write leveling以及DBI功能

怎樣降低DDR4系統功耗

MAX232雙驅動器接收器的數據手冊免費下載

具有漏極開路輸出的 SN74AUP2G07低功耗雙路緩沖器/驅動器數據表

漏極開路輸出的十六進制反相器緩沖器/驅動器SN74LVC06A數據表

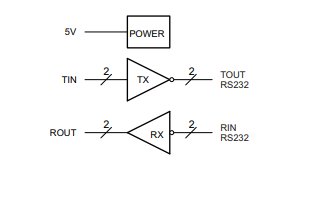

將 LVDS 驅動器與 Sub-LVDS 接收器對接應用說明

DDR4偽漏極開路驅動器及對接收器的功耗和Vref電平而言的意義

DDR4偽漏極開路驅動器及對接收器的功耗和Vref電平而言的意義

評論