如果布線不需要額外的層,為什么還要用它呢?難道減少層不會讓電路板更薄嗎?如果電路板少一層,難道成本不是更低么?但是,在一些情況下,增加一層反而會降低費(fèi)用。

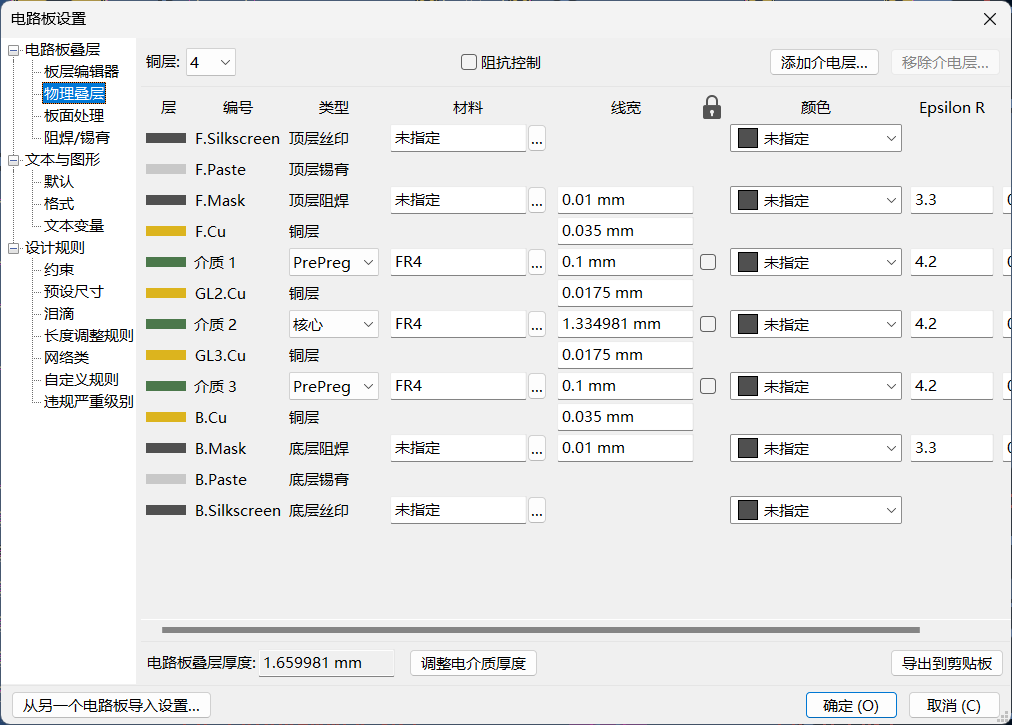

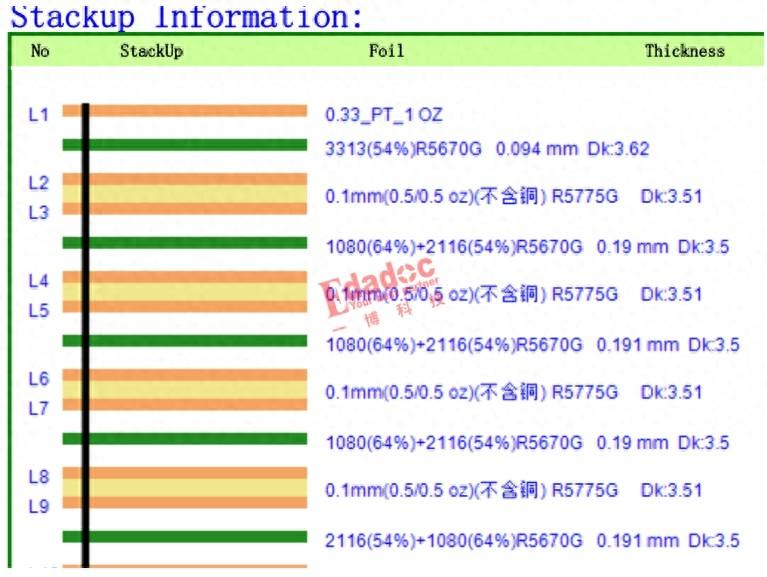

PCB板有兩種不同的結(jié)構(gòu):核芯結(jié)構(gòu)和敷箔結(jié)構(gòu)。

在核芯結(jié)構(gòu)中,PCB板中的所有導(dǎo)電層敷在核芯材料上;而在敷箔結(jié)構(gòu)中,只有PCB板內(nèi)部導(dǎo)電層才敷在核芯材料上,外導(dǎo)電層用敷箔介質(zhì)板。所有的導(dǎo)電層通過介質(zhì)利用多層層壓工藝粘合在一起。

核材料就是工廠中的雙面敷箔板。因為每個核有兩個面,全面利用時,PCB板的導(dǎo)電層數(shù)為偶數(shù)。為什么不在一邊用敷箔而其余用核結(jié)構(gòu)呢?其主要原因是:PCB板的成本及PCB板的彎曲度。

偶數(shù)層PCB板的成本優(yōu)勢

因為少一層介質(zhì)和敷箔,奇數(shù)PCB板原材料的成本略低于偶數(shù)層PCB。但是奇數(shù)層PCB板的加工成本明顯高于偶數(shù)層PCB板。內(nèi)層的加工成本相同;但敷箔/核結(jié)構(gòu)明顯的增加外層的處理成本。

奇數(shù)層PCB板需要在核結(jié)構(gòu)工藝的基礎(chǔ)上增加非標(biāo)準(zhǔn)的層疊核層粘合工藝。與核結(jié)構(gòu)相比,在核結(jié)構(gòu)外添加敷箔的工廠生產(chǎn)效率將下降。在層壓粘合以前,外面的核需要附加的工藝處理,這增加了外層被劃傷和蝕刻錯誤的風(fēng)險。

平衡結(jié)構(gòu)避免彎曲

不用奇數(shù)層 設(shè)計PCB板的最好的理由是:奇數(shù)層PCB板容易彎曲。當(dāng)PCB板在多層電路粘合工藝后冷卻時,核結(jié)構(gòu)和敷箔結(jié)構(gòu)冷卻時不同的層壓張力會引起PCB板彎曲。隨著電路板厚度的增加,具有兩個不同結(jié)構(gòu)的復(fù)合PCB板彎曲的風(fēng)險就越大。消除PCB板彎曲的關(guān)鍵是采用平衡的層疊。盡管一定程度彎曲的PCB板達(dá)到規(guī)范要求,但后續(xù)處理效率將降低,導(dǎo)致成本增加。因為裝配時需要特別的設(shè)備和工藝,元器件放置準(zhǔn)確度降低,故將損害質(zhì)量。

使用偶數(shù)層PCB板

當(dāng)設(shè)計中出現(xiàn)奇數(shù)層PCB板時,用以下幾種方法可以達(dá)到平衡層疊、降低PCB板制作成本、避免PCB板彎曲。以下幾種方法按優(yōu)選級排列。

1、一層信號層并利用。如果設(shè)計PCB板的電源層為偶數(shù)而信號層為奇數(shù)可采用這種方法。增加的層不增加成本,但卻可以縮短交貨時間、改善PCB板質(zhì)量。

2、增加一附加電源層。如果設(shè)計PCB板的電源層為奇數(shù)而信號層為偶數(shù)可采用這種方法。一個簡單的方法是在不改變其他設(shè)置的情況下在層疊中間加一地層。先按奇數(shù)層PCB板布線,再在中間復(fù)制地層,標(biāo)記剩余的層。這和加厚地層的敷箔的電氣特性一樣。

3、在接近PCB層疊中央添加一空白信號層。這種方法最小化層疊不平衡性,改善PCB板的質(zhì)量。先按奇數(shù)層布線,再添加一層空白信號層,標(biāo)記其余層。在微波電路和混合介質(zhì)(介質(zhì)有不同介電常數(shù))電路中采用。

平衡層疊PCB優(yōu)點:成本低、不易彎曲、縮短交貨時間、保證質(zhì)量。

-

電路板

+關(guān)注

關(guān)注

140文章

5058瀏覽量

100665 -

介質(zhì)

+關(guān)注

關(guān)注

0文章

142瀏覽量

18731 -

PCB層疊

+關(guān)注

關(guān)注

0文章

5瀏覽量

1317

發(fā)布評論請先 登錄

相關(guān)推薦

不可忽視!四層PCB打樣設(shè)計中的關(guān)鍵細(xì)節(jié)大盤點!

平衡電阻器可以改為不平衡嗎

PCB 設(shè)計規(guī)則、層疊結(jié)構(gòu)的導(dǎo)入/導(dǎo)出

動平衡校正和振動測量有關(guān)嗎?

0.4mm層疊封裝(PoP)封裝的PCB組裝指南,第二部分

0.5mm層疊封裝應(yīng)用處理器的PCB設(shè)計指南,第一部分

0.5mm層疊封裝應(yīng)用處理器的PCB組裝指南,第II部分

平衡閥正確安裝使用方法介紹

0.4毫米層疊封裝(PoP)的PCB設(shè)計指南,第一部分

電橋平衡的應(yīng)用、類型及測量方法

秘密背后的秘密-高速PCB的層疊確認(rèn)時,工廠為何不寫銅箔類型

秘密背后的秘密-高速PCB的層疊確認(rèn)時,工廠為何不寫銅箔類型

PMP30826.1-具有有源電池平衡功能的超級電容備用電源 PCB layout 設(shè)計

關(guān)于平衡PCB層疊設(shè)計方法介紹

關(guān)于平衡PCB層疊設(shè)計方法介紹

評論