為提高帶寬,很多類型的 Memory 都采用了 Double Data Rate(DDR)interface,它對在內(nèi)存控制器(memory controller)設(shè)計(jì)過程中的時(shí)序收斂和后仿真提出了挑戰(zhàn)。

1 引言

Double Data Rate (DDR) 接口在 ASIC 領(lǐng)域應(yīng)用得很廣,尤其在 Memory 領(lǐng)域,從 DDR SDRAM 誕生后 Memory 經(jīng)歷了 DDR2,DDR3 乃至現(xiàn)在主流的 DDR4,它們在數(shù)據(jù)接口上都使用的 Double Data Rate(DDR)interface[1-4]。DDR interface 是一種源同步接口,時(shí)鐘(DQS)和數(shù)據(jù)(DQ)都由發(fā)送方提供。讀操作時(shí) Memory 提供時(shí)鐘和讀數(shù)據(jù),Memory 僅在有數(shù)據(jù)的時(shí)間段內(nèi)驅(qū)動(dòng)時(shí)鐘(DQS),時(shí)鐘和數(shù)據(jù)是沿對齊(edge alignment),內(nèi)存控制器(Memory controller)使用收到的時(shí)鐘(DQS)的上下沿采樣數(shù)據(jù)。寫操作時(shí)內(nèi)存控制器提供時(shí)鐘和寫數(shù)據(jù)且僅在有數(shù)據(jù)的時(shí)間段內(nèi)驅(qū)動(dòng)時(shí)鐘(DQS),時(shí)鐘和數(shù)據(jù)是中間對齊(center alignment),內(nèi)存(Memory)也使用時(shí)鐘的上下沿采樣數(shù)據(jù)。基于這樣的協(xié)議,通常讀操作時(shí)內(nèi)存控制器使用延長線延遲輸入的 DQS, 以滿足足夠的建立保持時(shí)間采樣讀數(shù)據(jù)。而寫操作時(shí),內(nèi)存控制器需要將輸出的 DQS 做一定延遲以使內(nèi)存有足夠的建立保持時(shí)間采樣寫數(shù)據(jù)。因?yàn)槭菚r(shí)鐘上下沿都需要采樣數(shù)據(jù),隨著 Memory 時(shí)鐘頻率的加快,對時(shí)序收斂和后仿真都提出了挑戰(zhàn)。

本文介紹了一種通過靜態(tài)時(shí)序分析工具進(jìn)行時(shí)序檢查及指導(dǎo)后仿真工作的方法。

2 DDR Memory 讀接口

根據(jù) JEDEC Spec,DDR Memory 讀的時(shí)序如圖 1。

DQS 上升沿的參數(shù):① tDQSQ 是最晚有效數(shù)據(jù)的翻轉(zhuǎn),它反映著 DQ 的偏移(Skew)。② tDH是最早無效數(shù)據(jù)的開始,它反映著 DQ 的有效寬度。

DQS 下降沿的參數(shù):① tDQSQ 是最晚有效數(shù)據(jù)的翻轉(zhuǎn),它反映著 DQ 的偏移(Skew)。② tDH 是最早無效數(shù)據(jù)的開始,它反映著DQ的有效寬度。

讀操作時(shí) Memory 提供時(shí)鐘和讀數(shù)據(jù),Memory僅在有數(shù)據(jù)的時(shí)間段內(nèi)驅(qū)動(dòng)時(shí)鐘(DQS),時(shí)鐘和數(shù)據(jù)是沿對齊,內(nèi)存控制器(Memory controller)使用收到的時(shí)鐘(DQS)的上下沿采樣數(shù)據(jù)。鑒于DDR Memory 這個(gè)特性(上下沿都會(huì)發(fā)送數(shù)據(jù)),內(nèi)存控制器一般會(huì)使用延長線去延遲輸入的 DQS 然后再去采樣數(shù)據(jù)的電路,其結(jié)構(gòu)可如圖 2。

根據(jù)電路結(jié)構(gòu),它的時(shí)序約束可以如下設(shè)置(以 DDR3-1600 為例)。

使用 create_clock 和 create_generated_clock 定義了 Memory 產(chǎn)生的 dqs 經(jīng)過延遲線延遲后到達(dá) i_rdata_r/f 的 clock。

因?yàn)?Memory 既在上升沿發(fā)送數(shù)據(jù)又在下降沿發(fā)送數(shù)據(jù),所以需要使用下面兩條命令來約束輸入數(shù)據(jù)的建立時(shí)間(setup time)的要求。

根據(jù)時(shí)序要求還需要設(shè)置輸入數(shù)據(jù)的保持時(shí)間(hold time)的要求如下。

“set_multicycle_path 0”反映著圖 2 電路的工作機(jī)制,i_data_r/f 的采樣時(shí)鐘是經(jīng)過 delay chain 延遲后的 clock,理論上的建立時(shí)間不是通常時(shí)序電路中的一個(gè)周期,所以設(shè)為 multicycle_path=0。

根據(jù)上面的時(shí)序約束可以在靜態(tài)時(shí)序工具中得到如下的時(shí)序報(bào)告。pd 到 i_rdata_r 的建立時(shí)間(setup time) 報(bào)告如下。

從上面報(bào)告看到輸入數(shù)據(jù)被發(fā)送的時(shí)間從 0 ns 開始計(jì)算,而被采樣的時(shí)間也為 0 ns 開始計(jì)算,這恰好是符合 i_rdata_r 采樣的時(shí)鐘是來自延遲后的 DQS 的上升沿,隨著延遲線延遲的增大,i_rdata_r 的建立時(shí)間的余量會(huì)越來越大。

pd 到 i_rdata_r 的保持時(shí)間(hold time)的報(bào)告如下。

從上面報(bào)告看到新數(shù)據(jù)被發(fā)送的時(shí)間從 0.62 ns 開始計(jì)算并且上一筆數(shù)據(jù)被采樣的時(shí)間也從 0 ns 開始計(jì)算,這也符合電路工作實(shí)際情況。延遲線延遲最小時(shí) i_rdata_r 的保持時(shí)間的余量最大,隨著延遲線延遲的增大,保持時(shí)間的余量會(huì)越來越小(表 1)。

上面的時(shí)序報(bào)告描述了 i_rdata_r 的時(shí)序情況,i_data_f 的時(shí)序報(bào)告類似,只是 launch/capture 的時(shí)間不同而已,在此不再贅述。

根據(jù)上面的分析說明時(shí)序報(bào)告符合電路工作預(yù)期,所以時(shí)序約束是正確的。但在實(shí)際時(shí)序收斂時(shí)還不能像一般芯片內(nèi)部的數(shù)字電路那樣簡單地根據(jù)設(shè)定的時(shí)鐘和 IO 約束進(jìn)行時(shí)序收斂,理由如下。

圖 3 是芯片內(nèi)部一般數(shù)字電路的基本結(jié)構(gòu),它的時(shí)序關(guān)系如圖 4 所示。

flop1/CP 在 edge 2 發(fā)送新的數(shù)據(jù),flop2 會(huì)在 edge3 采樣這筆數(shù)據(jù),這是它們之間的建立時(shí)間(setup time)的檢查。同樣 flop1/CP 的 edge 4 也可能發(fā)送新的數(shù)據(jù),這些數(shù)據(jù)不能被 flop2/CP 的 edge4 采樣到,這個(gè)時(shí)序檢查就是保持時(shí)間(hold time)的檢查。基于這樣工作模式和靜態(tài)時(shí)序檢查方法,EDA 工具能夠比較容易根據(jù)時(shí)鐘頻率的要求和電路自身的快慢自動(dòng)地滿足上述電路的時(shí)序要求。例如當(dāng)建立時(shí)間不滿足時(shí) EDA 工具可以通過縮短flop1/Q->flop2/D 路徑的延遲或者利用 flop1/CP 和flop2/CP的skew 做到,但這些都不太適合 DDR Memory interface。因?yàn)閳D 2 中 i_rdata_r/f 的時(shí)鐘是經(jīng)過延遲線的,而這個(gè)延遲可能需要根據(jù)外接 Memory 的不同、工作頻率的不同甚至工作電壓及溫度的不同進(jìn)行調(diào)節(jié)以滿足 i_rdata_r/i_rdata_f 數(shù)據(jù)端的建立保持時(shí)間的要求,這樣才能夠正確接收數(shù)據(jù)。因此在時(shí)序收斂過程中時(shí)無法按照確定的延遲線延遲進(jìn)行時(shí)序收斂,如果固定延遲進(jìn)行時(shí)序收斂有可能會(huì)導(dǎo)致延遲線可用工作范圍變小。事實(shí)上,圖 2 電路的時(shí)序收斂通常做法就是使 pd 到 i_rdata_r/f/D 的延遲和 dqs 到 i_rdata_r/CP 和 i_rdata_f/CP 的延遲盡量相等,這樣才能保證將來做延遲線調(diào)節(jié)時(shí)有足夠的調(diào)節(jié)范圍,但這樣做法可能導(dǎo)致在自動(dòng)布局布線完成后 i_rdata_r或i_rdata_f 的數(shù)據(jù)端的建立/保持時(shí)間不是一直能夠得到滿足的,從而導(dǎo)致在后仿真時(shí)有可能遇到時(shí)序違例,造成后仿真失敗,這種情況在 DDR Memory interface 是多 bit 時(shí),由于不同 bit 之間的延遲偏差會(huì)更嚴(yán)重,給后仿真帶來困難,因?yàn)榉抡婀こ處熜枰业揭粋€(gè)合理的延遲線設(shè)置同時(shí)滿足不同 bit 和上下沿的建立保持時(shí)間的要求。而且,它隨著 DDR 速度的增加還會(huì)惡化。事實(shí)上基于前面的時(shí)序約束,通過腳本改變延長線的延遲設(shè)置然后做時(shí)序分析,可以很方便地利用靜態(tài)時(shí)序工具獲得后仿真時(shí)所需的延遲線的設(shè)置以滿足所有 bits 及上下沿的時(shí)序要求。這樣的方法也可以幫助我們分析讀路徑中實(shí)際可用的延遲線工作范圍,從而指導(dǎo)時(shí)序收斂過程。如當(dāng)自動(dòng)布局布線工具 APR 時(shí)由于某種原因?qū)е?dqs 到 i_rdata_r/CP 或 _rdata_f/CP 的延遲比 pd 到 i_rdata_r/D 或 i_rdata_f/D 的延遲偏大時(shí),這會(huì)導(dǎo)致延遲線可調(diào)范圍變小。設(shè)計(jì)者可以使用上述方法發(fā)現(xiàn)這樣的問題。

通過靜態(tài)時(shí)序工具可以得到上述方法的結(jié)果(表 1),它反映了隨著延遲線的調(diào)整 i_rdata_r/f 的建立保持時(shí)間滿足的情況,正值表示相應(yīng)的時(shí)序是滿足的,負(fù)值說明相應(yīng)的時(shí)序是不滿足的。可用的延遲線的設(shè)置是 i_rdata_r和i_rdata_f 的建立(setup)和保持(hold)時(shí)間都是正值。比較后得到 step=1~7 都是可以使用的延遲線設(shè)置,它們的中點(diǎn)大約為 step=4,這個(gè)值可以用來做 post-SDF 仿真。

因此上文中的 DDR Memory interface 的時(shí)序設(shè)置及后續(xù)時(shí)序檢查方法可以很好地檢查 DDR 讀接口的時(shí)序滿足情況并可以很方便地找到可用的后仿真設(shè)置,極大地提高了工作效率。

3 DDR Memory 寫接口

類似 DDR Memory 讀接口,JEDEC Spec 的 DDR Memory 寫時(shí)序如圖 5 所示。① tDQSH:Write DQS 高電平的寬度;② tDQSL:Write DQS 低電平的寬度;③ tDS:寫數(shù)據(jù)的建立時(shí)間;④ tDH:寫數(shù)據(jù)的保持時(shí)間。

寫操作時(shí)內(nèi)存控制器提供時(shí)鐘和寫數(shù)據(jù)且僅在有數(shù)據(jù)的時(shí)間段內(nèi)驅(qū)動(dòng)時(shí)鐘(DQS),時(shí)鐘和數(shù)據(jù)在內(nèi)存的輸入需要滿足中間對齊(center alignment),這樣內(nèi)存端(Memory)就可以使用時(shí)鐘(DQS)的上下沿采樣數(shù)據(jù)。圖 6 寫電路工作時(shí)序如圖 7 所示,i_wdata_r/f 的數(shù)據(jù)經(jīng)過 MUX 選擇后就會(huì)變成一個(gè)上下沿都翻轉(zhuǎn)的數(shù)據(jù),而 dqs 經(jīng)過延遲線后可以和寫數(shù)據(jù)達(dá)到中間對齊(center alignment), 從而滿足 DDR Memory 對寫數(shù)據(jù)的建立保持時(shí)間的要求。

根據(jù)圖 5、圖 6、圖 7 寫電路的時(shí)序約束可以添加圖 7 中寫數(shù)據(jù)和 DQS 間關(guān)系。對應(yīng)在靜態(tài)時(shí)序工具中可以得到時(shí)序報(bào)告。

綜上,基于前述的 DDR Memory 寫路徑時(shí)序約束的靜態(tài)時(shí)序報(bào)告和電路預(yù)期的工作模式是一致的,但和讀電路類似,為了保證 write DQS 有足夠的可調(diào)范圍,寫電路時(shí)序收斂時(shí)一般也只是盡量將數(shù)據(jù)和時(shí)鐘的 path 做 balance, 而不能基于某個(gè)延遲線的設(shè)置或某個(gè)頻率做簡單地修 timing 的工作,并且 Memory不同工作頻率下對于輸入數(shù)據(jù)的建立保持時(shí)間的要求也不同,也不易按照一個(gè)固定的標(biāo)準(zhǔn)做時(shí)序收斂。這樣有可能導(dǎo)致像讀電路一樣后仿真時(shí)需要調(diào)節(jié)寫時(shí)鐘延遲線的設(shè)置以滿足寫數(shù)據(jù)的建立/保持時(shí)間的要求。同樣在多 Memory bit 的設(shè)計(jì)情況時(shí)這樣工作也會(huì)隨著頻率的提高越來越不易,因此類似讀操作時(shí)的做法,這項(xiàng)工作也可以通過腳本改變延遲線的設(shè)置,在靜態(tài)時(shí)序工具里完成。

4 結(jié)語

本文介紹靜態(tài)時(shí)序工具在 DDR Memory interface 的時(shí)序分析,以及其在后仿真中的應(yīng)用。從實(shí)踐角度彌補(bǔ)了 DDR Memory interface 時(shí)序收斂目標(biāo)和后仿真目標(biāo)之間的差異,可以在滿足時(shí)序收斂目標(biāo)的前提的情況下給設(shè)計(jì)者提供一種快速找到合適的后仿真設(shè)置的方法。

-

仿真

+關(guān)注

關(guān)注

51文章

4206瀏覽量

135033 -

時(shí)序

+關(guān)注

關(guān)注

5文章

395瀏覽量

37710

原文標(biāo)題:靜態(tài)時(shí)序工具在 DDR Memory 接口時(shí)序收斂和后仿真中的應(yīng)用

文章出處:【微信號(hào):appic-cn,微信公眾號(hào):集成電路應(yīng)用雜志】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評(píng)論請先 登錄

相關(guān)推薦

FPGA時(shí)序約束之設(shè)置時(shí)鐘組

集成電路設(shè)計(jì)中靜態(tài)時(shí)序分析介紹

ADC的靜態(tài)指標(biāo)有專用的分析工具嗎?

固定帶寬與動(dòng)態(tài)帶寬的區(qū)別

ipc系統(tǒng)的網(wǎng)絡(luò)帶寬需求分析

海外靜態(tài)IP:跨國業(yè)務(wù)與遠(yuǎn)程工作的重要工具

TPS65950實(shí)時(shí)時(shí)鐘時(shí)序補(bǔ)償分析

使用IBIS模型進(jìn)行時(shí)序分析

利用關(guān)斷保護(hù)信號(hào)開關(guān)消除電源時(shí)序

利用靜態(tài)檢查工具完善功能安全中測試覆蓋率

時(shí)序邏輯電路故障分析

IAR通過多架構(gòu)認(rèn)證的靜態(tài)分析工具加速代碼質(zhì)量自動(dòng)化

FPGA 高級(jí)設(shè)計(jì):時(shí)序分析和收斂

AnyWay功率分析儀帶寬是否越寬越好?

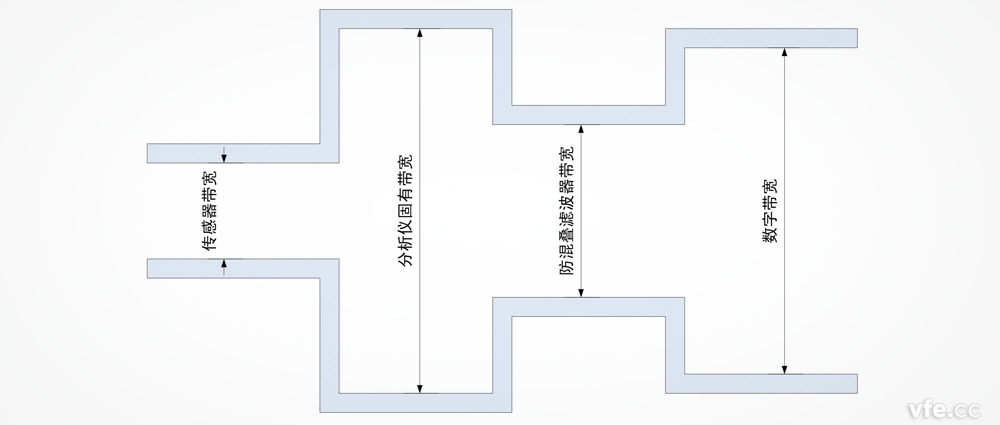

利用靜態(tài)時(shí)序分析工具解決帶寬不足問題

利用靜態(tài)時(shí)序分析工具解決帶寬不足問題

評(píng)論