由于集成了多核,密集時鐘樹,增加的AMS(模擬和混合信號),復雜的功率和功能,汽車SoC在設計上變得越來越復雜。復位管理,創新的ADAS/動力總成子系統,各種接口和其他高度可配置的模塊。在整個開發周期中,在IP/SoC級別上執行各種事前硅測試場景,目的是揭示設備中的系統級集成問題。這些觀察結果將導致某些設計/文檔更改,從而產生更強大的客戶解決方案。

但是,當某些序列和事件組合在設備上發生時,可能仍會遇到一些極端情況問題從未在設備測試中進行過操作。以便及早發現系統級問題:

時鐘同步問題

實現有限狀態的回歸機器(FSM)

嚴格的低功耗模式進入/退出

主從互連(交叉開關)周圍的性能方面

非法寄存器訪問時的系統行為

現在讓我們逐一討論這些領域中的每一個,并說明壓力測試中發現的問題。

時鐘同步問題

密集時鐘樹在SoC中實現,具有許多可配置的時鐘源,用于驅動內核和外設。此外,這些時鐘源具有相關的分頻器以允許進一步的可配置性。大多數情況下,由于資源/時間/計算限制,系統和外設時鐘之間的所有可能的時鐘同步問題都無法被驗證工具捕獲。這種即興變成了后硅驗證過程中關注的重要領域。

驗證工程師應在其代碼中實現隨機化,以便在外設和內核進行通信時改變時鐘源和分頻器。這可以幫助捕獲一些組合,其中交叉條和外設時鐘的不同時鐘頻率導致功能故障,然后可以正確記錄/實施以避免客戶應用程序中出現問題。

對已實施的FSM進行回歸

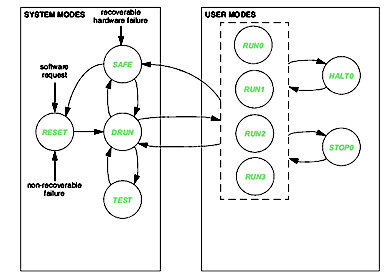

必須徹底驗證每個在內部實施FSM的模塊(參見圖1),以確保所有模塊的正確狀態轉換。所需的事件并確保不僅系統不會因所有有效模式狀態轉換而出現故障,而且系統應該能夠為所有無效模式轉換正確恢復。

圖1,在SoC中的1 FSM實現

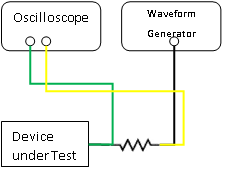

在后硅片期間覆蓋這些轉換更具挑戰性。復位生成模塊是一個關鍵模塊,它控制來自各種源/事件的復位斷言的系統行為。必須在RGM上開發驗證測試,以觀察外部復位信號在器件上的周期性斷言的影響,以及器件是否每次使用不同的配置都能完全復位。 RGM驗證設置的簡化說明如下所示:

圖。 2 RGM壓力驗證設置

此類練習可能有助于捕捉RGM的外部復位捕獲和邊沿檢測電路之間可能的競爭條件,這可能導致設備卡在復位狀態。

類似地,隨機驗證將設備從一種操作模式切換到另一種具有不同外圍狀態的操作模式可以捕獲某些災難性問題。例如,如果在目標模式下未啟用PLL的時鐘源,則嘗試切換到需要外圍設備的PLL時鐘的目標模式將失敗。時鐘源依賴性只是導致模式轉換失敗的因素之一。

嚴格的低功耗模式進入/退出

設備從低功耗模式成功進入和退出是另一個重要的設計方面,需要對各種系統參數進行全面檢查,如狀態外圍設備,閃光燈,低功率時備用ram。如果閃光燈在低功率狀態期間處于睡眠/正常狀態,則從低功率模式喚醒時間總是在規格中,而在閃光燈配置為斷電時可能不在規格范圍內。對喚醒中斷的廣泛檢查甚至可以找到可能導致設備不退出低功耗模式的所有設備配置。低功耗模式下的當前數字是此類測試中的另一個關注領域。

橫梁周圍的性能方面

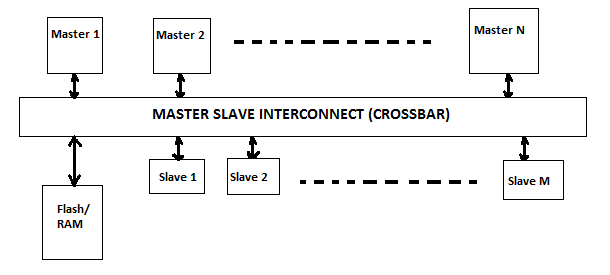

Master-從互連是任何SoC的重要組成部分,它仲裁多個主設備到多個從設備的通信,并通過控制優先級來控制執行流程。下圖顯示了一個高度簡化的橫桿版本。

圖3.主從互連的簡化圖

SoC的系統性能是高度依賴于Crossbar實施。此處的任何限制都會嚴重影響客戶的應用程序。在后硅驗證期間,應測試不同主設備的各種優先級配置方案,以確保發現交叉開關限制。在多個主設備同時訪問來自相同或不同系統存儲器組的指令和數據的情況下,可能存在主要饑餓的情況。

非法寄存器訪問時的系統行為

通常,設備文檔指出,如果在系統級別啟用,則對保留/未實現位置的訪問可能會生成總線錯誤并導致異常。但是,訪問保留位置的隨機驗證可能會發現系統行為,這可能會有很大不同,并可能導致設備掛起。某些保留位置可能不會產生總線錯誤,因為IP設計人員可能不認為存儲器孔是保留的。某些位置可能會生成異常,即使沒有在系統級別啟用它們。無論這些非統一的系統行為是什么,都需要對其進行適當的記錄,以便客戶在其應用程序中具有正確的實現來處理所有行為。了解此類行為也可用于在未來的IP/SoC設計中實現統一的系統行為。

-

soc

+關注

關注

38文章

4356瀏覽量

221835 -

PCB打樣

+關注

關注

17文章

2977瀏覽量

22380 -

華強PCB

+關注

關注

8文章

1831瀏覽量

28460 -

華強pcb線路板打樣

+關注

關注

5文章

14629瀏覽量

43765

發布評論請先 登錄

電池的使用在各個領域

寶馬慕尼黑工廠正在使用人工智能應用來對工廠的各個領域進行測試

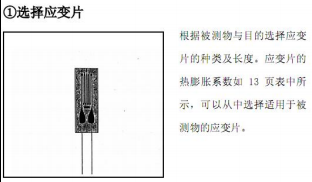

PCB板應力應該如何測試

PCB應力測試儀

離線語音識別模塊深入到各個領域當中

發送模塊在各個領域的應用

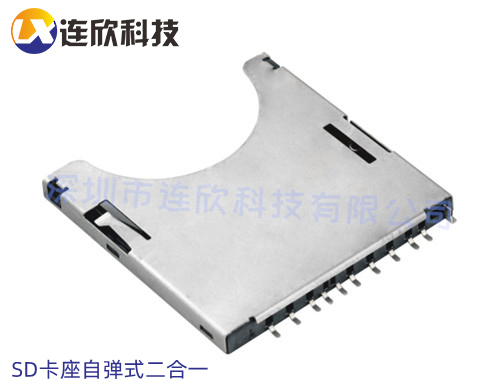

SD卡座自彈式在各個領域的使用特點

汽車SoC上硅后應力測試的各個領域知識解析

汽車SoC上硅后應力測試的各個領域知識解析

評論