在FPGA設計中,PLL(鎖相環)模塊作為核心時鐘管理單元,通過靈活的倍頻、分頻和相位調整功能,為系統提供多路高精度時鐘信號。它不僅解決了時序同步問題,還能有效消除時鐘偏移,提升系統穩定性。本文將深入探討智多晶PLL在實際應用中的關鍵注意事項,幫助工程師規避常見設計風險。

01PLL動態相位調整

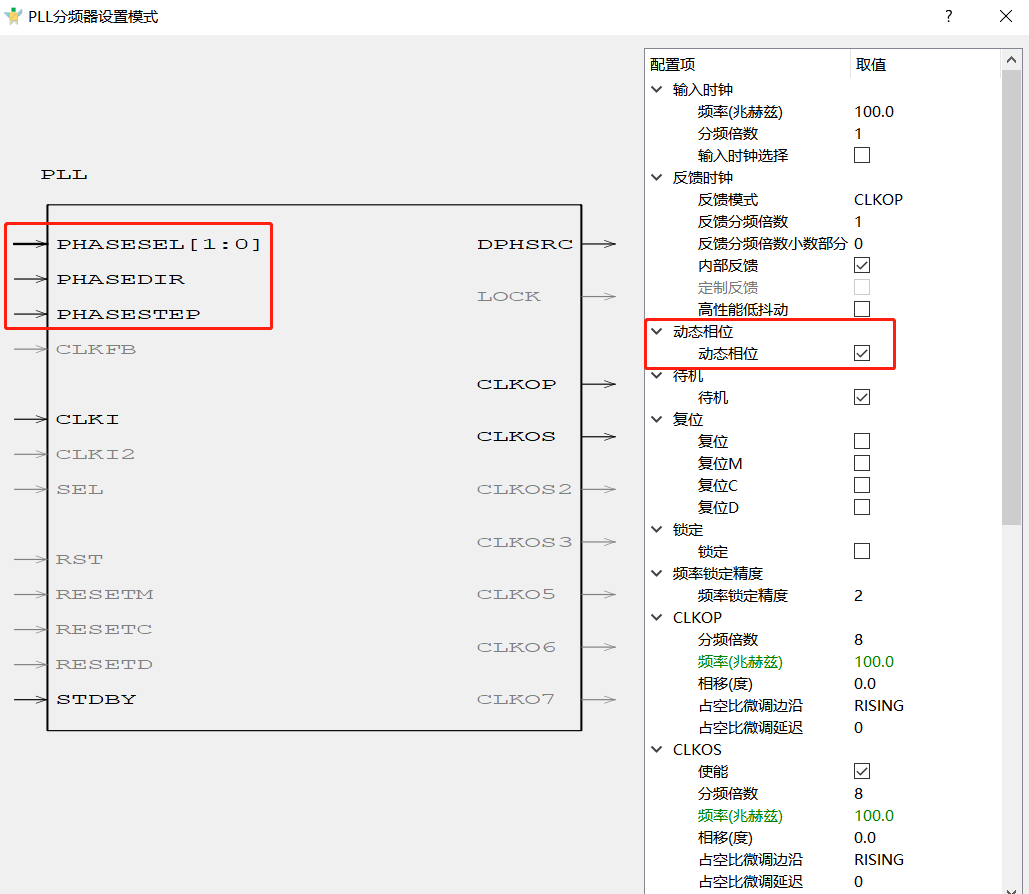

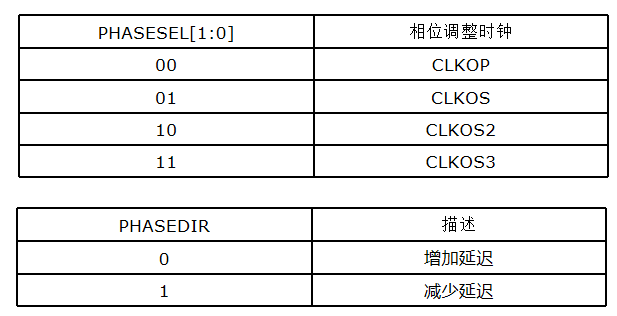

PLL模塊支持對輸出時鐘的相位進行調整,CLKOP、CLKOS、CLKOS2、CLKOS3四組時鐘信號都支持動態相位調整,但是同一時刻只有一個支持該功能。

當PHASESEL、PHASEDIR明確后,PHASESTEP信號每產生一次脈沖信號相位將調整1/(8*FVCO),需要注意智多晶不同型號的FVCO范圍存在差別,使用中請參考對應型號的數據手冊。

02Sealion系列 PLL相位調整

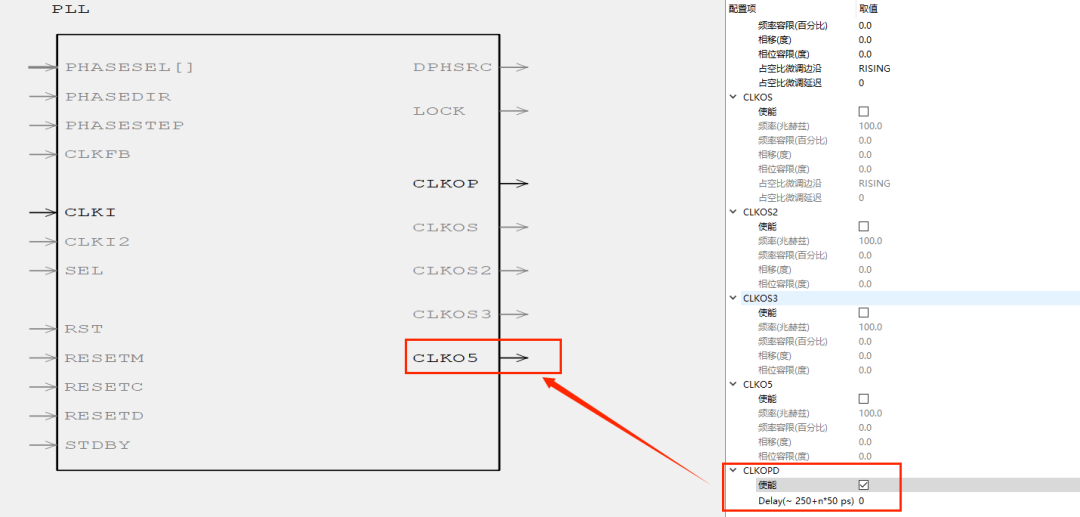

Sealion系列PLL支持CLKOPD單路時鐘延遲,該延遲參考對象為CLKOP,延遲時鐘從CLKO5端口輸出。固定延遲1step對應50ps(±20%)。

CLKO5和CLKOPD均使用CLK05端口輸出時鐘,使用該功能是需要注意CLKO5和CLKOPD不能同時開啟,同時開啟時PLL IP將發出錯誤提示。

03PLL頻率輸出計算

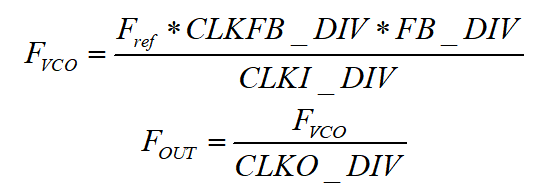

智多晶提供的PLL內有三種分頻器,分別為輸入、輸出和反饋。輸入分頻減小輸入頻率后送到PLL比較器。反饋分頻基本為一乘法器,PLL 電壓控制振蕩器 (VCO) 的輸出通過反饋分頻器減小其頻率與另一輸入頻率比較,輸出分頻器控制最終輸出頻率。

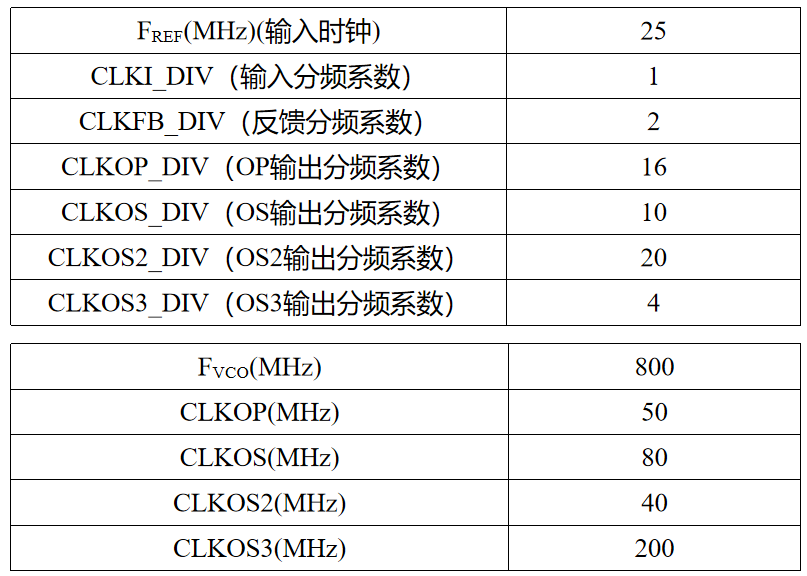

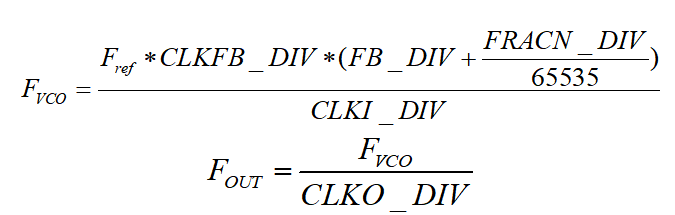

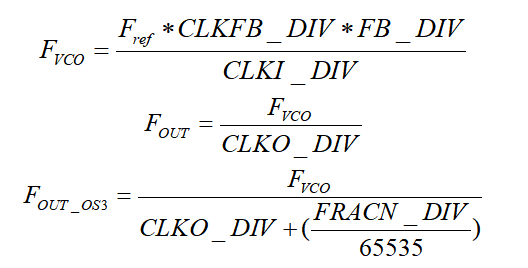

輸出頻率計算如下:

上式中,反饋通道的分頻系數由CLKFB_DIV及FB_DIV兩部分組成,2個系數的乘積作為最終的反饋系數。如果選擇OP作為反饋回路,則FB_DIV設置為OP通道的分頻系數CLKOP_DIV。

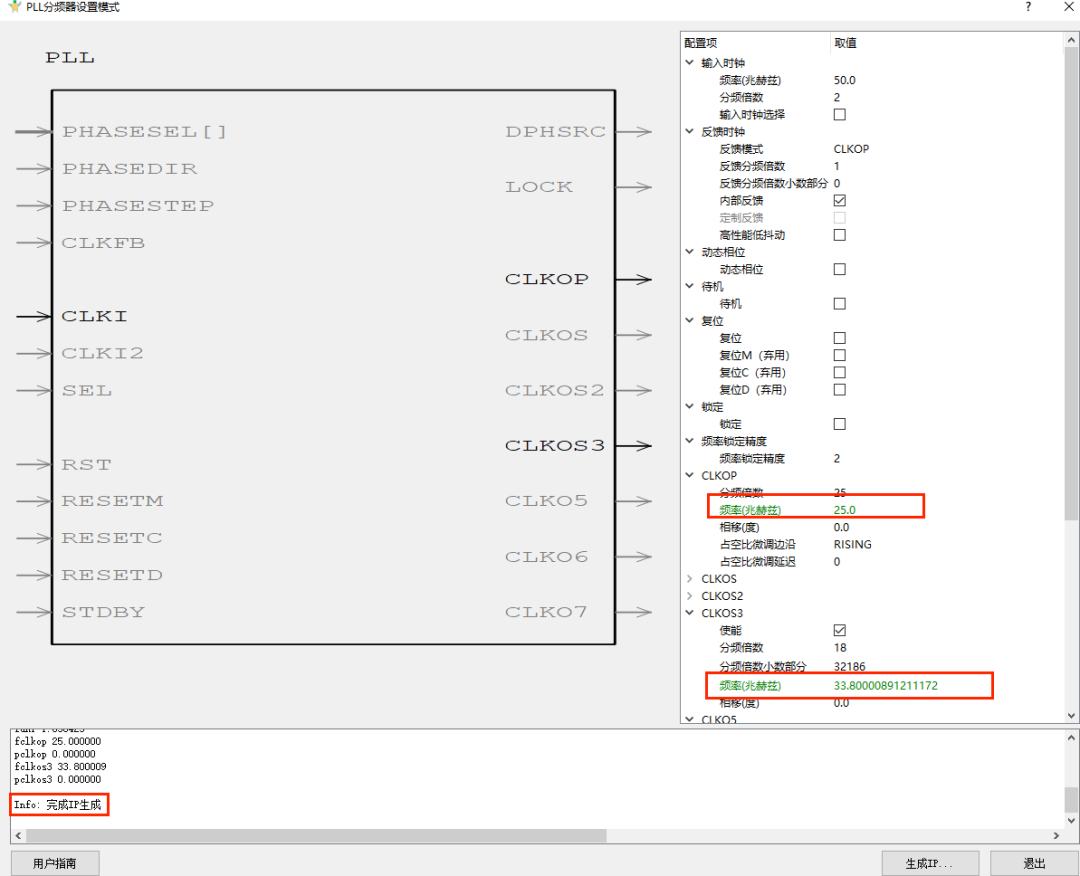

04PLL頻率輸出小數頻率

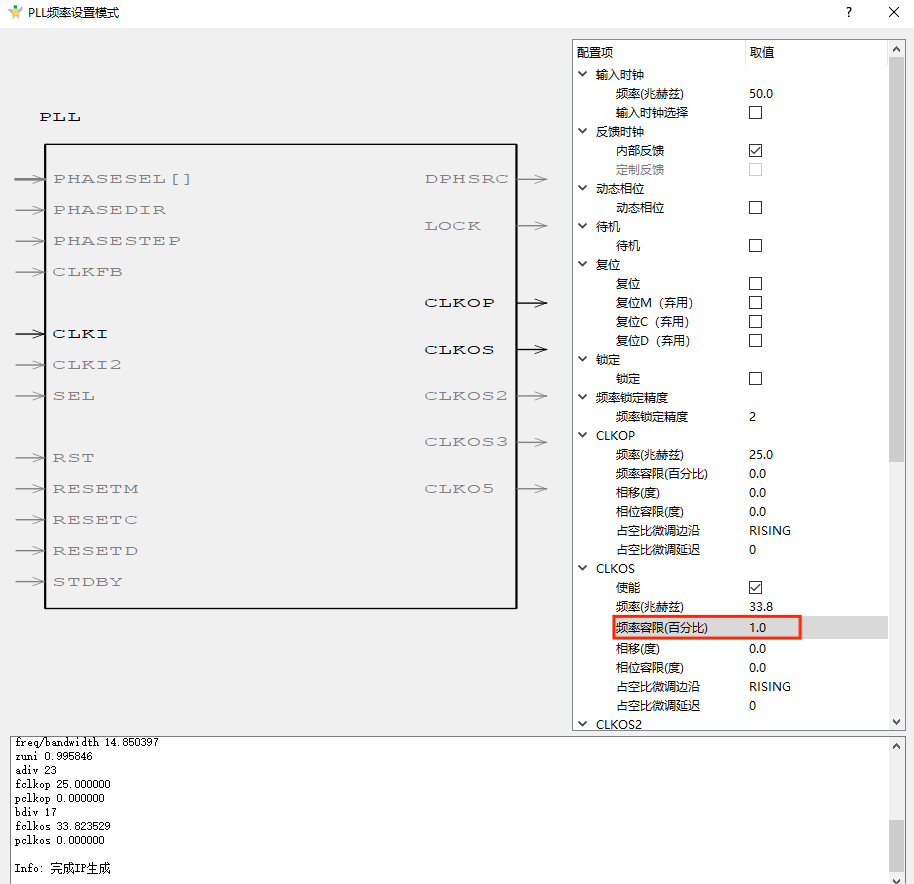

PLL生成特殊的小數頻率將無法生成,此時可以通過調整頻率容限(百分比)的方式生成頻率,此時輸出頻率與目標頻率將會存在一定誤差。例如,使用PLL的CLKOS端直接生成33.8MHz的頻率無法生成,修改整頻率容限(百分比)為1,再次生成,此時可以生成頻率,生成頻率為33.823529MHz。

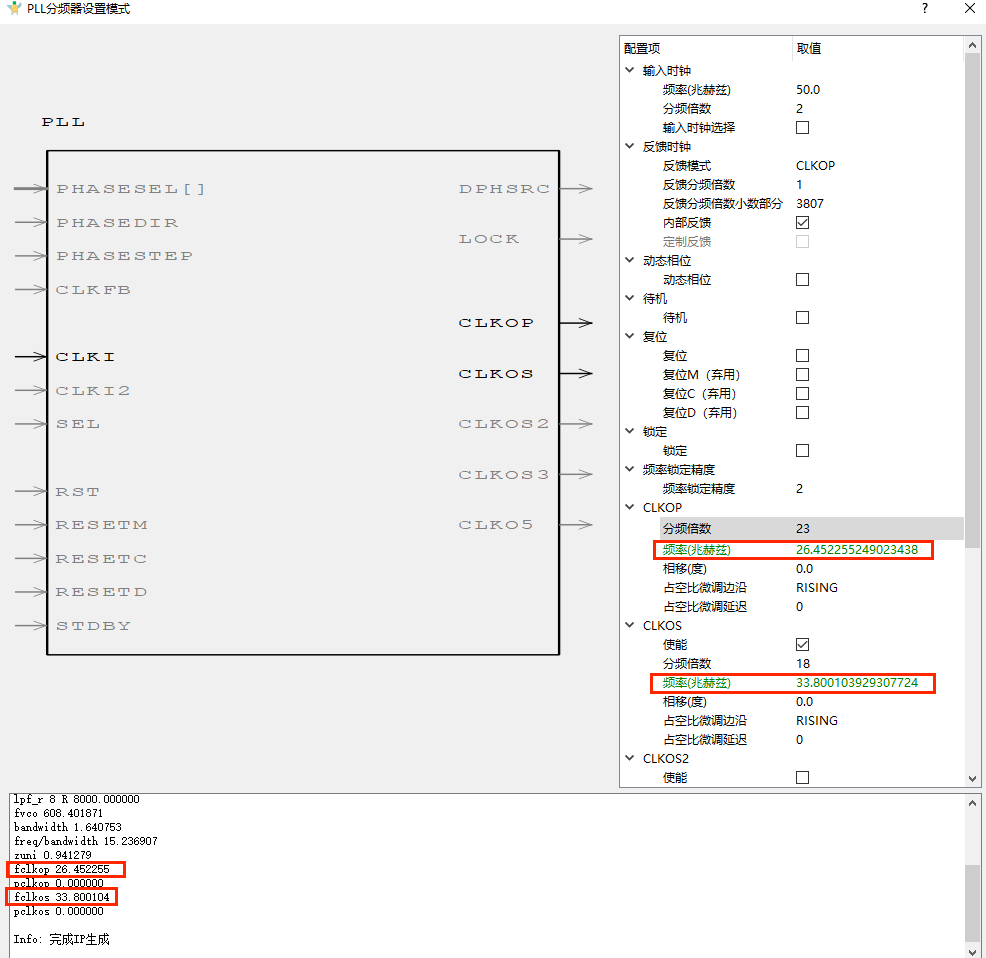

05多通道PLL小數分頻

FPGA的PLL可以對輸入時鐘進行小數分頻,分為多通道PLL小數分頻和指定通道PLL小數分頻。

(1)多通道PLL小數分頻

當用戶選擇多通道PLL小數分頻時,PLL所有7路輸出時鐘均為小數分頻。此時,PLL輸出時鐘頻率和參考時鐘頻率之間的關系如下:

上式中FRACN_DIV為精準分頻參數,16bit,取值范圍0-65535。FRACN_DIV會導致FVCO改變,所以PLL的所有輸出時鐘頻率都會改變。

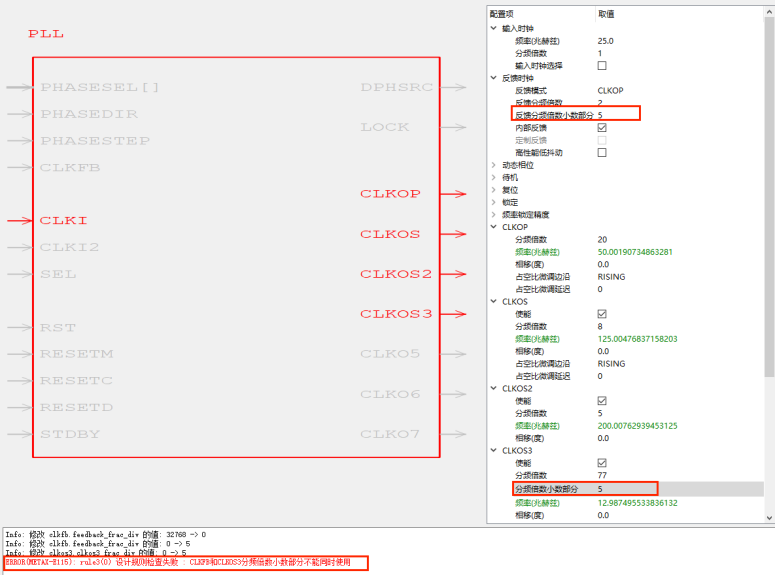

(2)指定通道PLL小數分頻

當用戶選擇指定通道PLL小數分頻模式時,只有CLKOS3單路輸出為小數分頻,其他6路輸出通路為整數分頻。此時,反饋支路時鐘不能選擇CLKOS3,PLL 輸出時鐘頻率和參考時鐘頻率之間的關系如下:

CLKOS3輸出頻率通過FOUT_OS3進行計算,其他通道通過式FOUT進行計算。該方式僅對CLKOS3輸出頻率進行改變,其他端口不改變。

需要注意,單通道PLL小數分頻和多通道PLL小數分頻兩種方式不能同時使用,同時使用時,IP將會輸出錯誤信息。

06總結

通過融合理論規范與實戰經驗,工程師可系統性規避PLL設計風險,充分發揮智多晶器件的高精度時鐘管理能力。

-

FPGA

+關注

關注

1643文章

21983瀏覽量

614977 -

鎖相環

+關注

關注

35文章

596瀏覽量

88517 -

pll

+關注

關注

6文章

887瀏覽量

136142 -

時鐘信號

+關注

關注

4文章

466瀏覽量

29115

原文標題:“芯”技術分享|智多晶PLL使用注意事項

文章出處:【微信號:智多晶,微信公眾號:智多晶】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

智多晶PLL使用注意事項

智多晶PLL使用注意事項

評論