完善資料讓更多小伙伴認識你,還能領取20積分哦,立即完善>

標簽 > pll

文章:488個 視頻:54個 瀏覽:136399次 帖子:518個

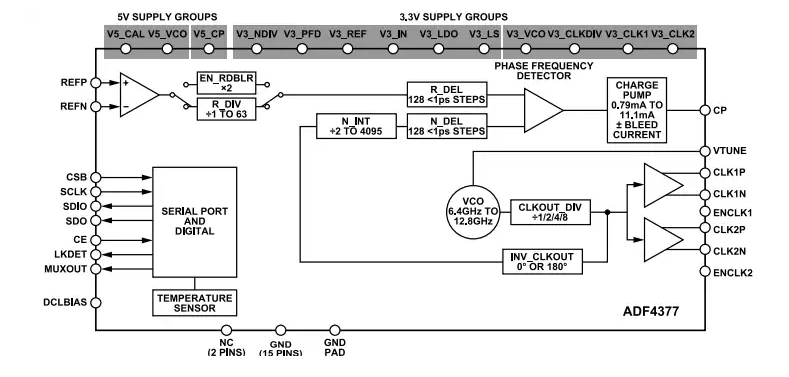

Analog Devices Inc. ADF44377低抖動微波寬帶合成器數據手冊

Analog Devices Inc. ADF4377低抖動微波寬帶合成器是一種高性能、超低抖動、雙輸出集成N相鎖定環(PLL),集成有電壓控制振蕩器(...

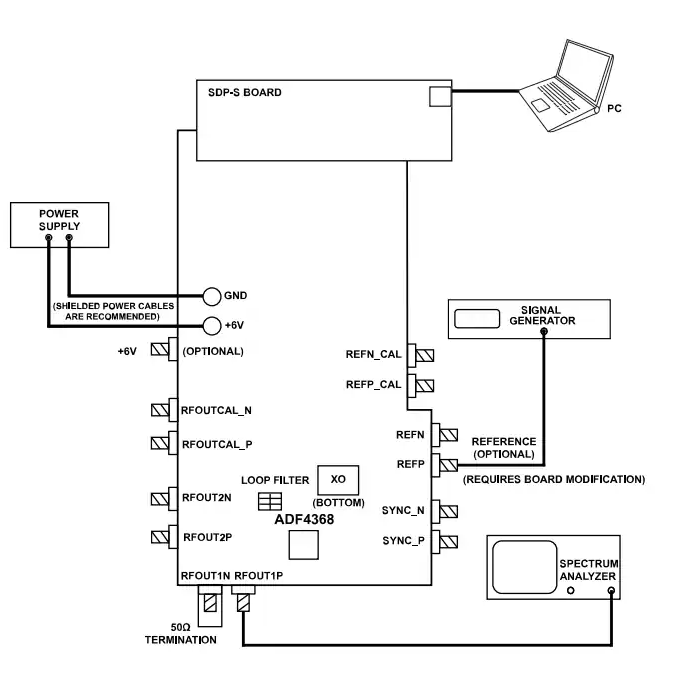

Analog Devices Inc. EV-ADF4368SD1Z評估板數據手冊

Analog Devices EV-ADF4368SD1Z 評估板用于演示ADF4368小數頻率合成器(具有適用于鎖相環 (PLL) 的集成壓控振蕩器 ...

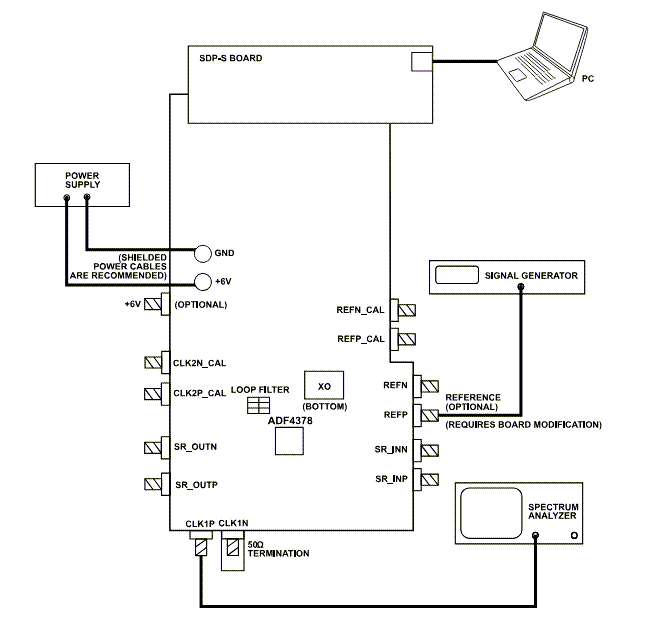

Analog Devices Inc. EV-ADF4378SD1Z 評估套件數據手冊

Analog Devices EV-ADF4378SD1Z評估套件支持用戶評估帶有用于鎖相環 (PLL) 的集成壓控振蕩器 (VCO) 的ADF4378...

Analog Devices Inc. ADF4382x小數N分頻鎖相環 (PLL)數據手冊

Analog Devices ADF4382x小數N分頻鎖相環 (PLL) 是一款高性能、超低抖動、小數N分頻鎖相環 (PLL)。它集成了壓控振蕩器 (...

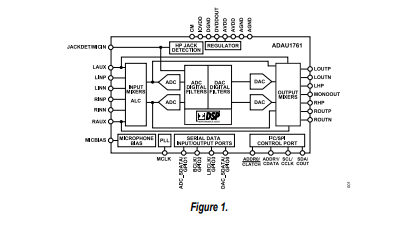

ADAU1761集成PLL的SIGMADSP立體聲、低功耗、96KHZ、24位音頻編解碼器技術手冊

ADAU1761是一款低功耗、集成數字音頻處理功能的立體聲音頻編解碼器,支持立體聲48 kHz錄音和回放,采用1.8 V模擬電源供電,功耗為14mW。立...

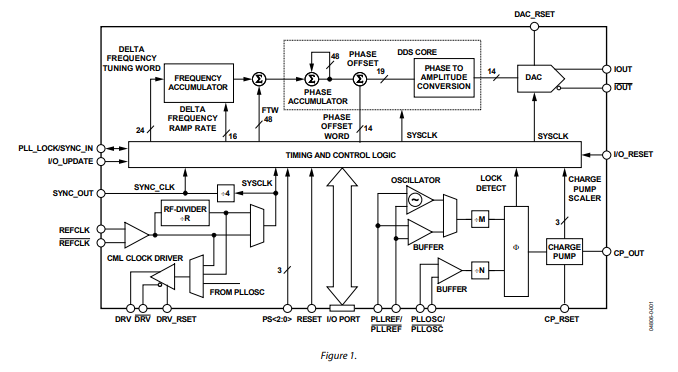

AD9956基于DDS的2.7 GHz AgileRF?頻率合成器技術手冊

AD9956是ADI公司的首款AgileRF頻率合成器,由一個DDS和PLL電路組成。DDS具有一個工作速度最高達400 MSPS的14位DAC和一個4...

易靈思的FPGA在生成PLL的方式與別的廠家稍有區別,這與其的core和interface架構是相對應的。對于易靈思的FPGA來講,PLL,GPIO,M...

2025-06-07 標簽:pll 411 0

2024年07月09日,一站式定制芯片及IP供應商——燦芯半導體(上海)股份有限公司(燦芯股份,688691)宣布成功研發出一款通用高性能小數分頻鎖相環...

? 6月28日,為期三天的2024 MWC上海世界移動通信大會順利落幕,本屆展會期間共累計吸引數萬名觀眾齊聚上海,展示移動通信領域強大的吸引力和號召力。...

ADC、PLL、相噪、三階交調、計量校準、自動編程等測試大揭秘

5月8日,中星聯華技術支持總監蘇水金給帶來《精密測試關鍵技術大揭秘!》,詳解中星聯華超低相噪微波信號源的6大核心特色,助您快速精準測試,解決尖端測試的苛...

低壓差調節器(LDO)如何影響PLL相位噪聲?? 低壓差調節器 (LDO) 在集成電路設計中扮演著非常重要的角色。它們的主要功能是將高電壓降至可接受的低...

鎖相環不是能夠完全跟蹤輸入信號的頻率嗎?為什么還會有固有頻差?

鎖相環不是能夠完全跟蹤輸入信號的頻率嗎?為什么還會有固有頻差? 鎖相環(PLL)是一種常見的電路系統,用于跟蹤和鎖定輸入信號的頻率。盡管PLL通常能夠有...

鎖相環同步帶與捕獲帶有區別嗎? 鎖相環(簡稱PLL)同步帶和捕獲帶是鎖相環中兩個重要的工作模式,它們在功能和應用上存在一些區別。 1. 定義和原理: -...

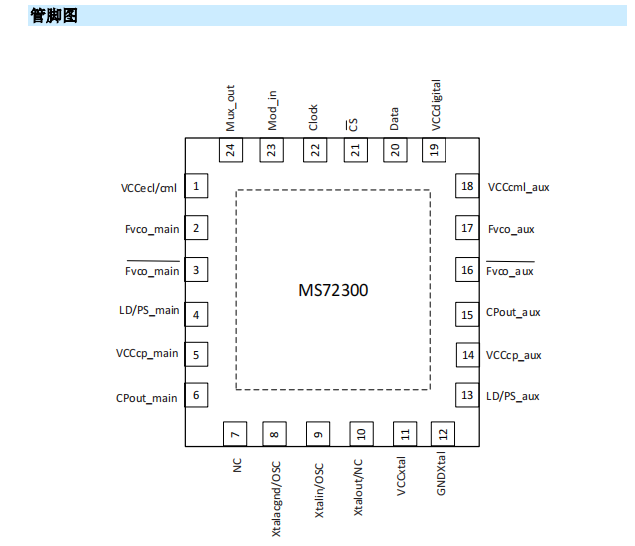

無雜散、2.1GHz、雙環路小數N分頻頻率綜合器MS72300

MS72300 是一款雙環路、小數 N 分頻頻率綜合器。包含主環路和副環路鎖相環。它提供了極高的頻率分辨率、快的輸出頻率切換速度和低相位噪聲性能。芯片須...

如何評估分布式PLL系統的相位噪聲? 要評估分布式PLL系統的相位噪聲,我們需要先了解什么是PLL系統和相位噪聲。PLL(Phase Locked Lo...

| 型號 | 描述 | 數據手冊 | 參考價格 |

|---|---|---|---|

| PLL650-02XI | PLL650-02XI - Low EMI Network LAN Clock - PhaseLink Corporation |

獲取價格

|

|

| PLL650-02XC-R | PLL650-02XC-R - Low EMI Network LAN Clock - PhaseLink Corporation |

獲取價格

|

|

| PLL650-02XC | PLL650-02XC - Low EMI Network LAN Clock - PhaseLink Corporation |

獲取價格

|

|

| PLL650-02 | PLL650-02 - Low EMI Network LAN Clock - PhaseLink Corporation |

獲取價格

|

|

| PLL620-80DI | PLL620-80DI - Low Phase Noise XO (9.5-65MHz Output) - PhaseLink Corporation |

獲取價格

|

換一批

換一批

編輯推薦廠商產品技術軟件/工具OS/語言教程專題

| 電機控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機 | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機 | PID | MOSFET | 傳感器 | 人工智能 | 物聯網 | NXP | 賽靈思 |

| 步進電機 | SPWM | 充電樁 | IPM | 機器視覺 | 無人機 | 三菱電機 | ST |

| 伺服電機 | SVPWM | 光伏發電 | UPS | AR | 智能電網 | 國民技術 | Microchip |

| 開關電源 | 步進電機 | 無線充電 | LabVIEW | EMC | PLC | OLED | 單片機 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 藍牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太網 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 語音識別 | 萬用表 | CPLD | 耦合 | 電路仿真 | 電容濾波 | 保護電路 | 看門狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 閾值電壓 | UART | 機器學習 | TensorFlow |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |