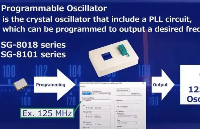

可編程晶振改變頻率的核心原理是:通過內部集成的鎖相環(PLL)和數字分頻/倍頻電路,對基礎石英晶體產生的固定頻率進行精密的數學運算(分頻、倍頻、分數分頻),最終輸出一個用戶通過數字接口(如I2C、SPI)編程設定的目標頻率。

以下是詳細的步驟和原理:

1、基礎頻率源:

核心仍然是一個高品質的石英晶體振蕩器(通常工作在相對較低的固定頻率,例如10 MHz、20 MHz、25 MHz、50 MHz等)。這個頻率非常穩定且精確(精度通常在±10~±50 ppm),但它是固定的。

2、鎖相環:

· 可編程晶振內部集成了一個關鍵的電路——鎖相環。

· PLL的基本工作原理:

· 壓控振蕩器:產生一個高頻輸出信號。

· 相位/頻率檢測器:將VCO的輸出頻率(經過分頻后)與參考頻率(來自基礎晶體振蕩器)進行比較。

· 電荷泵和環路濾波器: 將檢測器輸出的誤差信號轉換成平滑的電壓信號。

· 反饋分頻器: 將VCO的高輸出頻率除以一個可編程的整數N,得到反饋頻率。

當PLL鎖定后,VCO的輸出頻率 Fvco 滿足:Fvco = N * Fref。這里Fref 就是基礎晶振的頻率。

3、頻率合成(分頻與倍頻):

PLL的核心作用是利用基礎頻率Fref合成出一個新的、更高的頻率Fvco = N * Fref。N是一個可以通過編程設置的整數(倍頻系數)。

輸出分頻器:

通常,Fvco的頻率遠高于最終需要的輸出頻率Fout。

因此,在PLL的輸出端(VCO之后)還有一個或多個可編程輸出分頻器。

這些分頻器將 Fvco 除以一個可編程的整數 M,得到最終輸出頻率:Fout = Fvco / M = (N * Fref) / M。

分數分頻:

為了獲得更精細的頻率步進(遠小于 Fref),現代高性能可編程晶振普通采用分數-N PLL技術。

整數分頻器 N的基礎上,分頻比可以在N和N+1之間快速地、以一定比例切換。例如,平均分頻比可以是N + F/K(其中 F和K是整數)。

這使得輸出頻率可以表示為:Fout = (N + F/K) * Fref / M。

F 和K 也是可以通過編程設置的參數。K 通常很大(例如 22?),使得分數部分F/K可以非常小,從而實現極精細的頻率分辨率(如0.1 ppm或更小)。

4、編程接口:

· 用戶通過標準的數字接口(最常見的是I2C 或 SPI)與可編程晶振內部的寄存器進行通信。

· 制造商提供編程指南或配置軟件,用戶只需輸入所需的目標輸出頻率Fout。

· 晶振內部的微控制器或狀態機根據Fout、基礎頻率Fref 以及內部電路的限制,自動計算出最優的分頻/倍頻系數組合(N, M, F, K 等)。

· 用戶通過接口將這些系數值寫入晶振內部相應的配置寄存器。

5、輸出驅動:

合成并分頻后的信號經過輸出緩沖/驅動電路,轉換為具有標準電平(如LVCMOS、LVDS、HCSL等)和驅動能力的時鐘信號輸出。

總結關鍵點:

· 基礎固定頻率:核心是穩定但固定的石英晶體振蕩器。

· 數學變換: 利用可編程的PLL(整數/分數分頻)和輸出分頻器,對基礎頻率進行精確的乘法和除法運算。

· 公式:Fout = (N * Fref) / M(整數模式)或更精細的 Fout = ((N + F/K) * Fref) / M (分數模式)。

· 數字控制: 用戶通過I2C/SPI接口設定目標頻率Fout,晶振自動計算并設置內部參數 N, M, F, K。

· 靈活性: 通過改變這些數字參數,可以在晶振支持的頻率范圍內,產生幾乎任意所需的輸出頻率(分辨率可達ppb級),而無需更換物理晶體。

· 附加功能:許多可編程晶振還集成了其他可編程功能,如輸出電平選擇、使能/禁用控制、擴頻調制(SSM)等,也是通過相同的接口配置。

因此,可編程晶振并不是通過物理方式改變石英晶體本身的振動頻率(那是VCXO的原理),而是通過復雜的數字頻率合成技術,將固定晶體頻率“轉換”成用戶所需的任意目標頻率。

-

有源晶振

+關注

關注

1文章

930瀏覽量

21318 -

晶振

+關注

關注

35文章

3254瀏覽量

70037 -

pll

+關注

關注

6文章

889瀏覽量

136350

發布評論請先 登錄

可編程晶振怎么改變頻率

可編程晶振怎么改變頻率

評論