Analog Devices ADF4382x小數(shù)N分頻鎖相環(huán) (PLL) 是一款高性能、超低抖動、小數(shù)N分頻鎖相環(huán) (PLL)。它集成了壓控振蕩器 (VCO),是5G或數(shù)據(jù)轉換器時鐘應用生成本地振蕩器 (LO) 的理想之選。該高性能PLL的品質因數(shù)包括 ?239dBc/Hz,1/f低噪聲,整數(shù)模式下PFD頻率高達625MHz,可實現(xiàn)超低帶內噪聲和集成抖動。ADF4382x可生成11.5GHz至21GHz基倍頻程范圍內的頻率,無需使用次諧波濾波器。ADF4382x上的二分頻和四分頻輸出分頻器可分別生成5.75GHz至10.5GHz和2.875GHz至5.25GHz的頻率。

數(shù)據(jù)手冊:*附件:Analog Devices Inc. ADF4382x小數(shù)N分頻鎖相環(huán) (PLL)數(shù)據(jù)手冊.pdf

Analog Devices ADF4382x通過在PLL反饋環(huán)路中添加輸出分頻器,自動將其輸出與多個數(shù)據(jù)轉換器時鐘應用的輸入?yún)⒖歼吘墝R。針對需要確定性延遲或延遲調整功能的應用,提供了分辨率小于1ps的可編程輸出延遲參考。跨多個設備和溫度的輸出延遲匹配參考可實現(xiàn)可預測且精確的多芯片時鐘和系統(tǒng)參考 (SYSREF) 對齊。ADF4382x框圖簡潔,具有簡化的串行外設接口 (SPI) 寄存器映射、可重復的多芯片時鐘對齊,并且通過允許片外SYSREF生成來限制不需要的時鐘雜散,從而縮短了開發(fā)時間。

特性

- 輸出頻率范圍:687.5MHz至22GHz

- 集成RMS抖動:20GHz

- 20fs(集成帶寬:100Hz至100MHz)

- 31fs(ADC SNR方法)

- 快速VCO校準時間:<1μs

- VCO自動校準時間:<100μs

- 相位噪底:-156dBc/Hz(20GHz時)

- PLL規(guī)格

- 標稱帶內相位噪底:-239dBc/Hz

- 標稱1/f相位噪底:-287dBc/Hz

- 最大相位/頻率檢測器輸入頻率:625MHz

- 基準輸入頻率:4.5GHz

- 典型雜散f

PFD:-90dBc

- 輸出延遲參考規(guī)格

- 傳播延遲溫度系數(shù):0.06ps/°C

- 調整步長:<1ps

- 多芯片輸出相位對齊

- 3.3V和5V電源

- ADIsimPLL?環(huán)路濾波器設計工具支持

- 7mm × 7mm、48端子LGA封裝

- 工作溫度范圍:-40 °C至+105 °C

應用

- 高性能數(shù)據(jù)轉換器時鐘

- 無線基礎設施(MC-GSM、5G、6G)

- 測試與測量

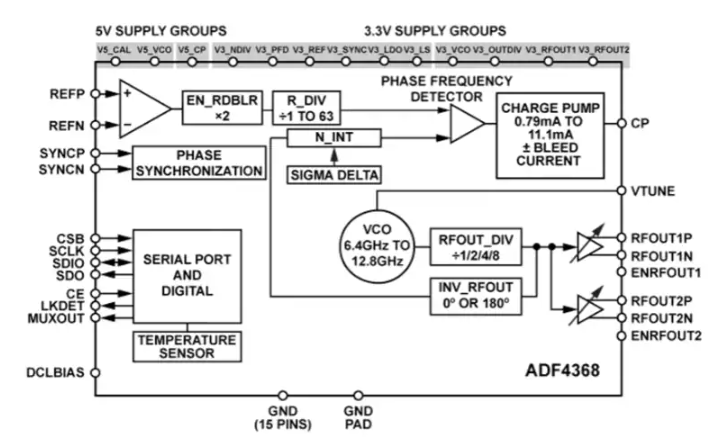

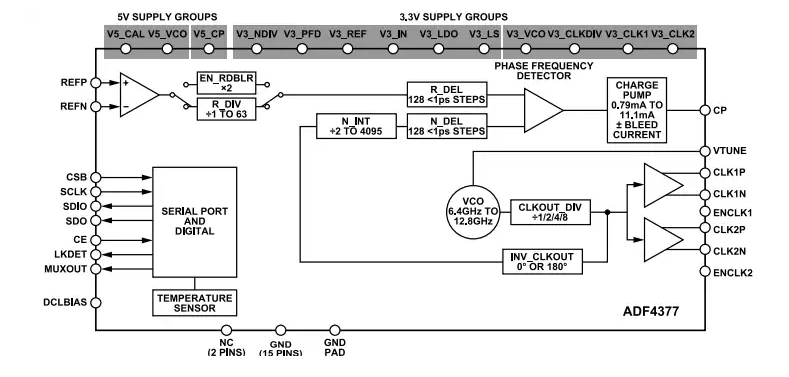

功能框圖

-

鎖相環(huán)

+關注

關注

35文章

596瀏覽量

88502 -

pll

+關注

關注

6文章

887瀏覽量

136116 -

Analog

+關注

關注

12文章

9716瀏覽量

58882 -

高性能

+關注

關注

0文章

204瀏覽量

20834

發(fā)布評論請先 登錄

鎖相環(huán)常見問題解答

基于adf4351鎖相環(huán)相關硬件的設計資料分享

小數(shù)分頻鎖相環(huán)的工作原理

鎖相環(huán)(PLL),鎖相環(huán)(PLL)是什么意思

低噪聲小數(shù)N分頻鎖相環(huán)實現(xiàn)方案

UG-804:評估ADF4355-2小數(shù)/整數(shù)N鎖相環(huán)頻率合成器

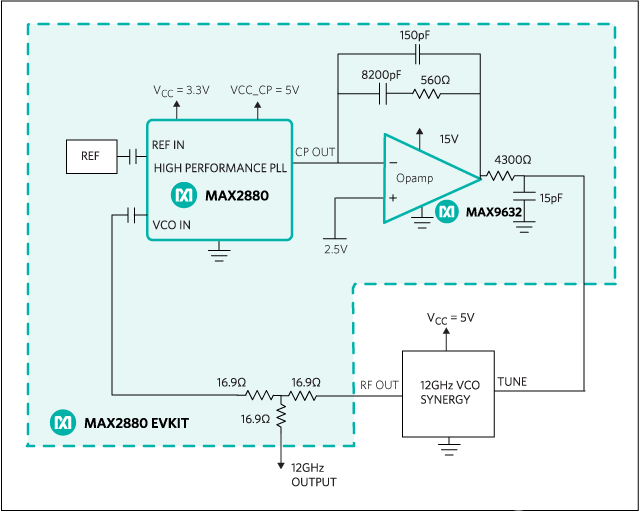

12GHz、超低相位噪聲小數(shù)N分頻鎖相環(huán)的設計

鎖相環(huán)整數(shù)分頻和小數(shù)分頻的區(qū)別是什么?

ADF4155整數(shù)N/小數(shù)N分頻PLL頻率合成器技術手冊

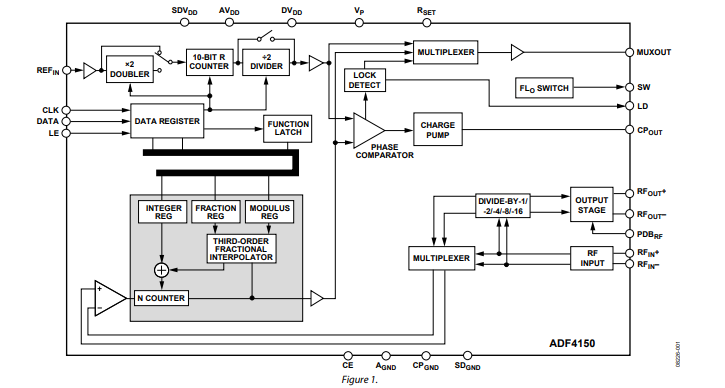

ADF4151小數(shù)N/整數(shù)N分頻PLL頻率合成器技術手冊

ADF4150小數(shù)N/整數(shù)N分頻PLL頻率合成器技術手冊

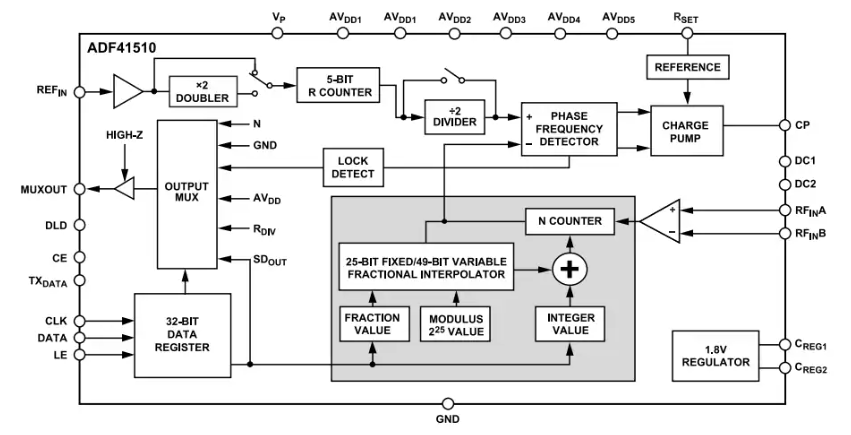

Analog Devices Inc. ADF41510整數(shù)N/小數(shù)N PLL合成器數(shù)據(jù)手冊

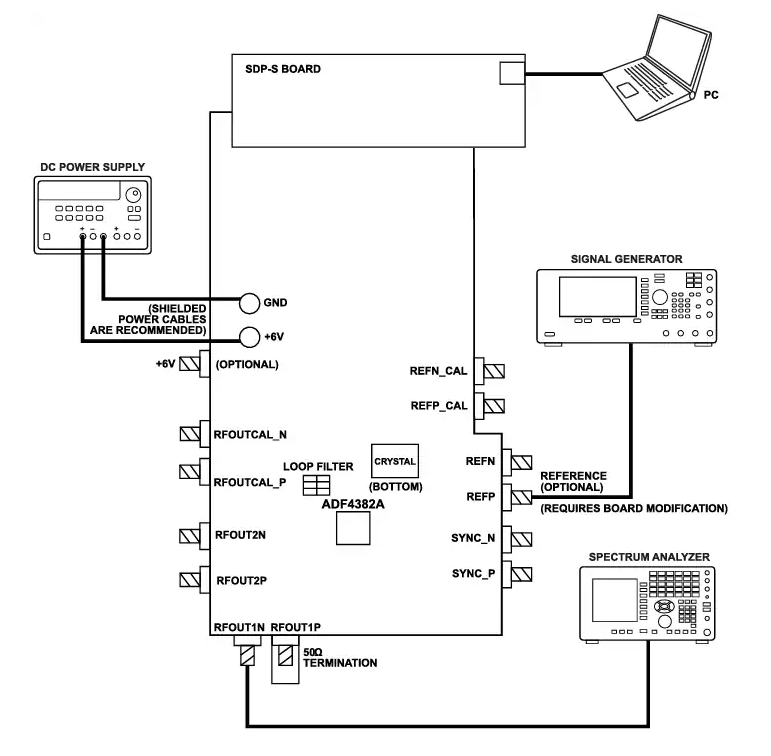

Analog Devices Inc. EV-ADF4382A 評估板數(shù)據(jù)手冊

Analog Devices Inc. ADF4368微波寬頻合成器數(shù)據(jù)手冊

Analog Devices Inc. ADF44377低抖動微波寬帶合成器數(shù)據(jù)手冊

Analog Devices Inc. ADF4382x小數(shù)N分頻鎖相環(huán) (PLL)數(shù)據(jù)手冊

Analog Devices Inc. ADF4382x小數(shù)N分頻鎖相環(huán) (PLL)數(shù)據(jù)手冊

評論