當(dāng)我們驗證片上系統(tǒng)(SoC)嵌入了具有多個數(shù)字外設(shè)的微處理器以及可能的模擬模塊時,我們希望檢查所有實現(xiàn)的功能和可能的極端情況,以最大限度地縮短驗證時間。多種技術(shù)和方法的混合用于改進(jìn)功能驗證并提取覆蓋等級的度量:基于通用驗證方法(UVM)的形式驗證和隨機(jī)約束測試增加了發(fā)現(xiàn)錯誤的可能性。有時我們?yōu)镽TL驗證創(chuàng)建一個完美有效的測試,但發(fā)現(xiàn)它不能在門級仿真期間重復(fù)使用,因為UVM監(jiān)視器掛在內(nèi)部SoC信號上,這些信號在實現(xiàn)階段后可能會消失或改變。

本文將描述創(chuàng)建有效的自檢模型是多么容易,這些測試既簡單又可以在門級模擬過程中重復(fù)使用。令人驚訝的是,通過改變數(shù)據(jù)流,我們可以為測試平臺帶來好處,降低記分板的復(fù)雜性,這也意味著更少的測試開發(fā)時間。

流程基于實例化UVM驗證用于檢查接口的組件,例如SPI,I 2 C,& UART,但它也可以擴(kuò)展到更復(fù)雜的接口。

SoC驗證流程

最有效的SoC驗證是基于內(nèi)部總線內(nèi)部,特定內(nèi)部模塊和主SoC接口上的多個UVM驗證組件(UVM VC)的實例化。這些UVM VC用作總線協(xié)議檢查器(例如,AMBA檢查器);串行協(xié)議檢查器和主動主控器(例如,I 2 C,SPI,UART,JTAG,SATA,PCIe)。

基于UVM開發(fā)的測試應(yīng)該是自檢的;必須通過檢查器驗證每個操作,激勵和事務(wù),如果不匹配,會引發(fā)一個“標(biāo)志”,停止模擬并發(fā)出模擬器控制臺上顯示的錯誤消息并寫入日志文件。

通信接口(例如,SPI)的驗證需要使用由在總線上獲取事務(wù)的收集器形成的UVM VC,用于檢查協(xié)議合規(guī)性的監(jiān)視器以及生成的生成的總線功能模型(BFM)交易。 SoC和外部UVM VC之間交換的數(shù)據(jù)通過名為記分板的模塊進(jìn)行驗證。

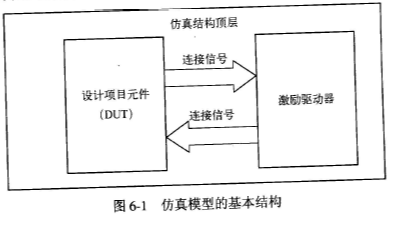

此記分板至少有兩個端口,其中添加的對象與第二個相匹配 - 參考。如果不匹配,則發(fā)出錯誤。在門級仿真期間必須重復(fù)使用這種檢查器以刺激關(guān)鍵路徑。圖1顯示了驗證測試平臺的簡單框圖,該平臺使用多個檢查器進(jìn)行有效的驗證方法。

圖1:典型的UVM驗證測試平臺

黃色塊是UVM VC。總線監(jiān)視器是一個只有監(jiān)視器和檢查器的無源組件。

用于測試串行外設(shè)的通用數(shù)據(jù)流是將數(shù)據(jù)從UVM VC發(fā)送到微處理器并檢查數(shù)據(jù)是否有到達(dá)目的地(微處理器)。在第二步中,我們將數(shù)據(jù)從微處理器發(fā)送到UVM VC,檢查正確的數(shù)據(jù)是否已到達(dá)目的地(UVM VC)。

圖2顯示了數(shù)據(jù)記分板<的示例/i>用于全雙工同步通信(例如,SPI)。 UVM VC和外圍總線上的監(jiān)視器(被動)用于將數(shù)據(jù)發(fā)送到記分板:UVM VC發(fā)送的數(shù)據(jù)被添加到記分板 TX路徑,當(dāng)它們到達(dá)外圍設(shè)備時,將通過總線監(jiān)視器發(fā)送到相同的記分板進(jìn)行匹配。來自外圍設(shè)備的數(shù)據(jù)被添加到記分板 RX路徑中,并與UVM VC被動監(jiān)視器接收的數(shù)據(jù)相匹配。

圖2:全雙工同步外設(shè)示例

此方法的主要缺點是門級仿真的可移植性。在實施階段,RTL中可用的內(nèi)部信號可能會在優(yōu)化的網(wǎng)表中消失,UVM VC模塊的綁定變得困難,有時甚至不可能(例如,在合成期間刪除未使用的端口)。

新的SoC驗證流程

新流程的基本概念是記分板中檢查的數(shù)據(jù)不應(yīng)來自內(nèi)部SoC節(jié)點上綁定的監(jiān)視器(參見圖2)。因此,修改了測試平臺配置,以便僅使用UVM VC(主動和被動)進(jìn)行頂層綁定的數(shù)據(jù)檢查。內(nèi)部監(jiān)視器(綁定在SoC內(nèi)部節(jié)點上的監(jiān)視器)僅用于RTL仿真,檢查總線的合規(guī)性并跟蹤覆蓋范圍。

此時,有必要更改數(shù)據(jù)在UVM VC和SoC外設(shè)之間交換數(shù)據(jù)包的流程。主要要求是:

數(shù)據(jù)隨機(jī)化

門級模擬的可移植性

易用性

由UVM VC生成并由外圍設(shè)備接收的隨機(jī)約束數(shù)據(jù)分組被SoC用于生成出站分組。為了增加隨機(jī)化,SoC中的微處理器計算接收數(shù)據(jù)的CRC并將結(jié)果用作要傳輸?shù)臄?shù)據(jù)。

記分板將從UVM獲取數(shù)據(jù)VC,在將它們添加到數(shù)據(jù)列表之前,它將計算CRC。從外圍設(shè)備返回的數(shù)據(jù)將直接添加到記分板以進(jìn)行匹配過程。圖3顯示了這個新流程的一個示例。

圖3:數(shù)據(jù)檢查的新方法

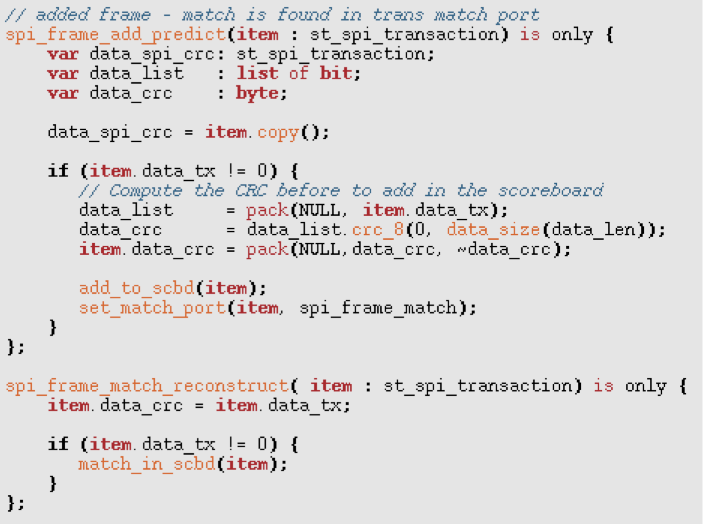

計算CRC非常簡單;對于記分板,可以使用內(nèi)置函數(shù)(偽方法),例如,可以使用 e 語言:

list_bytes 。crc_32(來自字節(jié),字節(jié)數(shù))

list_bytes 。crc_8(來自字節(jié),字節(jié)數(shù))

它逐字節(jié)讀取列表返回位或字節(jié)列表的CRC函數(shù)的整數(shù)值。可以計算CRC,定義起始字節(jié)(通過第一個參數(shù) from byte )和選定的字節(jié)數(shù)(通過第二個參數(shù)字節(jié)數(shù))。

32位CRC的生成多項式為:

x 32 + x 26 + x 23 + x 22 + x 16 + x 12 + x 11 + x 10 + x 8 + x 7 + x 5 + x 4 + x 2 + x +1

8位CRC的生成多項式為:

x 8 + x 2 + x + 1

類似的函數(shù)用于SoC中微處理器執(zhí)行的 C 代碼:

POLY_GEN8為0x03。可以使用POLY_GEN32 = 0x2608EDB為CRC32擴(kuò)展該功能。

使用此方法可以極大地簡化記分板上的數(shù)據(jù)管理;由于數(shù)據(jù)檢查是在串行接口上進(jìn)行的,因此它與微處理器總線的數(shù)據(jù)大小無關(guān),可以是8,16,32位或更多。以下是記分板的示例。

全雙工同步接口

如果是全雙工同步接口,例如SPI,我們可以有兩種可能的模式:外設(shè)是從機(jī),或外設(shè)是主機(jī)。

當(dāng)外設(shè)是從機(jī)時,事務(wù)由外部UVM VC啟動。全雙工模式意味著必須同時發(fā)送和接收數(shù)據(jù)。由于我們希望避免在SoC側(cè)生成數(shù)據(jù)(在 C 代碼上沒有有線數(shù)據(jù)),因此有效數(shù)據(jù)存在系統(tǒng)延遲。此延遲應(yīng)在記分板上實現(xiàn),以便正確比較交換的數(shù)據(jù)。

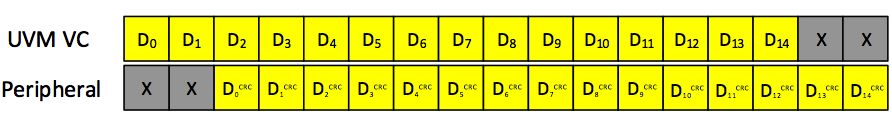

圖4:全雙工數(shù)據(jù)序列用于從模式

圖4顯示了在主(UVM VC)和從(外設(shè))之間交換的數(shù)據(jù)序列的示例。由外圍設(shè)備發(fā)送的第一個符號對于記分板“不關(guān)心”,因此被釋放。微處理器需要一些時間從緩沖區(qū)獲取數(shù)據(jù)并計算CRC。一段時間后,數(shù)據(jù)準(zhǔn)備就緒,交換繼續(xù)從UVM VC隨機(jī)生成和來自外圍側(cè)的偽隨機(jī)數(shù)據(jù)(在D x 上計算的CRC)。

我們可以通過使用傳統(tǒng)的“不關(guān)心”數(shù)據(jù)(例如,零)來進(jìn)行自動符號同步。當(dāng)然,這些數(shù)據(jù)不應(yīng)由UVM VC生成。 SoC上的外設(shè)將發(fā)送零直到CRC數(shù)據(jù)準(zhǔn)備就緒,并且UVM VC以足夠的零符號終止以完成記分板中的匹配。

當(dāng)外圍設(shè)備是主設(shè)備時,事務(wù)通過微處理器自行啟動。

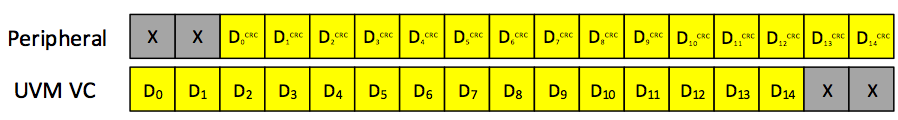

圖5:主模式的全雙工數(shù)據(jù)序列

數(shù)據(jù)流與奴隸模式的情況非常相似。圖5顯示了在主(外設(shè))和從(UVM VC)之間交換的數(shù)據(jù)序列的示例。外圍設(shè)備發(fā)送的第一個符號對于記分板“不關(guān)心”。 UVM VC用隨機(jī)符號D x 回復(fù),微處理器用它來計算外圍設(shè)備發(fā)送的偽隨機(jī)數(shù)據(jù)。如上所述,黃色突出顯示的符號是在記分板中比較的符號。

半雙工接口

如果是半雙工接口,例如I 2 C,我們可以有兩種可能的模式:外設(shè)是從機(jī),或外設(shè)是主機(jī)。

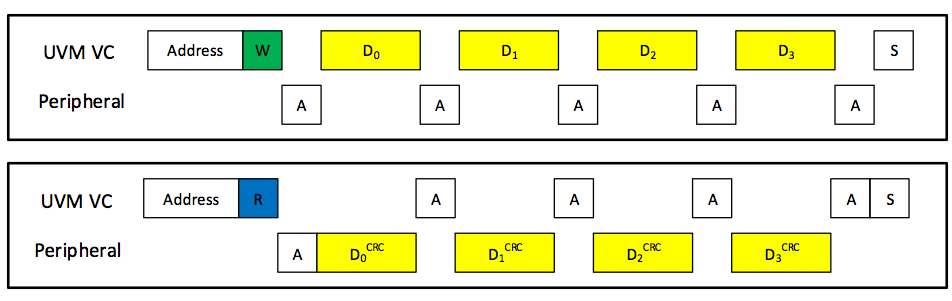

外設(shè)是slave,事務(wù)由外部UVM VC啟動。半雙工模式基于通信協(xié)議,其中主設(shè)備發(fā)送命令請求數(shù)據(jù)作為回復(fù)或?qū)?shù)據(jù)發(fā)送到專用從設(shè)備。

對于全雙工模式,有必要定義良好的流程這樣可以避免 C 代碼中的數(shù)據(jù)(非隨機(jī))并使數(shù)據(jù)檢查變得簡單:

通過發(fā)送write命令啟動事務(wù)。 UVM VC將開始發(fā)送數(shù)據(jù)包。在計算CRC之后,這些數(shù)據(jù)被添加到記分板中。

接收的數(shù)據(jù)被DUT用作“回復(fù)讀取”命令。微處理器計算接收數(shù)據(jù)的CRC并準(zhǔn)備數(shù)據(jù)包以進(jìn)行回復(fù)。

UVM VC發(fā)送讀命令。外圍設(shè)備開始發(fā)送先前準(zhǔn)備的數(shù)據(jù)。這些數(shù)據(jù)將添加到記分板中以進(jìn)行匹配。

圖6顯示了此數(shù)據(jù)握手的簡單圖表。

圖6:從模式的半雙工數(shù)據(jù)交換

主模式

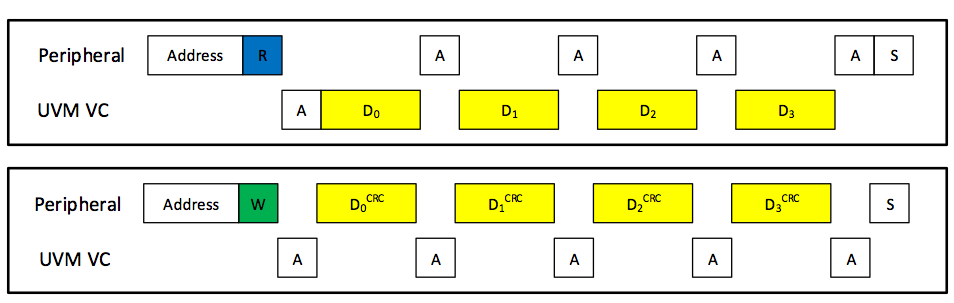

當(dāng)外圍設(shè)備是主設(shè)備時,事務(wù)通過微處理器自行啟動。

在這種情況下,為了利用UVM VC的隨機(jī)約束特性,協(xié)議必須

通過發(fā)送讀命令啟動事務(wù)。 UVM VC將開始作為回復(fù)發(fā)送數(shù)據(jù)包。在計算CRC之后,這些數(shù)據(jù)被添加到記分板中。

接收的數(shù)據(jù)被DUT用作“寫入數(shù)據(jù)”命令。微處理器計算接收數(shù)據(jù)的CRC并為下一步準(zhǔn)備數(shù)據(jù)包。

外設(shè)發(fā)送寫命令,然后開始發(fā)送先前準(zhǔn)備的數(shù)據(jù)。這些數(shù)據(jù)將添加到記分板中以進(jìn)行匹配。

圖7顯示了此數(shù)據(jù)握手的簡單圖表。

圖7:主模式的半雙工數(shù)據(jù)交換

復(fù)雜協(xié)議

相同的方法可以也可用于USB或以太網(wǎng)等復(fù)雜協(xié)議。概念是相同的:對于全雙工通信,初始符號是“不關(guān)心”(空符號),然后DUT使用接收的樣本來計算CRC并將數(shù)據(jù)發(fā)回。

對于半雙工,數(shù)據(jù)交換由UVM VC啟動,然后DUT使用接收的數(shù)據(jù)包構(gòu)建傳輸數(shù)據(jù)包。

-

仿真

+關(guān)注

關(guān)注

51文章

4245瀏覽量

135362 -

PCB打樣

+關(guān)注

關(guān)注

17文章

2974瀏覽量

22379 -

華強PCB

+關(guān)注

關(guān)注

8文章

1831瀏覽量

28455 -

華強pcb線路板打樣

+關(guān)注

關(guān)注

5文章

14629瀏覽量

43761

發(fā)布評論請先 登錄

RTL級仿真與門級仿真

關(guān)于RTL仿真和門級仿真求助~

IC驗證“UVM驗證平臺加入objection機(jī)制和virtual interface機(jī)制“(七)

數(shù)字IC驗證之“UVM”基本概述、芯片驗證和驗證計劃(1)連載中...

數(shù)字IC驗證之“什么是UVM”“UVM的特點”“UVM提供哪些資源”(2)連載中...

數(shù)字IC驗證之“典型的UVM平臺結(jié)構(gòu)”(3)連載中...

數(shù)字IC驗證之“構(gòu)成uvm測試平臺的主要組件”(4)連載中...

數(shù)字IC驗證之“搭建一個可以運行的uvm測試平臺”(5)連載中...

什么是uvm?uvm的特點有哪些呢

UVM驗證平臺執(zhí)行硬件加速

如何建立VHDL程序的仿真模型和平臺及仿真過程詳細(xì)說明

UVM中的虛擬序列:為什么,如何?

測試與驗證復(fù)雜的FPGA設(shè)計(2)——如何在虹科的IP核中執(zhí)行面向全局的仿真

重復(fù)使用UVM RTL驗證測試進(jìn)行門級仿真詳細(xì)過程介紹

重復(fù)使用UVM RTL驗證測試進(jìn)行門級仿真詳細(xì)過程介紹

評論