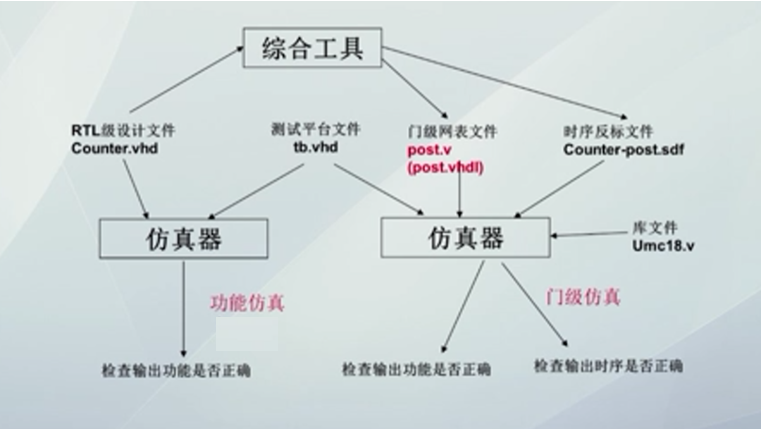

經過邏輯綜合過程后,Verilog代碼被轉化成門級網單,轉化后的門級網單需要被驗證與Verilog代碼功能是否一致,需要進行門級仿真。

Verilog代碼的仿真可以被稱為功能仿真,可以驗證Verilog代碼功能與設計需求是否一致。

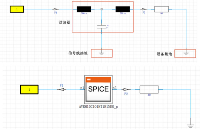

驗證Verilog代碼過程中需要編寫測試平臺文件tb.vhd,該平臺文件仍可以在門級仿真中使用。門級仿真所用的仿真器(仿真工具,如

Modelsim)與功能仿真相同,門級仿真還需要邏輯綜合保存的文件:門級網表文件和時序反標文件(時序相關信息),門級網表文件所用的底層電路(如:與門)的特性信息在庫文件中,庫文件由芯片制造公司提供,各個芯片制造公司的庫文件因其元器件性能的差異而不同。

綜上,門級仿真基于測試平臺文件、門級網表文件、時序反標文件、庫文件,可以進行更精確的仿真。設計人員除了可以通過門級仿真驗證門級網單與Verilog代碼功能是否一致,還可以檢查門級電路的時序是否正確。

圖片來源:學堂在線《IC設計與方法》

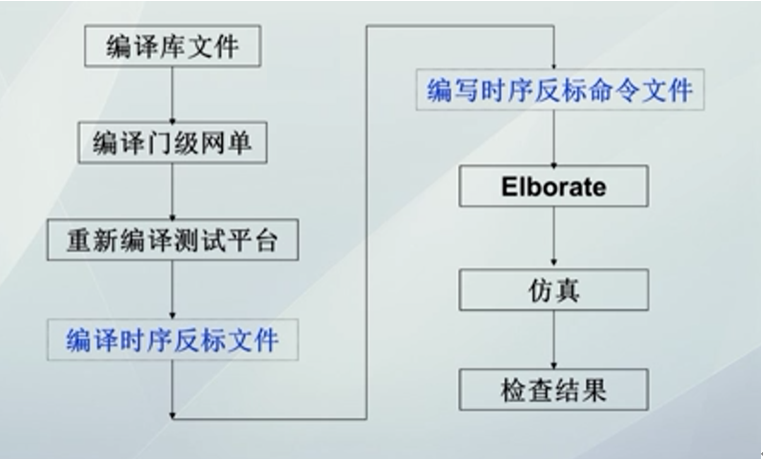

門級仿真的過程與功能仿真過程相類似,不同之處在于需要將庫文件重新編譯,庫文件編譯結束后,依次編譯門級網單、測試平臺、時序反標文件,并編寫時序反標的命令文件。

如果仿真工具采用Modelsim,時序反標文件可以內嵌在Modelsim工具中,不需編譯。如果采用NC仿真工具,還需要進行Elborate(個人理解Elborate步驟是進行精細化的設定)。

最后進行仿真并檢查結果。

圖片來源:學堂在線《IC設計與方法》

編譯庫文件時,需將底層門級電路單獨建立庫,而不能將庫文件混入到芯片設計代碼中。這是因為庫文件中有數百個元器件,混入芯片設計代碼中,難以定位由設計人員自主設計的部分。

因為設計方案最終確定前需要反復修改,所以編譯過程會反復進行,庫文件也需要重新編譯,需要及時清理過去編譯的內容。

因為門級網單的仿真步長(根據網絡資料理解:連續系統仿真中設置的最小時間間隔)和庫文件的仿真步長不一定相同,需要設置統一的仿真步長。底層單元庫(庫文件)仿真步長通常設置在ps(皮秒,1s=10-12s)量級,設計人員編寫的芯片代碼仿真步長通常設置在ns(納秒,1ns=10-9s)量級。

進行門級仿真前,時序反標信息需要標注到門級網單中。標注方式采用Verilog代碼中$sdfannotate系統任務,$sdfannotate系統任務可以向仿真工具輸入門級網單的時序信息。

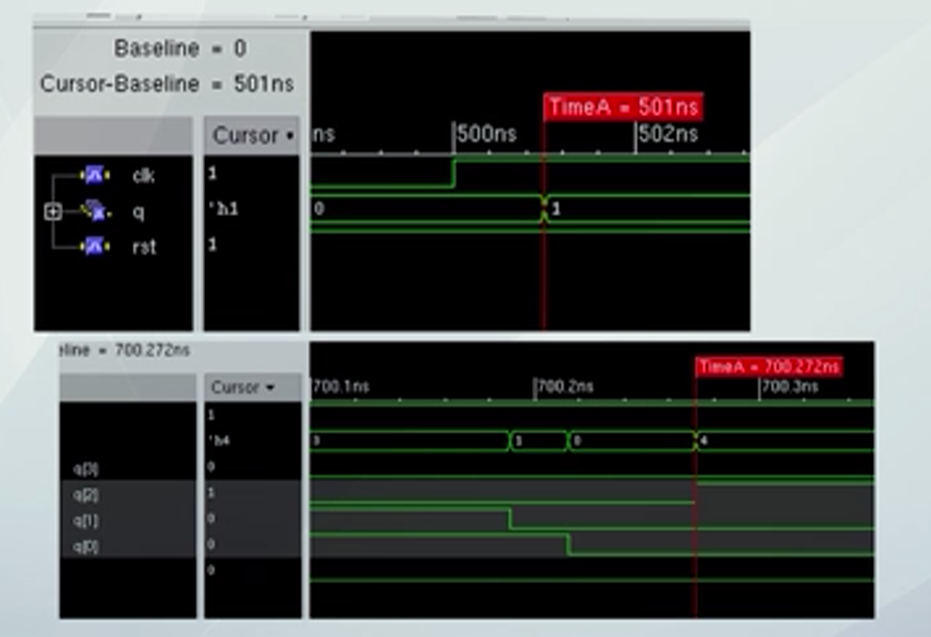

下圖是門級仿真的結果。偏上的圖片中,延時顯示的是1ns,長于門元器件的延時,意味著時序反標可能不正確。當時序反標不正確時,庫文件會采用默認延時,即該庫文件的默認延時是1ns。時序反標不正確的原因可能是反標文件名錯誤、反標流程錯誤等。

偏下的圖片是反標正確的結果,延時在0.1ns左右。正常情況下,下圖所映射的電路輸出應該從3直接變為4,但實際輸出由3變為1,再變為0,再變為4,所對應的波形會顯示出毛刺。如果該輸出只作為狀態信號(只在信號穩定時作為輸入)或輸出指示(如指示發光二極管發光),沒有什么影響,其他情況需要考慮毛刺的影響。

圖片來源:學堂在線《IC設計與方法》

審核編輯 :李倩

-

仿真

+關注

關注

51文章

4229瀏覽量

135231 -

Verilog

+關注

關注

28文章

1365瀏覽量

111694

原文標題:芯片設計相關介紹(26)——門級仿真

文章出處:【微信號:行業學習與研究,微信公眾號:行業學習與研究】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

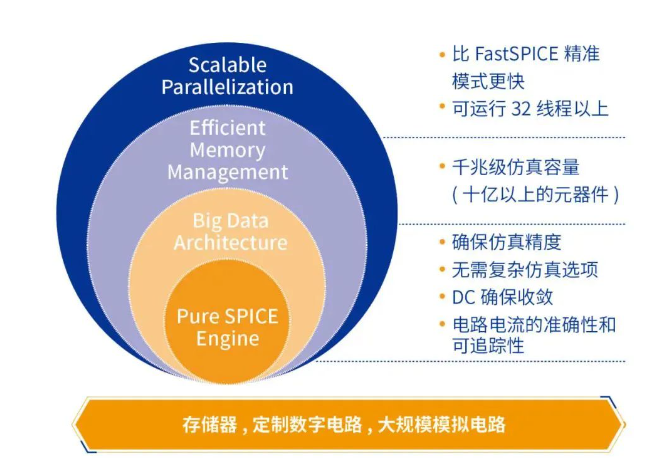

概倫電子千兆級高精度電路仿真器NanoSpice Giga介紹

概倫電子芯片級HBM靜電防護分析平臺ESDi介紹

光伏發電系統篇:單級式并網系統實時仿真

光伏發電系統篇:單級式并網系統實時仿真

OpenAI推進“星際之門”項目,評估美國數據中心選址

OpenAI“星際之門”首期工廠亮相

芯片后仿真要點

關于芯片PACK包和IDE綁定仿真的問題

新技術丨廣電計量成功開發系統級電磁脈沖防護仿真技術

芯片設計之門級仿真

芯片設計之門級仿真

評論