INNOVUS/ICC2吐出的netlist經(jīng)過Formal/LEC驗(yàn)證后,Star-RC/QRC抽取RC寄生參數(shù)文件并讀入到Tempus/PT分別做func/mbist/scan時(shí)序sign-off,寫出SDF3.0用以后仿真,搭建后仿真的驗(yàn)證環(huán)境,添加sc/io/macro的verilog model,仿真輸出VCD給Redhawk/Voltus做功耗/IR Drop分析。本文簡(jiǎn)要敘述下后仿真要點(diǎn):

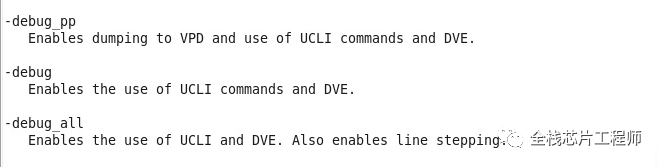

-debug選項(xiàng),為了導(dǎo)出VPD通常選擇-debug_pp;

-R表示編譯之后立即運(yùn)行仿真;

-gui表示在仿真0時(shí)刻打開DVE界面;

-l表示記錄編譯過程日志,后跟日志文件名;

+incdir+表示文件搜索路徑;

+v2k表示支持verilog 2001標(biāo)準(zhǔn);

-top設(shè)置編譯頂層模塊,后跟頂層module名,不是文件名;

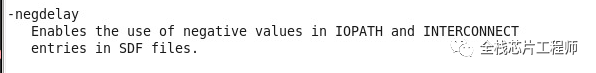

-negdelay

SDF文件中有負(fù)延遲時(shí),若不加-negdelay會(huì)出現(xiàn)SDF Error: SDF Error: NegativeDELAY ignored and replaced by 0.

即VCS將負(fù)延時(shí)忽略,用0取代負(fù)值。加參數(shù)-negdelay 可消除負(fù)延遲導(dǎo)致的error,變成warning,但最終都不影響設(shè)計(jì)。

SDF Warning:Negative IOPATH DELAY A to Y ignored.

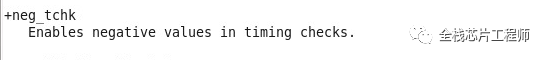

+neg_tchk支持負(fù)延遲檢查,主要是檢查holdtime,否則反標(biāo)中會(huì)把負(fù)值忽略為0

標(biāo)準(zhǔn)單元庫文件有兩種,譬如tsmc18_neg和tsmc18,前者支持neg_tchk負(fù)延時(shí)檢查,后者不支持。因?yàn)閔old time check的值是負(fù)的,所以要進(jìn)行negative timingcheck,否則默認(rèn)將會(huì)使負(fù)值的hold time check改為0。為了滿足對(duì)hold time負(fù)值的檢查,在vcs仿真時(shí)需加上+neg_tchk這個(gè)option。

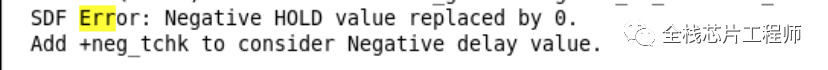

如果不加的話會(huì)產(chǎn)生下面的問題:

+maxdelays用SDF文件中的延遲,取代仿真庫中的延時(shí)(仿真庫中通常是建立時(shí)間1ns,保持時(shí)間0.5ns),取SDF文件中的最大延遲;

+mindelays用SDF文件中的延遲,取代仿真庫中的延時(shí),取SDF文件中的最小延遲(保持時(shí)間檢查);

實(shí)際上,我們會(huì)出ss、ff、tt等數(shù)個(gè)sdf,每個(gè)sdf里面都只有類似{max::max}形式,因此,每個(gè)sdf只對(duì)應(yīng)一種ss或ff形式的延時(shí)反標(biāo)。

+sdfverbose顯示所有的sdf反標(biāo)錯(cuò)誤

+no_notifier關(guān)閉時(shí)序檢查函數(shù)中的不定態(tài)生成傳播,即通過這個(gè)參數(shù),如果有時(shí)序違規(guī),控制臺(tái)會(huì)報(bào)告,但不會(huì)影響邏輯功能的正確輸出。

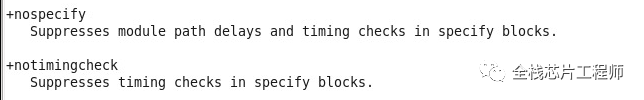

+nospecify 消除所有延遲,只做網(wǎng)表的功能仿真可以用;

+notimingchecks只是消除延遲違規(guī)斷言,避免輸出不定態(tài),但延遲還在。因此+nospecify的作用包括了+notimingchecks;

注意:+nospecify,加上該選項(xiàng)之后,所有的線延遲以及標(biāo)準(zhǔn)單元verilog文件中的固有延遲都沒有了,如果只是單純的不加sdf文件的話,標(biāo)準(zhǔn)單元verilog文件中的specify延遲還是有的。

+delay_mode_zero: Change all the delay specifications on all gates,switches, and continuous assignments to zero and change all module path delays to zero.

-

芯片

+關(guān)注

關(guān)注

460文章

52520瀏覽量

441065 -

仿真

+關(guān)注

關(guān)注

52文章

4289瀏覽量

135878 -

函數(shù)

+關(guān)注

關(guān)注

3文章

4381瀏覽量

64904 -

編譯

+關(guān)注

關(guān)注

0文章

679瀏覽量

34005

原文標(biāo)題:芯片后仿(一)

文章出處:【微信號(hào):全棧芯片工程師,微信公眾號(hào):全棧芯片工程師】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

LTspice噪聲仿真要點(diǎn)

一文掌握集成電路封裝熱仿真要點(diǎn)

STM32F4系列有對(duì)PI/SI仿真要求的文件嗎?

proteus 7可以仿真msp430f249嗎?哪位大神可以幫我解釋一下,msp430f249仿真要用哪個(gè)版本?感謝

ARM cortex 處理器本身仿真要注意什么

Vivado仿真器進(jìn)行混合語言仿真的一些要點(diǎn)

芯片前仿真和后仿真的區(qū)別

calibre后仿真參數(shù)提取

芯片后仿真deposit的用法簡(jiǎn)析

芯片后仿真要點(diǎn)

芯片后仿真要點(diǎn)

評(píng)論