本文的關鍵要點

?ROHM Solution Simulator仿真可以通過在啟動Solution Circuit后單擊電路圖工具欄上的Run按鈕 ? 啟動。

?單擊Simulation Settings圖標可以進行仿真設置。

?仿真結果可以使用波形查看工具顯示每個節點的信號波形。

本文將介紹如何執行ROHM Solution Simulator仿真。直接進入本文的用戶,請參考“仿真電路的啟動”,來啟動示例的仿真電路。如果希望快速了解操作方法等,請使用“用戶操作手冊(PDF)”。

ROHM Solution Simulator仿真的執行

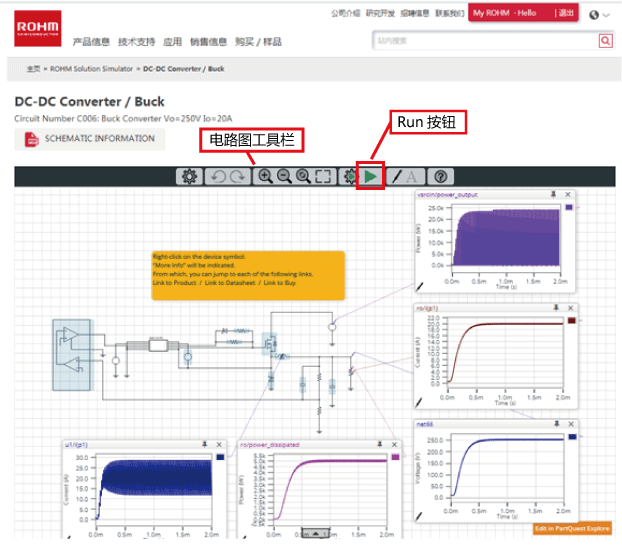

當仿真電路啟動時,將會顯示圖1所示的仿真畫面。要執行仿真,請單擊電路圖工具欄上的Run按鈕 ? 。

圖1. ROHM Solution Simulator仿真的執行

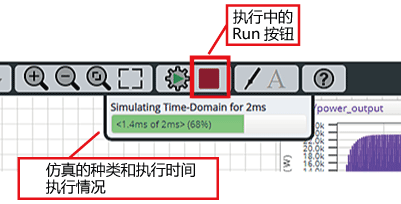

當仿真開始時,Run按鈕 ? 將變為圖2所示的紅色方塊 ■ 。另外,還會打開一個小窗口,顯示正在執行的仿真種類(圖2中的Time-Domain)、執行仿真的時間(圖2中的2ms)以及執行情況。仿真時間(2ms)是設置的時間,不是仿真所需的時間。例如,表示從接通電源到2ms時的電路工作仿真。

圖2. 執行仿真時的電路圖工具欄的顯示狀態

當仿真進度達到100%時,電路圖顯示區的波形會被更新。單擊紅色方塊 ■ 按鈕可暫停仿真。但是,無法從這種暫停狀態下重新啟動。

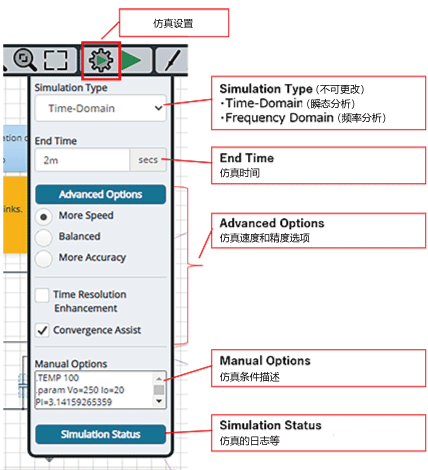

可以通過單擊Simulation Settings圖標來設置仿真(圖3)。仿真設置已經根據所選的仿真電路進行了預設。另外,不能更改Simulation Type。

圖3. 通過Simulation Settings進行的仿真設置

關于仿真結果,可以使用波形查看工具來查看每個節點的信號波形。顯示方法將在下一篇中進行介紹。

審核編輯黃宇

-

仿真

+關注

關注

51文章

4241瀏覽量

135325 -

simulator

+關注

關注

0文章

10瀏覽量

8036

發布評論請先 登錄

Multisim模擬電路仿真教程

《聊一聊ZXDoc》之CAN總線仿真、面板仿真

對齊熱測量與仿真

智能駕駛HIL仿真測試解決方案

功放設計仿真的一般步驟

芯片后仿真要點

機器人仿真的類型和優勢

仿真的時候在哪些地方添加寄生電容呢?

AMI參數掃描與仿真的實際應用和實現方法

仿真-ROHM Solution Simulator 仿真的執行

仿真-ROHM Solution Simulator 仿真的執行

評論