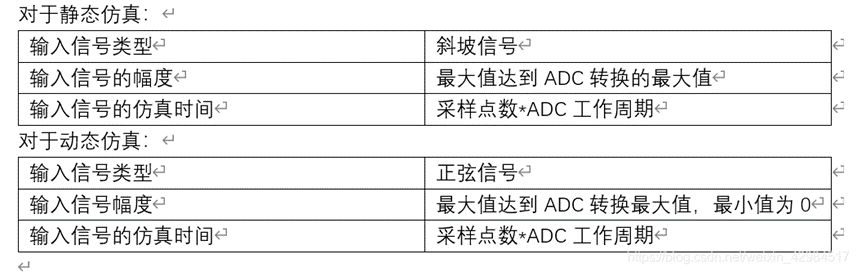

ADC電路主要存在靜態(tài)仿真和動態(tài)仿真兩類仿真,針對兩種不同的仿真,我們存在不同的輸入信號和不同的數(shù)據(jù)采樣,因此靜態(tài)仿真和動態(tài)仿真是完全不同的兩個概念,所以設(shè)置的參數(shù)不同:

靜態(tài)參數(shù)仿真:

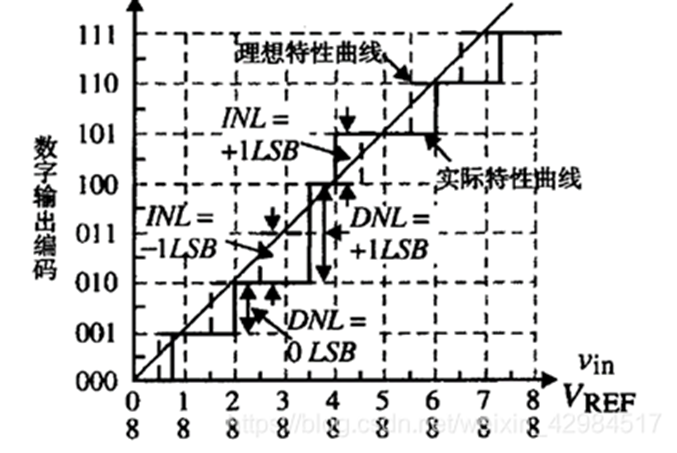

主要參數(shù)為INL DNL

輸入斜坡信號作為激勵

用WavevsWave 繪制出輸入模擬量和數(shù)字編碼之間的關(guān)系。利用calculator中的inl dnl函數(shù)進(jìn)行計算。

動態(tài)參數(shù)仿真:

信噪比(SNR),信號噪聲失真比(SINAD),有效位數(shù)(ENOB),總諧波失真(THD),無雜散動態(tài)范圍(SFDR);

SNR:信噪比是輸入信號和噪聲(不包括任何諧波以及直流) 的功率比,衡量器件內(nèi)部噪聲大小的基本參數(shù)。

SINAD:SINAD是輸入信號和所有輸出信號失真功率(包括諧波成分,不包括直流)比,它測量的是輸出信號所有傳遞函數(shù)非線性加上系統(tǒng)所有噪聲(量化、抖動和假頻)的累積效果。

ENOB: 表示ADC在轉(zhuǎn)換過程中真正輸出有效的位數(shù)。

THD: 總諧波失真是輸入信號與系統(tǒng)所有諧波的總功率比,它可提供系統(tǒng)對稱和非對稱非線性產(chǎn)生的失真大小,用以表達(dá)其對信號的諧波含量的作用或者影響。

SFDR: 表示器件輸入和輸出之間的非線性

第一步:在ADC后面接一個理想的DAC(VerilogA實現(xiàn))。根據(jù)需求修改所需要的位數(shù)。

可以在cadence得ahdLib庫中找到dac_8bit_ideal元件參考

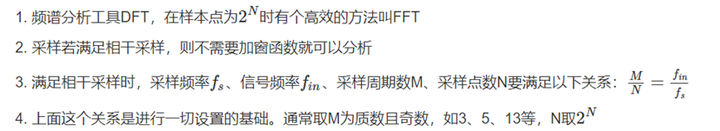

第二步:確定如何加激勵(滿足相干采樣情況下,設(shè)定輸入信號頻率)。

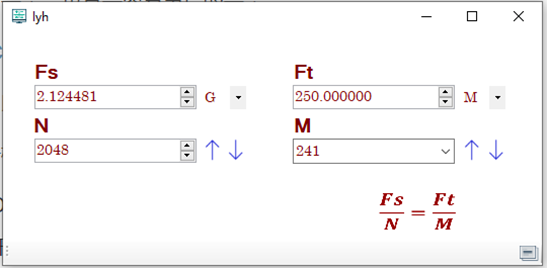

我這里使用編寫得程序進(jìn)行自動計算

下面說明手動計算具體如何實現(xiàn):

1.確定采樣率

設(shè)ADC CLK的周期為40ns,即頻率為25MHz,設(shè)置采樣周期為8CLK,轉(zhuǎn)換周期是12CLK,因此采樣時間間隔為20CLK,從而采樣率為25M/20=1.25MSPS(1.25MHz)

采樣率=CLK的頻率除以(采樣周期+轉(zhuǎn)換周期)

(若采樣周期為4CLK,采樣率為25M/16=1.5625MSPS)

2.確定采樣點N和周期數(shù)M

采樣點取2^n,這樣可以進(jìn)行FFT分析。此處取M=3,N=128

3.確定AC分析的輸入頻率fin=fs*M/N

根據(jù)采樣定理,輸入頻率要小于1.25M/2=0.625MHz=625KHz。若M=3,取N=128,則fin=1.25M*3/128=29.296875KHz

4.確定仿真時間

如果采樣M個周期,每個周期時間1/fin,則:

T=M/fin=N/fs=128/1.25M=102.4us。仿真時,稍微多點時間,保證后面分析時,取數(shù)據(jù)取在非跳變處。比如仿真110us。由這個公式也可以看出,在采樣率確定的情況下,N越大需要的仿真時間越長,而與輸入信號頻率無關(guān)。

接下來就是在電路圖做好設(shè)置,就可以仿真啦。

如果仿真時間比較長,比如取4096個點,那仿真時間可能無法接受。可以考慮使用多核

在ADE窗口中:Setup>Environment,彈出如下窗口,加上:

+mt=20 +aps

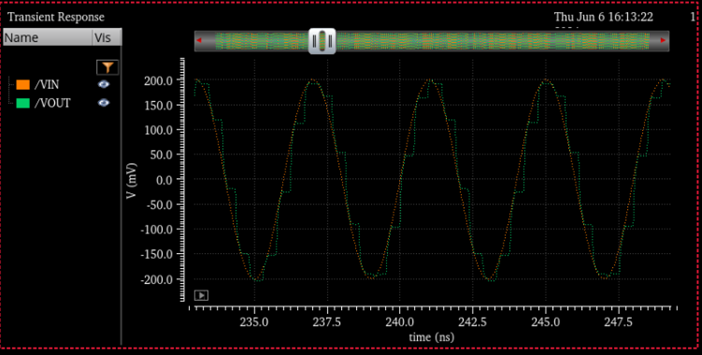

仿真完成后,波形大概如下:

從圖中可以看出,正弦信號經(jīng)過ADC轉(zhuǎn)換,再經(jīng)過理想DAC的轉(zhuǎn)換,基本靠譜。

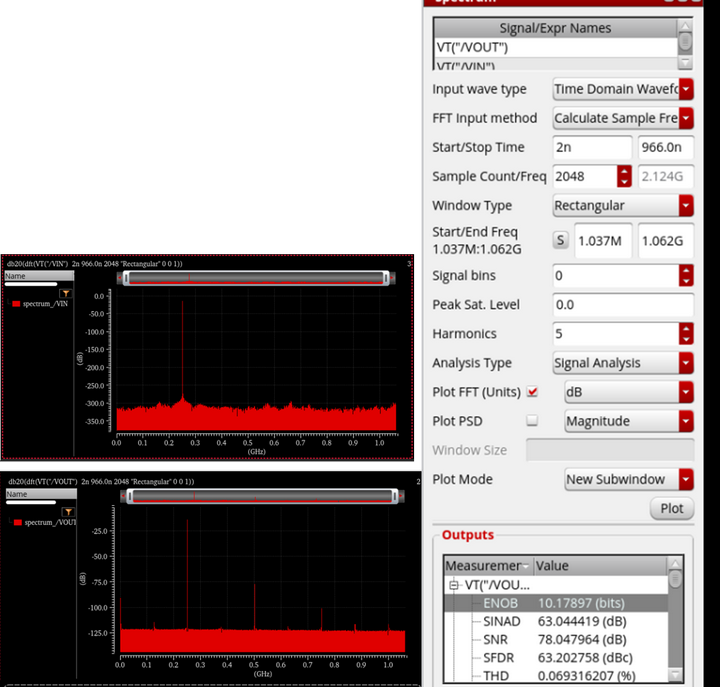

第三步:設(shè)置參數(shù)并查看結(jié)果

得到瞬態(tài)仿真波形后,接下來就是對信號進(jìn)行頻譜分析。

分析方法可以采用:

1. Cadence Spectrum工具2.MATLAB計算

下面說明在利用cadence的spectrum工具進(jìn)行參數(shù)分析

開始時間:t0,結(jié)束時間:t0+M/ft

2.MATLAB計算

選中仿真出的輸出信號波形-右鍵-send to-export,

選擇格式為csv,start從一個穩(wěn)定時刻開始,end默認(rèn)就可以,step就是1/fs,比如50M,step就是20n,然后導(dǎo)出文件。

打開matlab代碼main,修改讀取的文件,運行得到ADC的輸出頻譜圖及相關(guān)動態(tài)性能參數(shù)值。

-

matlab

+關(guān)注

關(guān)注

188文章

2998瀏覽量

233463 -

adc

+關(guān)注

關(guān)注

99文章

6656瀏覽量

548489 -

仿真

+關(guān)注

關(guān)注

51文章

4249瀏覽量

135415 -

函數(shù)

+關(guān)注

關(guān)注

3文章

4372瀏覽量

64365

原文標(biāo)題:ADC參數(shù)仿真

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設(shè)計論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

Protel DXP 的電路仿真設(shè)計

靜態(tài)、動態(tài)時序模擬的優(yōu)缺點

如何對數(shù)碼管的靜態(tài)顯示和動態(tài)顯示進(jìn)行Proteus仿真呢

LTspice的瞬態(tài)仿真為什么先計算電路的靜態(tài)工作點?

機構(gòu)動態(tài)仿真

MATLAB通信仿真及應(yīng)用實例詳解

基于multisim調(diào)頻仿真電路圖及波形圖詳解

詳解ADC電路的靜態(tài)仿真和動態(tài)仿真

詳解ADC電路的靜態(tài)仿真和動態(tài)仿真

評論