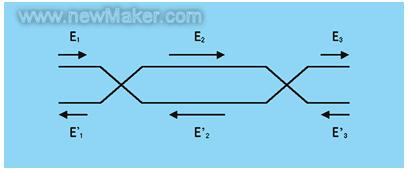

PCB板的設計中 ,隨著頻率的迅速提高 ,將出現與低頻 PCB板設計所不同的諸多干擾 ,并且 ,隨著頻率的提高和PCB板的小型化和低成本化之間的矛盾日益突出 ,這些干擾越來越多也越來越復雜。在設計中,采用抗干擾的措施很多,其中常用的措施有以下三條。

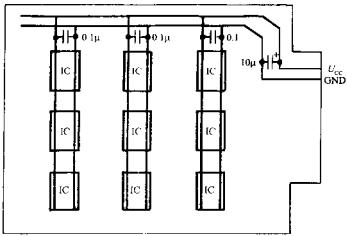

在電子設備中,接地是控制干擾的重要方法。若能將接地和屏蔽正確結合起來使用,可解決大部分干擾問題。電子電路的接地方式通常分為單點接地、多點接地兩種。單點接地也稱一點接地,電路中只有一個接地點,可使共地阻抗降到最低,其抗共地干擾性能也最佳,通常適用于直流和低頻電路;多點接地可使電路中各條地線長度減到最短,故能有效地防止因地線電感及電容引起的干擾。由于各級電路采用多點接地,當地線阻抗較大時,會產生較嚴重的共地干擾現象。通常適用于高頻電路,在直流和低頻電路中也應用較多。

選擇接地線類型時,應根據信號頻率的高低及電路的類型采用不同的接地方式。當印制電路板上信號頻率小于1MHz,由于布線和元器件之間的電磁感應影響很小,而接地電路形成的環流對于擾的影響較大,所以要采用一點接地,使其不形成回路;當信號頻率離于10MHz時,由于布線的電感效應明顯,地線阻抗變得很大,此時接地電路形成的環流就不再是主要問題了,所以應采用多點接地,盡量降低地線阻抗;當印制電路板上工作頻率為1~10MHz時,如果采用一點接地,其地線長度不應超過波長的1/20,否則應采用多點接地法。

對于印制電路板上既有數字電路,又有模擬電路,應使它們盡量分開,而且兩者的地線不要相混,分別與電源端地線相連,而且盡量加大模擬電路引出端的接地面積。如果地線很細的話,則地線電阻將會較大,造成接地電位隨電流的變化而變化,致使信號電平不穩,導致電路的抗干擾能力下降。因此應將接地線盡量加粗,在布線空間允許的情況下,要保證主要地線的寬度至少為2mm,元件引腳上的接地線應該在1.5mm左右。

-

pcb

+關注

關注

4340文章

23330瀏覽量

404545 -

電子設備

+關注

關注

2文章

2858瀏覽量

54392 -

頻率

+關注

關注

4文章

1552瀏覽量

59846

發布評論請先 登錄

相關推薦

在電路設計中抗干擾的措施有哪些

在電路設計中抗干擾的措施有哪些

評論