支持SystemC的電子系統(tǒng)級(ESL)設(shè)計和驗證環(huán)境旨在設(shè)計,分析,優(yōu)化和驗證片上系統(tǒng)(SoC)平臺模型。這樣的環(huán)境構(gòu)成了已建立的RTL實現(xiàn)流程的前端。

現(xiàn)在,您為什么要關(guān)心?

根據(jù)Gartner DataQuest的說法,SystemC設(shè)計和驗證環(huán)境被用作設(shè)計流程前端用于約2003年的約100個SoC設(shè)計。其中許多設(shè)計是世界領(lǐng)先的SoC設(shè)計公司的旗艦產(chǎn)品。

根據(jù)最近發(fā)布的材料,德州儀器使用SystemC ESL設(shè)計方法設(shè)計和開發(fā)其OMAP處理器和調(diào)制解調(diào)器平臺,STMicroelectronics使用它來設(shè)計其Nomadik應(yīng)用處理器。此外,諾基亞和高通等領(lǐng)先的系統(tǒng)設(shè)計公司正在建立面向SystemC的設(shè)計流程。

但為什么所有這些領(lǐng)先的公司都采用SystemC方法?是什么促使公司使用SystemC ESL設(shè)計增強其現(xiàn)有的設(shè)計方法?換句話說,您如何決定是否需要SystemC ESL設(shè)計方法?

當您遇到以下任何問題時,應(yīng)考慮使用SystemC ESL設(shè)計:

1。當您的SoC部署采用多個嵌入式微處理器和DSP來實現(xiàn)融合功能時,例如通信和/或多媒體?復(fù)雜的體系結(jié)構(gòu),功能和協(xié)議的設(shè)計陷入了大量耗時的RTL細節(jié)。

SystemC ESL設(shè)計方法可以將架構(gòu)設(shè)計時間從幾個月縮短到幾周。如何?

優(yōu)化SoC架構(gòu)需要探索和分析多個候選硬件/軟件分區(qū)方案和硬件架構(gòu),每個方案都有不同的性能和經(jīng)濟權(quán)衡。在這個階段,SoC架構(gòu)師關(guān)注的是開發(fā)和優(yōu)化系統(tǒng)行為和架構(gòu)。

但RTL的引腳精確連接和納秒精確的時序細節(jié)模糊了系統(tǒng)范圍的視圖,并大大減慢了設(shè)計速度。使用這種低生產(chǎn)率的方法,設(shè)計師偶爾會選擇“無論什么工作”,而不是設(shè)計“什么效果最好”?并冒險推出一項缺乏競爭力的產(chǎn)品。國際商業(yè)戰(zhàn)略(IBS)對領(lǐng)先的SoC公司進行的一項調(diào)查預(yù)測,SoC架構(gòu)開發(fā)工作將很快超過物理設(shè)計工作,因此這種生產(chǎn)力問題有望變得更加糟糕。

SystemC ESL設(shè)計速度復(fù)雜硬件/軟件分區(qū)和硬件架構(gòu)開發(fā)通過執(zhí)行比RTL更高的抽象級別,僅使用與系統(tǒng)設(shè)計相關(guān)的那些設(shè)計屬性。這是“設(shè)計意圖”被最有意義地捕獲的水平?為SoC架構(gòu)師提供直接和清晰的系統(tǒng)行為視圖的水平。

SoC架構(gòu)采用SystemC IP模塊設(shè)計,通過應(yīng)用程序接口(API)連接到與實現(xiàn)無關(guān)的高級總線模型。使用事務(wù)級建模(TLM),該體系結(jié)構(gòu)在功能方面進行設(shè)計和驗證,其特征在于高級塊輸入和輸出事件以及塊間數(shù)據(jù)傳輸。

系統(tǒng)IP組件和總線可以比RTL更容易修改或更換,模擬速度提高1000多倍。因此,設(shè)計人員可以快速優(yōu)化設(shè)計,以實現(xiàn)“最佳效果”。

最終優(yōu)化架構(gòu)的TLM模型構(gòu)成了一個“可執(zhí)行規(guī)范”,可驅(qū)動整個后續(xù)RTL實現(xiàn)。

2。當完整的系統(tǒng),功能驗證消耗了更大的設(shè)計時間和預(yù)算?你仍然對第一次通過成功沒有信心。

設(shè)計師報告說,SystemC ESL設(shè)計可以減少驗證時間,使整體設(shè)計和驗證工作減少50% ,并確保第一次是正確的。事實上,當設(shè)計團隊首次使用SystemC ESL設(shè)計來設(shè)計和開發(fā)SoC時,這是投資回報率中的最大因素。 SystemC ESL設(shè)計如何提供這一價值?

RTL驗證始于設(shè)計人員對系統(tǒng)級行為的全面解釋,包括大量的塊內(nèi)電路狀態(tài)和納秒精確的轉(zhuǎn)換,以及相關(guān)的比特精確的總線行為。然后,需要定義執(zhí)行這些行為的大量詳細場景,并為這些場景創(chuàng)建眾多刺激/預(yù)期響應(yīng),然后進行模擬,通常以實際芯片速度的百萬分之一執(zhí)行。

這就是為什么隨著SoC復(fù)雜性的增加,驗證會消耗不斷增加的設(shè)計時間。然后將驗證的RTL設(shè)計轉(zhuǎn)移到合成。但是如果全面的解釋不夠全面呢?

SystemC ESL設(shè)計自動化SoC架構(gòu)的開發(fā),并根據(jù)高級塊輸入和輸出事件以及塊間數(shù)據(jù)傳輸來驗證行為,交易級別。這種系統(tǒng)級行為的直接視圖消除了手動RTL到系統(tǒng)行為的解釋,這種解釋太容易不夠全面,并且顯著減少了所需場景的數(shù)量和測試它們所需的刺激/響應(yīng)。

消除如此多的任務(wù)大大簡化了驗證工作和時間。此外,周期精確的TLM仿真執(zhí)行速度比RTL快1000倍。

最終的系統(tǒng)級功能測試平臺構(gòu)成了“黃金”驗證套件,可確保RTL設(shè)計符合規(guī)范。此外,SystemC與RTL的協(xié)同仿真功能使驗證團隊能夠?qū)oC的TLM模型用作測試平臺,以便在RTL塊可用時對其進行驗證。

3.當市場生存需要你以類似消費者的速度旋轉(zhuǎn)原始SoC設(shè)計的多個衍生物?并且你迫切希望提高設(shè)計效率。

設(shè)計師報告說,SystemC ESL設(shè)計可以將衍生物的旋轉(zhuǎn)時間減少多達75%。實際上,衍生設(shè)計是SystemC ESL設(shè)計的生產(chǎn)力對ROI影響最大的地方。如何?

衍生設(shè)計旨在維護SoC平臺的基本架構(gòu)和行為,同時增強或添加所選功能。傳統(tǒng)方法是圍繞第一個SoC選擇的處理器建立基線RTL平臺,然后通過“混合和匹配”適當?shù)腞TL IP來設(shè)計衍生產(chǎn)品,以實現(xiàn)所需的新功能。

問題在于“混合搭配”意味著RTL IP模型從未實現(xiàn)的“即插即用”程度,因為它們過于復(fù)雜。通常,衍生設(shè)計幾乎與“干凈”設(shè)計一樣困難。

同樣,SystemC ESL設(shè)計解決了這個問題。 IP模型實際上可以在SoC平臺的SystemC TLM中“混合和匹配”。使用SoC設(shè)計的其余部分快速模擬新的SystemC IP,并且經(jīng)過驗證的衍生SoC的TLM模型可以用作測試平臺,其中可以共同驗證新IP的RTL視圖。

4.當SoC性能和/或低功耗可以決定你的市場地位?并且調(diào)整RTL設(shè)計無法提供所需的改進。

SystemC ESL設(shè)計可以提供更高的性能,并且比RTL優(yōu)化所實現(xiàn)的功耗節(jié)省10倍至20倍。怎么樣?

SoC性能主要由硬件/軟件分區(qū),處理器,總線和存儲器的速度以及它們的通信協(xié)議決定。這些系統(tǒng)組件和屬性無法在RTL中進行調(diào)整。 SystemC ESL設(shè)計使設(shè)計人員能夠設(shè)計出最佳的硬件/軟件分區(qū),硬件架構(gòu)和協(xié)議,從而最大限度地提高SoC性能。

處理器,存儲器和相關(guān)總線活動消耗高達80%的SoC功率,以及因此,硬件/軟件分區(qū)以及軟件算法和數(shù)據(jù)存儲的效率受到很大影響。同樣,這些系統(tǒng)組件和屬性無法在RTL中進行調(diào)整,因此RTL調(diào)整最多可以在剩余的20%中進行漸進式改進。

功耗優(yōu)化內(nèi)存包括最小化內(nèi)存訪問次數(shù)和定制給定應(yīng)用程序的內(nèi)存架構(gòu)。將高使用率的內(nèi)存訪問集群到一個單獨的優(yōu)化緩存中可以簡化內(nèi)存事務(wù),從而降低功耗(并且通常可以提高SoC性能),因此緩存內(nèi)存架構(gòu)對功耗至關(guān)重要。

SystemC ESL設(shè)計直接和即時查看內(nèi)存訪問以及與之相關(guān)的活動,可以實現(xiàn)緩存命中率與緩存大小之間的直接關(guān)聯(lián),以及用于確定最佳內(nèi)存大小的軟件甘特圖。從函數(shù)調(diào)用與內(nèi)存訪問頻率的相關(guān)性中識別算法優(yōu)化候選。

5.當您的系統(tǒng)客戶需要早期SoC模型以使他們能夠完成他們的設(shè)計并贏得設(shè)計時??他們不能等到RTL設(shè)計完成。

在無線通信中經(jīng)常出現(xiàn)這種情況,這也是全球最大的寓言半導(dǎo)體公司之一Qualcomm的原因之一已經(jīng)在SystemC上實現(xiàn)了標準化。

系統(tǒng)設(shè)計人員在芯片可用性之前通常需要SoC模型來驗證整個系統(tǒng)設(shè)計的進展情況,并贏得客戶的早期批準。此階段的驗證使系統(tǒng)設(shè)計人員能夠在完成原型硬件之前檢測并糾正系統(tǒng)不合格或徹底的故障,從而消除昂貴且耗時的硬件重制。

以及“遲到”,RTL模型并不是特別適合這個目的,因為它的實際芯片速度的百萬分之一的驗證速度減慢了系統(tǒng)模擬的速度。并且系統(tǒng)設(shè)計人員不一定知道如何調(diào)試RTL。

SystemL TLM模型在RTL實現(xiàn)之前幾個月就可用,它封裝了系統(tǒng)感興趣的所有系統(tǒng)級行為和屬性。設(shè)計師,執(zhí)行速度比RTL快1000倍。因此,它不僅滿足系統(tǒng)設(shè)計人員對早期SoC模型的需求,而且還在系統(tǒng)設(shè)計者最熟悉的抽象層次上執(zhí)行。

6.當您僅開始軟件開發(fā)時原型可用?產(chǎn)品發(fā)布的軟件和軟件完成。

在嵌入式軟件中實現(xiàn)了超過50%的SoC功能,這正成為SoC設(shè)計的起搏項目。 IBS調(diào)查預(yù)測嵌入式軟件開發(fā)工作將很快超過SoC硬件設(shè)計工作,因此問題變得更加嚴重。軟件開發(fā)人員必須在RTL設(shè)計完成之前開始有效工作。

使用外設(shè)“存根”的先前軟件開發(fā)方法不再能夠充分代表現(xiàn)代的多處理器,多總線架構(gòu)。如果沒有早期的SystemC TLM原型,該軟件的開發(fā)完全獨立于硬件團隊設(shè)計,從而產(chǎn)生了顯著的集成風險。在設(shè)計過程的尾端進行集成使得上市時間變得非常難以預(yù)測。

使用FPGA原型來實現(xiàn)早期的軟件和系統(tǒng)硬件集成只能適度地改善計劃,因為這樣的原型仍然來得太晚。在這個階段,RTL設(shè)計發(fā)生了變化?甚至是次要的?整合所遇到的問題需要非常耗時。

同樣,SystemC TLM原型可以在幾個月前開始有效的軟件開發(fā)。可以將與硬件相關(guān)的軟件(例如RTOS)移植到模型中,而無需連接各個引腳。應(yīng)用軟件 ??這與硬件無關(guān)?可以使用TLM作為數(shù)據(jù)流模型開發(fā)和移植。

7.當使用RTL原型協(xié)同驗證軟件太慢時,您無法驗證是否有足夠的信心確保沒有錯誤。

Qualcomm舉了一個這個問題的例子。維特比解碼器在20ms內(nèi)執(zhí)行一個數(shù)據(jù)包,但需要6個小時來模擬C/RTL級別。 Qualcomm估計必須模擬1,000個數(shù)據(jù)包以達到合理的置信水平,但認為必要的6000小時的模擬時間是不切實際的。

SystemC ESL設(shè)計可以與硬件相關(guān)的軟件共同驗證硬件架構(gòu)比RTL快1000倍以上,具有周期精度。維特比解碼器可在不到6小時內(nèi)驗證,而不是6,000小時。通過使用定時和協(xié)議無關(guān)的仿真,可以更快地共同驗證與硬件無關(guān)的軟件,例如應(yīng)用軟件。

8.當您的團隊想要建立或已經(jīng)維護時這是一個本土化的系統(tǒng)級設(shè)計環(huán)境,它將重要的工程資源和預(yù)算從創(chuàng)收設(shè)計中轉(zhuǎn)移出來。

構(gòu)建和維護自行開發(fā)的ESL設(shè)計環(huán)境既昂貴又不提供戰(zhàn)略分化。自行開發(fā)的ESL設(shè)計環(huán)境與本土邏輯綜合或布局布線工具一樣具有經(jīng)濟意義?

此外,許多歷史悠久的ESL設(shè)計環(huán)境利用C或C ++方言,與SystemC不同,它們不具備描述真實所需的時間,位精度和并發(fā)性概念。 RTL設(shè)計人員和嵌入式軟件開發(fā)人員所需的世界行為和性能。更糟糕的是,沒有標準的C/C ++建模方法,導(dǎo)致缺乏可用的模型,難以共享和重新使用那些可用的模型。

這兩個問題的解決方案是部署商用的SystemC ESL設(shè)計環(huán)境。提供商確保該工具和您始終處于SoC設(shè)計自動化的前沿。

9.當您在日程安排上失眠,第一次成功,設(shè)計和掩蓋成本超過跑?你想知道如何繼續(xù)與其他領(lǐng)先的SoC公司競爭。

解決方案很簡單。采用與領(lǐng)先的SoC設(shè)計人員已經(jīng)使用的相同的SystemC ESL方法。

電子系統(tǒng)級設(shè)計和驗證方法的采用正在加速。 ESL設(shè)計工具的需求受復(fù)雜多處理器設(shè)計的挑戰(zhàn)驅(qū)動,其中一半以上的功能在嵌入式軟件中實現(xiàn),而SystemC則使ESL設(shè)計得以快速采用。

今年將遠遠超過使用ESL設(shè)計方法的100個SoC設(shè)計。這種方法最終超越了它的采用鴻溝,因為SoC設(shè)計遇到了自己的鴻溝?系統(tǒng)級設(shè)計生產(chǎn)力鴻溝。

Mark Creamer是CoWare公司的副總裁。

-

soc

+關(guān)注

關(guān)注

38文章

4348瀏覽量

221762 -

ESL

+關(guān)注

關(guān)注

1文章

76瀏覽量

21636 -

systemc

+關(guān)注

關(guān)注

2文章

25瀏覽量

14717

發(fā)布評論請先 登錄

如何在ModelSim下用SystemC的做驗證?

如何基于uvm方法學(xué)采用systemc進行IC驗證?

ARM RealView ESL API v2.0開發(fā)人員指南

Systemc From The Ground Up

基于SystemC事務(wù)級的建模仿真研究

在SoC設(shè)計中采用ESL設(shè)計和驗證方法

片上網(wǎng)絡(luò)的SystemC建模研究

ESL設(shè)計的流程是什么

ESL設(shè)計的特點有哪些

SystemC中的模塊與進程

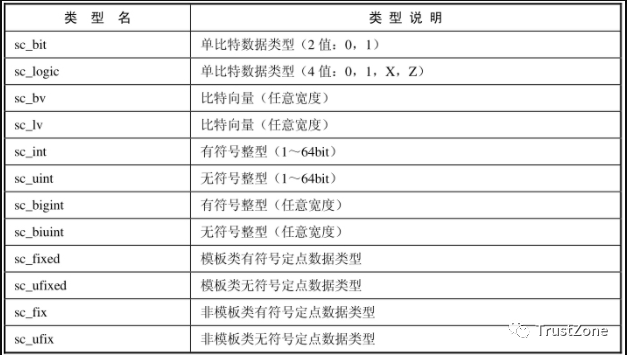

SystemC中的數(shù)據(jù)類型概念

采用SystemC ESL設(shè)計的九個理由

采用SystemC ESL設(shè)計的九個理由

評論