很久之前遇到一個問題,就是一塊電路板沒有全部敷銅,只敷銅了一小部分,但是其它未敷銅的地方還是有GND連接。

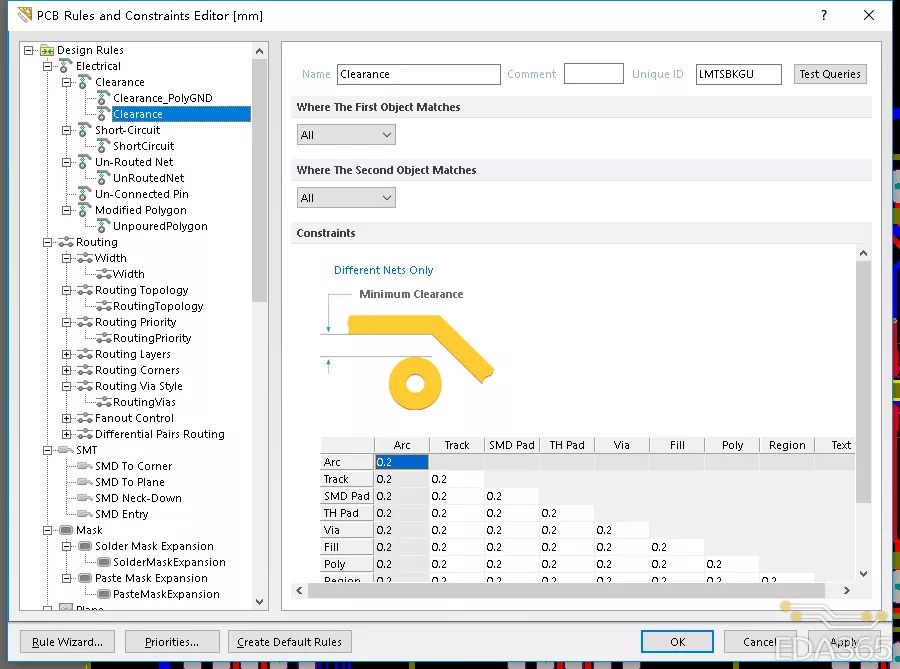

然后我直接用Track將未敷銅的Object連接到GND敷銅上去,但是重新敷銅之后發現敷銅與連線斷開了,因為規則規定了Track與Poly的間距:

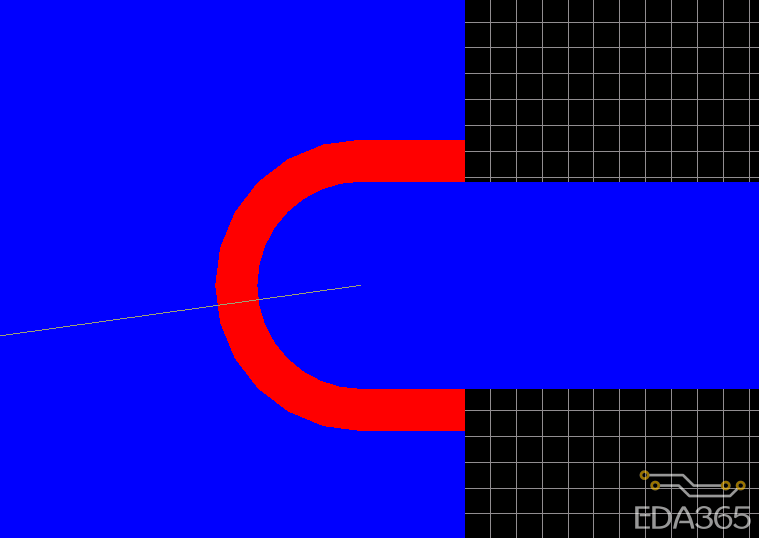

可以看到規則規定了Track與Poly的間距為0.2mm,所以Repour Polygon之后就會有下面的現象:

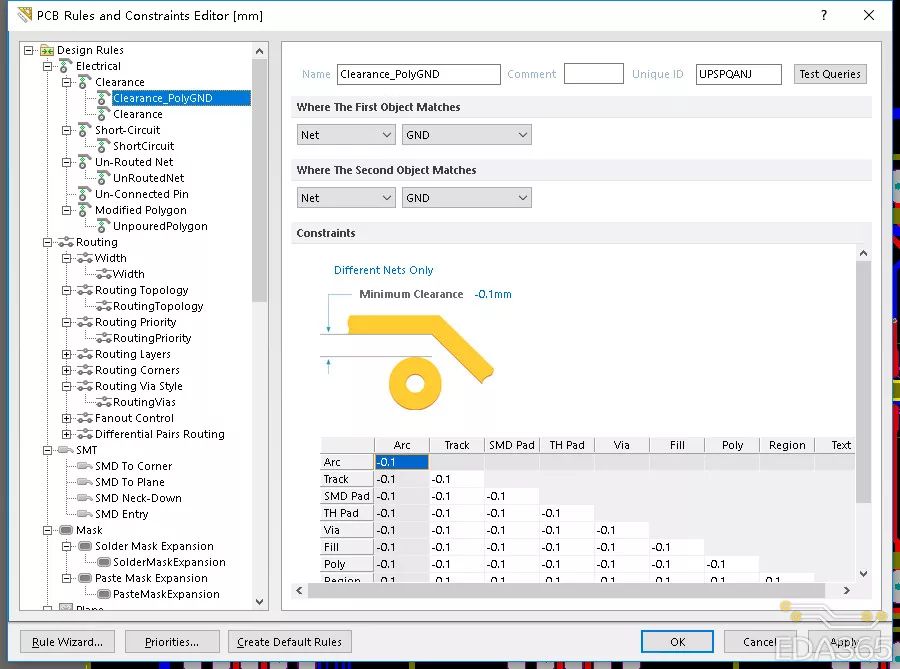

我們可以在Clearence下新建一個規則,取名叫Clearance_PolyGND,然后設置Where The First Object Mathces為Net-GND,Where The second object Matches也為Net-GND,意思就是這個規則所應用在的目標物體都選擇為GND網絡,然后設置Minimum Clearance為-0.1mm,如果設置為0mm的話,重新敷銅之后還有有點間隙,設置成負數之后重新敷銅就會完全連接,但是這個負數的絕對值不能太大,你可以試試。設置如下:

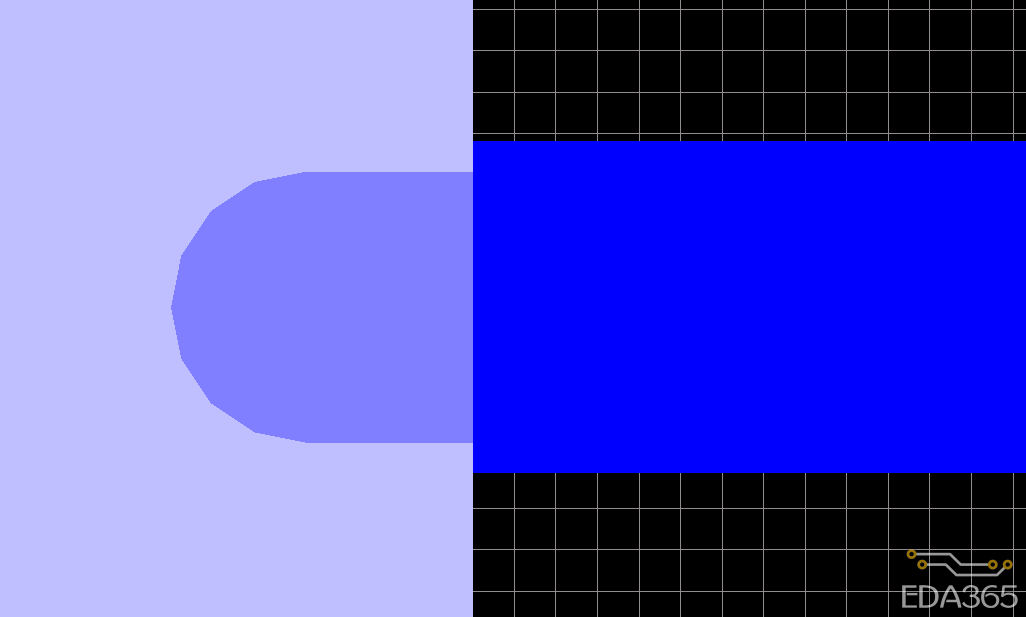

設置完之后重新敷銅:

可以看出來敷銅和右側的Track完全連接在一起并且已經“伸進去”了一點,這“伸進去”的長度就是|-0.1|mm,是不是很神奇,原來AD的規則還能這樣用!其實這是最簡單的用法,AD的規則還能使用Query來查找匹配,和腳本一樣,功能十分強大!!

-

AD

+關注

關注

27文章

869瀏覽量

150592 -

GND

+關注

關注

2文章

540瀏覽量

38922

原文標題:領福利啦!丨EDA365:電巢APP全國招募“體驗官”

文章出處:【微信號:eda365wx,微信公眾號:EDA365電子論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

PADS9.5:Rules_1——Clearance

密集元件組成的PCB怎樣設置規則DRC規則?

請問在哪里可以設置外設寄存器的user和privilege模式?設置的過程應該遵循怎樣的規則?

差分對線距規則設置為6mil是因為在clearance中設置最小間隔為10mil就會報錯嗎?

鋪銅和Clearance規則的優先級

【Altium小課專題 第114篇】不同元素之間的間距規則如何進行設置?

pcb覆銅規則設置

PCB設計的線寬線距與孔徑規則設置注意事項

AD學習問題記錄(二):pcb設計規則檢查報錯Silk To Solder Mask Clearance Constraint

怎樣操作AD設置Clearance規則

怎樣操作AD設置Clearance規則

評論