IMEC提出了一種扇形晶圓級封裝的新方法,可滿足更高密度,更高帶寬的芯片到芯片連接的需求。 IMEC的高級研發工程師Arnita Podpod和IMEC Fellow及3D系統集成計劃的項目總監Eric Beyne介紹了該技術,討論了主要的挑戰和價值,并列出了潛在的應用。

晶圓級封裝: 適用于移動應用的有吸引力的封裝解決方案

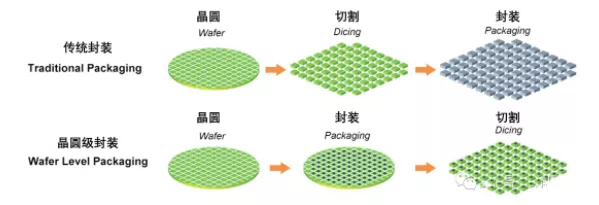

如今,許多電子系統仍然由多個元件組成,這些元件在芯片切割后單獨封裝,并且使用傳統的印刷電路板互連。 然而,這些年來,對于更“苛刻”的應用就需要先進的3D集成和互連技術。 因為這大大減小了電子系統的尺寸,并且實現了子電路之間更快,更短的連接。 這些技術之一是晶圓級封裝(Wafer Level Packaging),即多個裸片在晶圓上同時被封裝。 由于整個晶圓現在是一次性封裝,因此該解決方案比傳統封裝方案成本更低。 此外,所得封裝后芯片尺寸更小,更薄,這是智能手機等尺寸敏感設備非常看重的。 在現今的智能手機上,大概5/7的芯片是晶圓級封裝的,而且數量還在不斷增加。

扇入和扇出

有兩種主要類型的晶圓級封裝: 扇入式和扇出式,它們的區別主要在重分布層中。 重分布層(通常是有機層)用于將裸片的接口(I/ O)重新布線到所需的(凸塊)位置。 扇入就是重分布層跡線向內布線,形成一個非常小的封裝(大致對應于裸片本身的尺寸)。 但是,重分布工藝還可以用于擴展封裝的可用區域,延伸芯片觸點到超出芯片尺寸就形成了扇出式封裝。 通常,這種扇出WLP(FO-WLP)技術提供比扇入式WLP技術更多的I /O數量。

在移動應用中,扇出晶圓級封裝正在逐步取代更傳統的封裝上封裝(PoP)存儲器邏輯芯片堆疊解決方案。

這些PoP比扇出式厚得多,并且受到的互連帶寬和密度以及有限的間距縮放(幾百微米)的限制。 在這些應用中,FO-WLP也優于其他可用的高帶寬3D技術,例如3D堆疊(其中邏輯管芯中的熱點可能影響存儲器數據保持能力)或2.5D堆疊(其中較長的互連線產生較高的互連功率和額外成本)。

兩個基本的“扇出”流程

在過去幾年中,已經涌現了各種FO-WLP方法,以滿足對高數據速率和寬I/ O數量的日益增長的需求,并滿足對封裝上增加的功能集成的需求。 所有這些方法都從兩個基本的扇出流程中的一個開始: “mold first”或“redistribution layer first”。

在“mold first “工藝中,首先將裸片組裝在臨時載體上,然后進行芯片包覆成型。 環氧樹脂的功能是保護各個組件并將它們粘在一起。 在最后,制作重分部層并建立連接。 在“redistribution layer first”工藝中,在重分布層的工藝之后再做裸片組裝和芯片注塑成型。

這些方法中的每一種都有其自身的一些缺點。 例如,在“mold first “工藝中,裸片通常在注塑成型之后發生移位,這使得實現低于100μm的互連節距非常具有挑戰性。 “redistribution layer first”工藝中,可實現的密度受到(有機)再分布層能夠實現的線和空間分辨率的限制。

Flip-chip on FO-WLP: 一種新的“扇出”方法,可實現更高的互連密度

為了滿足更高密度,更高帶寬的芯片到芯片連接的需求,IMEC團隊在300mm晶圓上開發了一種新穎的FO-WLP方法,稱為Flip-chip on FO-WLP。

這個工藝屬于“mold first ”工藝,但與標準的“mold first ”工藝相反,芯片在包覆成型之前已經互相連接。

下面將解釋這種方法的優點以及挑戰。

關鍵部件: through package vias(TPV)和硅橋

這種新的扇出方案的已經在TQV上得到驗證。 TQV由七個獨立的芯片組件組成: Wide I / O DRAM,閃存,邏輯,兩個TPV裸片和兩個硅橋。 因為這個TQV只是用于驗證。 因此,邏輯和存儲器芯片不是全功能的: 它們是“模擬”裸片,用于測試凸點連接之間的電連續性。

硅橋和TPV裸片是實現高密度連接的關鍵部件。 TPV裸片具有硅通孔(TSV)和40μm節距的凸點。 硅橋具有40μm和20μm節距的凸塊。 這些元件在功能芯片(例如邏輯和存儲器芯片)之間形成橋接,實現具有20μm凸塊節距的超高芯片到芯片互連密度。

與標準“mold first “工藝相比,另一個關鍵工藝是裸片間的緊密對準。 在該關鍵組裝步驟中,需要將各個裸片高精度地放置并臨時鍵合在平坦的硅晶圓上。

Flip-chip on FO-WLP芯片概念圖

工藝流程細節

在組裝工藝流程的第一步驟中,將TPV片和邏輯裸片放置在覆有臨時鍵合層的載體芯片上。 接下來,使用熱壓接合(TCB)工藝連接硅橋(具有40μm和20μm的凸塊間距)與邏輯裸片和TPV裸片。 在該工藝步驟中,具有40μm節距的凸塊連接到邏輯裸片的左側和TPV裸片。 20μm間距凸塊連接到邏輯裸片的右側。 在下一步驟中,芯片由液態化合物注塑成型。 測試顯示完全填充,甚至是硅橋下方區域。 然后,通過研磨拋光暴露銅柱,以便稍后與重分布層連接。 在將減薄的芯片翻轉并第二載體鍵合,并移除第一載體。 之后,使用倒裝芯片技術組裝存儲器裸片。 最后,再一次晶圓級注模和第二載體的移除完成工藝流程。 在工藝步驟之間,會進行連續性測試以驗證電路完整。 最后得到封裝厚度僅為300-400μm的芯片(不包括焊球)。

Flip-chip on FO-WLP芯片: 封裝工藝流程

圖示了裸片放置和橋接之后的步驟5至8(左); (中)在注塑和背面研磨之后和(右)暴露的Cu柱在封裝體表面上

最終的第二晶圓級成型之后的橫截面

主要挑戰和解決方案

這套工藝流程帶來了一系列挑戰,需要克服這些挑戰才能確保具有超高芯片到芯片互連密度的全功能封裝解決方案。

其中一個問題是在組裝工藝流程中裸片可能傾斜,特別是對于長而窄的TPV裸片和硅橋。 這些裸片的傾斜可能會破壞組件之間的互連。 為了評估傾斜是否以及何時發生,IMEC團隊采用不同的力量來放置TPV裸片。 該團隊觀察到,即使是最大的貼裝力,傾斜也限制在5μm以下,這足夠低以保持連接性。

接下來是,邏輯裸片和TPV裸片之間的對準,這已經引起了相當大的關注,并且被認為是FO-WLP工藝的關鍵因素。

邏輯裸片和TPV裸片彼此靠的非常近,并且需要精確的對準步驟以實現后續的硅橋40μm和20μm凸塊節距堆疊。 例如,為了實現所需的20μm凸塊間距,僅可以容忍邏輯裸片和TPV裸片之間的最大+/-3μm的對準誤差。 為了實現這種極小的誤差,該團隊將對準標記引入到載體和裸片設計中。 邏輯裸片首先與載體對準。 接下來,放置TPV裸片,與載體對準因此與邏輯管芯對準。 最后,使用高精度堆疊熱壓鍵合設備來放置硅橋。

硅橋連接鍵合到邏輯裸片上的示例

在隨后的模制過程中,裸片仍然會移位,從而損壞TPV和硅橋之間或邏輯裸片和硅橋之間的凸塊連接。 因此,IMEC團隊在成型之前和之后進行了專門的電氣測試。 測試表明,模塑過程不會影響連接的完整性。 基于這些結果,可以假設,如果這些裸片在注塑時移位,它們應該是在相同的方向上作整體位移,因而不會破壞連接性。

總結和未來展望

通過這種新穎的方法,IMEC團隊在扇出環境中展示了具有20μm凸塊節距的創紀錄的芯片到芯片互連密度。 在不久的將來,該技術將得到進一步改進,電氣和射頻行為將以不同的配置進行評估。

所提出的技術對于移動應用尤其具有吸引力,因為它以非常小的形狀因子實現了經濟有效的WideI / O存儲器到邏輯芯片互連。

最終,FO-WLP上的倒裝芯片也可能成為異構集成的支持技術,瞄準高性能應用。 它可以提供一種在電氣高度互連的封裝中集成多個裸片的方法,包括高性能計算,存儲器和光通信模塊。

-

電路板

+關注

關注

140文章

5136瀏覽量

102665 -

晶圓

+關注

關注

53文章

5165瀏覽量

129805 -

封裝

+關注

關注

128文章

8685瀏覽量

145514

發布評論請先 登錄

HRP晶圓級先進封裝替代傳統封裝技術研究(HRP晶圓級先進封裝芯片)

功率型LED熱阻測量的新方法

imec提出以亞微米像素尺寸分離顏色的新方法賦能CMOS圖像傳感器

IMEC提出扇形晶圓級封裝的新方法

IMEC提出扇形晶圓級封裝的新方法

評論