深圳市華芯邦科技有限公司 (李振寧,李昊)

近年來,隨著晶圓級封裝技術的不斷提升,眾多芯片設計及封測公司開始思考并嘗試采用晶圓級封裝技術替代傳統封裝。其中HRP(HeatRe-distributionPackaging)晶圓級先進封裝工藝技術的研究,由深圳市華芯邦科技有限公司(Hotchip)提出,可解決元器件散熱、可靠性、成本、器件尺寸等問題,是替代傳統封裝技術解決方案之一。本文總結了HRP工藝的封裝特點和優勢,詳細介紹其工藝實現路線,為傳統封裝技術替代提供解決方案。

1 傳統封裝技術及其弊端介紹

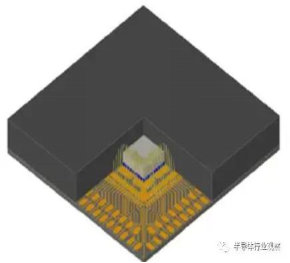

集成電路封裝是半導體器件制作的最后一步。傳統的芯片封裝是指將制作好的晶粒嵌入具有保護作用的塑料、金屬或陶瓷殼體中,并與外界電路及其他元器件連接的過程。此過程需要借助銀漿或其他膠水將晶粒粘接固定在引線框架上,通過引線鍵合實現芯片輸入輸出端口與引線框架引腳實現電氣互聯,再進行模壓塑封、陶瓷燒結或采用金屬殼體將晶粒包覆起來,最后進行切割、測試完成芯片封裝(如圖1)。

圖1 傳統封裝工藝流程

圖1 傳統封裝工藝流程

此傳統封裝技術使得元器件存在以下弊端:

(1)散熱問題。芯片散熱主要途徑有:

a. 芯片內部熱量通過硅襯底、導電銀漿、引線框架、芯片管腳、焊接錫膏、電路基板進行散熱,散熱路徑 長,熱阻高,散熱效果一般。

b.芯片內部產生的熱量通過電氣互聯線導熱至引線 框架上,再通過引線框架引腳及焊接錫膏導熱到電路基板上進行散熱。通常電氣互聯線為銅線,線徑為0.8~1.2mil,線徑小、路徑長,導熱能力有限。散熱效果一般。

c.芯片產生的熱量散發到外殼包封的塑膠、陶瓷或金屬包封殼體散熱。塑膠包封殼體導熱系數低,散熱能力差。而陶瓷或金屬殼體導熱系數較好,但是同時也帶來高昂的成本。

圖2 傳統心態封裝結果

圖2 傳統心態封裝結果

(2)可靠性問題。

圖3 引線鍵合線徑受損

圖3 引線鍵合線徑受損

(如圖2)為傳統芯片封裝結構,每顆芯片由幾根、幾十根甚至上百根鍵合線實現晶粒與引線框架引腳的電氣互聯。引線鍵合工藝因焊線瓷嘴磨損、焊線參數匹配性等因素容易導致鍵合線焊球頸部受損(如圖3所示)。

而塑封材料、晶粒、鍵合線、引線框架由于不同材料熱膨脹系數不一樣,在應用端SMT高溫過爐或產品使用過程中發熱,熱應力導致鍵合線受損部位斷開,導致器件失效。塑封器件因塑封材料容易吸潮,不同封裝材料結合面存在縫隙也容易導致水汽進入,在SMT工藝及產品使用過程中,熱應力和濕應力的雙重作用下將加速器件失效。

(3)成本問題。

芯片封裝經過晶粒固定、引線鍵合、AOI檢查、模壓、電鍍、切割、測試工序,工藝流程長,生產效率慢,需要投入高額的設備成本、人工成本及材料成本,使得產品成本居高不下。

(4)器件尺寸大,阻礙產品微型化問題。芯片封裝需要預留足夠的引線鍵合空間,完成引線鍵合后,還需要進行塑封,使得器件尺寸遠大于晶粒尺寸,對于器件或產品尺寸微型化造成了阻礙。 基于以上傳統封裝存在的弊端,我們進行了深入的技術研究,采用HRP晶圓級先進封裝技術替代傳統封裝技術,有效解決產品散熱、可靠性、成本、產品尺寸微型化等問題。

2 HRP工藝介紹

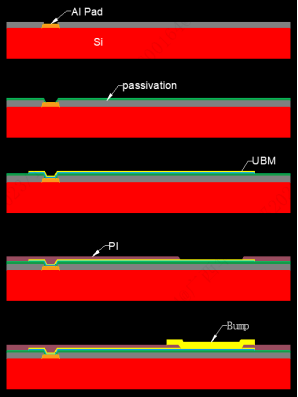

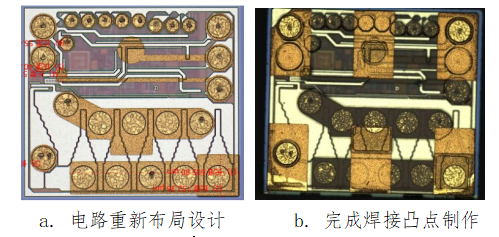

HRP旨在依據芯片電流大小、發熱量、輸入輸出端口電路連接設計等,對芯片做線路層重構設計,并制作焊接凸點。主要設計內容為,依據電流大小、發熱量及散熱要求,設計符合要求的線寬、線距、線厚,確保芯片電學、熱學特性達到設計需求。依據輸入輸出端口電路連接進行重新設計,簡化線路及焊接凸點制作。

圖4 HRP工藝流程圖

圖4 HRP工藝流程圖

2.1 HRP工藝技術路線 HRP的工藝路線為使用物理氣相沉積(PVD)制作UBM層,接著通過光刻、電鍍和蝕刻工藝完重構電路布線。 HRP具體的工藝過程如圖4所示。首先在Wafer上沉積一層金屬薄膜(UBM),沉積方法可用物理氣相沉積(PVD)或者化學氣相沉積(CVD),沉積金屬可選擇Ti、Au、Cu等的一種或兩種。隨后在其上涂敷光刻膠,將設計好的圖案或路線通過光刻技術“刻畫”在光刻膠上,然后通過電鍍或化學鍍的方法把圖案或線路進行金屬化,最后在其上涂敷一層PI絕緣層,作為金屬層間絕緣阻隔,在所需制作焊接凸點區域開窗預留凸點制作位置。完成PI層制作后,接著通過UBM層制作、光刻、電鍍、蝕刻完成焊接凸點制作,也可以通過焊料印刷的方式制作焊接凸點。依據所需要制作的電路層數,不斷重復以上步驟就可以獲得所需的多層HRP。

HRP工藝是在晶圓上進行設計制作,隨著所需的HRP完成,芯片的焊接區域也已按照設計所需生成,將晶圓進行劃片后即可得到一顆顆的芯。以往的傳統封裝工藝技術,在完成晶圓劃片后,還要進行后到器件級封裝,即晶粒固定、引線鍵合、模壓塑封、電鍍、切割、測試等工序,才能貼裝到PCB板上組裝使用。而HRP則無需再進行后道的封裝,而是將芯片以倒裝(Flip Chip)的方式焊接組裝在PCB板上,極大地縮短了互聯長度,減小了RC延遲,有效的提升了器件的電性能。

2.2 HRP工藝特點

基于HRP晶圓級先進封裝技術對芯片進行了電學、熱學的電路設計重構,并直接倒裝焊接在PCB板上,其具有如下特點:

圖5 HRP封裝結構

圖5 HRP封裝結構

(1)散熱能力好。如圖5所示,電路重構設計在芯片表面設計了大面積金屬布局,并在特定位置設計較大尺寸的焊接凸點,最終直接倒裝焊接在PCB上,其散熱路徑為直接通過重構電路、焊接凸點、焊接錫膏即可將熱量傳導到PCB上,且均為大面積的金屬導熱,導熱系數高,散熱路徑短,從而帶來了較好的散熱性能。經測試對比,相同芯片,采用HRP晶圓級封裝技術替代傳統的封裝技術,使用過程中,達到熱穩態后,其溫度比傳統封裝產品低40%以上。

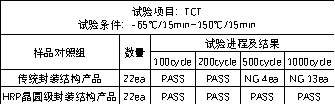

(2)可靠性高。參考圖5所示的電路重構設計及焊接凸點設計,均為大面積金屬致密結合,并通過倒裝的方式焊接在PCB板上,封裝結構簡單,抗機械強度高,沒有傳統封裝的引線鍵合損傷的失效風險,也沒有塑封材料吸潮、熱膨脹系數差異大導致的應力影響,具有優秀的可靠性表現。

如右側表1為相同芯片兩種不同封裝形式的可靠性對比。

(3)成本低。HRP晶圓級封裝技術是在晶圓上進行,單片晶圓顆粒數為幾千甚至幾萬顆,UBM生長、光刻、電鍍、蝕刻均是正片wafer上所有晶粒同時進行,生產效率極高,良率高達99.9%以上,單位生產成本低。同時HRP線路重構可采用鈀、銅等金屬制作,使用的材料較少,材料費用低。晶圓完成劃片后即可貼裝到PCB板上進行組裝使用,不再進行后道器件級封裝,省去全部的后道工藝制作。經測算,采用HRP晶圓級封裝技術綜合成本比傳統封裝技術低30%以上。

(4)產品尺寸微型化。HRP晶圓級封裝技術在晶粒上進行電路重構及焊接凸點制作,相比傳統封裝尺寸因引線鍵合及塑封額外增加了大量的尺寸空間,采用HRP晶圓級封裝技術完成封裝后的芯片,其尺寸與裸晶粒完全相同,不會額外增加尺寸,對于追求產品尺寸微型化的應用是最優的解決方案。

3 HRP工藝進展

華芯邦科技HotChip的研發團隊對HRP晶圓級先進封裝技術做了深入研究及大量的探索驗證,目前HRP工藝技術已成功批量應用與微機電芯片,未來,我們還將繼續拓展應用于電源IC、LDO、存儲器等領域。 目前,大多數芯片采用的封裝方式因散熱能力不足而或多或少的存在一些可靠性方面的問題。在持續的進行高功率輸出時,芯片容易過熱進而觸發保護機制,導致性能中斷,嚴重影響用戶體驗。為了解決這些問題,HotChip HRP封裝技術進行了深入研究,并從底層傳熱學邏輯出發,全面分析了元器件在工作狀態下的界面熱阻。研發團隊運用有限元仿真技術,構建了元器件的傳熱模型,以便改善散熱問題。通過對傳熱模型的研究,HotChip改善了現有的封裝方式,提高了芯片的散熱性能,保證了可靠性,從而有效地提升了用戶的使用體驗。

4 結束語

如今,隨著芯片成本日漸上漲以及封裝難度的增加,HRP工藝路線將會逐漸在先進封裝領域中大放光彩,主要的優勢為:

1)可以直接貼合在柔性線路板上,實現柔性封裝;

2)可以實現超高密度的多層布線;

3)具有更高的良率、更低的成本及更好的可靠性。因此,雖然HRP應用不久,但研發者們在工藝優化、材料選擇、設備改進等方面已經進行了大量的實驗驗證并取得了一系列成果,未來將成為系統級集成的重要解決方案。

5 參考文獻

(1)一文講透QFN封裝- 半導體行業觀察

(2)晶圓級封裝技術的發展-戴錦文

(3)扇出型晶圓級封裝可靠性問題與思考-范懿鋒1董禮2張延偉1王智彬1孟猛1

(4)先進的扇出晶圓級封裝進展-Yonggang JinJerome TeysseyreAnandan RamasamyYun LiuBing Hong Huang

(5)電子元器件封裝技術發展趨勢-黃慶紅

審核編輯 黃宇

-

芯片

+關注

關注

460文章

52616瀏覽量

442585 -

封裝

+關注

關注

128文章

8741瀏覽量

145730 -

晶圓級

+關注

關注

0文章

37瀏覽量

10068 -

先進封裝

+關注

關注

2文章

479瀏覽量

663

發布評論請先 登錄

HRP晶圓級先進封裝替代傳統封裝技術研究(HRP晶圓級先進封裝芯片)

HRP晶圓級先進封裝替代傳統封裝技術研究(HRP晶圓級先進封裝芯片)

評論