文章來(lái)源:學(xué)習(xí)那些事

原文作者:前路漫漫

本文介紹了晶圓級(jí)封裝技術(shù)的概念、優(yōu)劣勢(shì)和發(fā)展現(xiàn)狀及趨勢(shì)。

WLP技術(shù)概述與發(fā)展

圓片級(jí)封裝(WLP),也稱為晶圓級(jí)封裝,是一種直接在晶圓上完成大部分或全部封裝測(cè)試程序,再進(jìn)行切割制成單顆組件的先進(jìn)封裝技術(shù) 。WLP自2000年左右問(wèn)世以來(lái),已逐漸成為半導(dǎo)體封裝領(lǐng)域的主流技術(shù),深刻改變了傳統(tǒng)封裝的流程與模式。

在傳統(tǒng)封裝工藝中,通常先將晶圓分割成單個(gè)裸片,再對(duì)裸片進(jìn)行QFP、BGA、CSP等形式的封裝;而WLP實(shí)現(xiàn)了前道IC加工與后道IC組裝在晶圓層面的整合。其基本工藝是在晶圓完成IC加工后,通過(guò)特定工藝直接在晶圓上構(gòu)建IC互連接口,完成測(cè)試、老化等流程后再進(jìn)行分割,直接產(chǎn)出IC成品。WLP的技術(shù)發(fā)展與晶圓級(jí)凸點(diǎn)技術(shù)緊密相關(guān)。自20世紀(jì)60年代起,IBM公司便在倒裝芯片工藝中應(yīng)用晶圓級(jí)凸點(diǎn)技術(shù),WLP正是這一技術(shù)自然演進(jìn)的成果。標(biāo)準(zhǔn)意義上的WLP封裝尺寸與芯片一致,也被稱為晶圓級(jí)芯片尺寸封裝(WLCSP),屬于真正意義上的芯片尺寸封裝。隨著技術(shù)需求的提升,為突破WLCSP在I/O數(shù)量上的限制,扇出型晶圓級(jí)封裝(FOWLP)應(yīng)運(yùn)而生。FOWLP通過(guò)在芯片切割后重新排布、模壓重組晶圓,實(shí)現(xiàn)了面積擴(kuò)展與復(fù)雜的異構(gòu)集成,提升了封裝的集成度,降低了成本,增強(qiáng)了性能。與之對(duì)應(yīng),WLCSP也被稱為扇入型(Fan - in)晶圓級(jí)封裝(FIWLP)。

根據(jù)電極轉(zhuǎn)移相關(guān)的方式,圓片級(jí)封裝可粗略分為焊區(qū)上凸點(diǎn)(BOP)WLP、電極再分布WLP、包封式WLP和柔性載帶WLP四種,其中電極再分布WLP是目前晶圓級(jí)封裝技術(shù)的最主要形式。隨著芯片復(fù)雜性的增加,添加金屬重布線層,或稱為電極再分布層(RDL)變得十分必要,它能夠?qū)⒑盖驈男酒竞副P上轉(zhuǎn)移到合適的凸點(diǎn)位置,以滿足不斷提高的性能需求。

WLP的優(yōu)勢(shì)與局限

一、優(yōu)勢(shì)

WLP的優(yōu)勢(shì)顯著。從尺寸上看,它實(shí)現(xiàn)了封裝面積與芯片面積近乎1:1,相比四邊引腳扁平封裝、板上芯片(COB)封裝等,大幅縮小了在系統(tǒng)電路板上的占用空間,滿足了現(xiàn)代電子產(chǎn)品尤其是便攜式設(shè)備對(duì)小型化的極致追求。以一個(gè)10mm尺寸的芯片為例,四邊引腳扁平封裝的面積是900mm2,芯片與PWB直接引線鍵合的板上芯片(COB)封裝的面積是225mm2,而WLP的封裝面積和芯片面積相同,僅為100mm2,對(duì)于需要減小尺寸或重量的產(chǎn)品而言,采用WLP已經(jīng)將尺寸或重量降到了最小。

在成本方面,WLP與IC加工類似,隨著晶圓尺寸增大和IC尺寸減小,封裝成本降低。它在晶圓劃片前完成封裝和測(cè)試,減少了傳統(tǒng)封裝中因晶圓增大需線性增加封裝設(shè)備(如引線鍵合機(jī)、模塑機(jī)、測(cè)試儀和取放裝置等)的成本投入;同時(shí),采用標(biāo)準(zhǔn)卷帶式傳送設(shè)備和標(biāo)準(zhǔn)SMT技術(shù)進(jìn)行組裝裝配,進(jìn)一步優(yōu)化了成本結(jié)構(gòu)。并且,在圓片級(jí)一次性實(shí)現(xiàn)所有IC的測(cè)試和老化,也大大降低了測(cè)試和老化成本,這對(duì)于大規(guī)模生產(chǎn)來(lái)說(shuō),成本優(yōu)勢(shì)尤為明顯。

在性能上,WLP采用薄膜工藝實(shí)現(xiàn)互連,縮短了引線長(zhǎng)度,降低了寄生電阻、電容、電感,顯著提升了電性能。WLP中的芯片尺寸通常較小,約10mm左右,I/O數(shù)從少到中等,一般約100左右,大部分WLP采用面陣列互連,這種互連方式具有諸多優(yōu)點(diǎn):一方面,焊料凸點(diǎn)比引線鍵合的引線尺寸小得多,電感和電阻都很小,從而擁有很好的電性能;另一方面,所有I/O焊盤都在芯片的有源面上方,互連區(qū)不超過(guò)芯片面積范圍,且面陣列互連的I/O節(jié)距可以達(dá)到最大,可以直接與成本最低的PWB進(jìn)行互連,大大提高了封裝的實(shí)用性和經(jīng)濟(jì)性。

二、局限

不過(guò),WLP也存在一定局限性。當(dāng)IC的I/O數(shù)量較多時(shí),為保證互連,焊球尺寸和節(jié)距需相應(yīng)減小,這對(duì)PWB的制造工藝提出了極高要求,適配的高密度PWB成本昂貴,限制了其在高I/O芯片中的應(yīng)用。例如,目前實(shí)際應(yīng)用中的最小 PWB 節(jié)距已突破 0.5mm,達(dá)到 110μm 級(jí)別,若要降低到100μm,就需要在一塊很大的電路板上采用12μm的光刻技術(shù)進(jìn)行加工,這無(wú)疑是十分困難且成本高昂的。

此外,WLP需對(duì)晶圓上所有IC進(jìn)行封裝,在早期晶圓加工成品率較低時(shí),會(huì)顯著增加成本;盡管隨著工藝成熟及 AI 檢測(cè)技術(shù)(如 X 射線預(yù)篩選、缺陷自動(dòng)識(shí)別)的普及,失效 IC 在封裝前即可被高效剔除,資源浪費(fèi)問(wèn)題已大幅緩解,但仍是需要持續(xù)優(yōu)化的環(huán)節(jié)。因?yàn)榧词宫F(xiàn)在晶圓加工技術(shù)已經(jīng)有了很大進(jìn)步,仍難以保證晶圓上所有IC都是完好的,對(duì)失效IC進(jìn)行封裝會(huì)造成一定的資源浪費(fèi)。

WLP的應(yīng)用現(xiàn)狀與未來(lái)趨勢(shì)

目前,WLP已廣泛應(yīng)用于可擦除可編程只讀存儲(chǔ)器(EPROM)、模擬芯片、射頻(RF)、集成無(wú)源器件(IPD)以及微機(jī)電系統(tǒng)(MEMS)等領(lǐng)域。國(guó)際半導(dǎo)體技術(shù)路線圖(ITRS)將其定義為基于晶圓(或晶圓形式)實(shí)現(xiàn)封裝和測(cè)試,且封裝后的單個(gè)封裝體可直接用于電路組裝工藝的技術(shù)。其主要封裝形式包括I/O端扇入型、I/O端扇出型、集成無(wú)源器件圓片級(jí)封裝及各類傳感器的圓片級(jí)封裝等。以扇出型圓片級(jí)封裝——嵌入式圓片級(jí)球柵陣列封裝(embedded Wafer Level Ball Grid Array,eWLB)為例,其典型的封裝結(jié)構(gòu)所涉及的主要封裝材料包括制造再布線層(Redistribution Layer,RDL)中介質(zhì)層的光敏材料、布線金屬層材料和實(shí)現(xiàn)微互連的微細(xì)連接材料及包封保護(hù)材料等。

隨著半導(dǎo)體產(chǎn)業(yè)向更高集成度、更小尺寸、更低功耗方向發(fā)展,WLP 與 2.5D/3D 封裝、Chiplet 技術(shù)深度融合,憑借其在異構(gòu)集成方面的潛力,將成為未來(lái)先進(jìn)封裝的重要發(fā)展方向。

同時(shí),隨著技術(shù)的不斷進(jìn)步,WLP在解決現(xiàn)有局限性方面也有望取得突破,從而拓展其在更多領(lǐng)域的應(yīng)用。

-

封裝

+關(guān)注

關(guān)注

128文章

8685瀏覽量

145521 -

晶圓級(jí)封裝

+關(guān)注

關(guān)注

5文章

41瀏覽量

11671 -

先進(jìn)封裝

+關(guān)注

關(guān)注

2文章

476瀏覽量

629

原文標(biāo)題:晶圓級(jí)封裝簡(jiǎn)介

文章出處:【微信號(hào):bdtdsj,微信公眾號(hào):中科院半導(dǎo)體所】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

STM32WB和STM32L4/L4+的區(qū)別和優(yōu)劣勢(shì)是什么?

電流檢測(cè)采用高端檢測(cè)和低端檢測(cè)有什么區(qū)別?有什么優(yōu)劣勢(shì)?

Prolith和HyperLith的優(yōu)劣勢(shì)

你如何看待LoRa技術(shù)的優(yōu)劣勢(shì)?

請(qǐng)問(wèn)工業(yè)機(jī)器人有什么優(yōu)劣勢(shì)?

異步電路原理是什么?有哪些優(yōu)劣勢(shì)?

SPI協(xié)議的特性是什么?具有哪些優(yōu)劣勢(shì)?

六種室內(nèi)定位技術(shù)的優(yōu)劣勢(shì)分析

uwb定位技術(shù)優(yōu)劣勢(shì)有哪些_uwb定位技術(shù)的應(yīng)用

cob封裝的優(yōu)劣勢(shì)

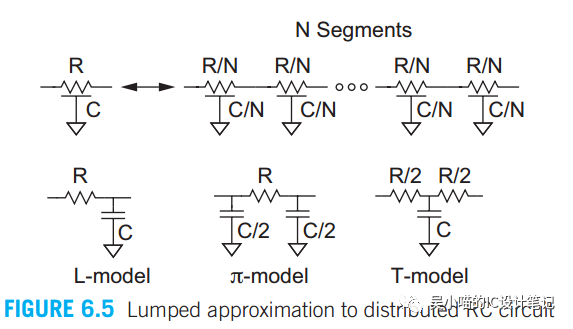

RC modeling的優(yōu)劣勢(shì)

晶圓級(jí)封裝技術(shù)的概念和優(yōu)劣勢(shì)

晶圓級(jí)封裝技術(shù)的概念和優(yōu)劣勢(shì)

評(píng)論