文章來源:鮮棗課堂

原文作者:小棗君

本文介紹了先進封裝技術中的晶圓級封裝技術。

晶圓級封裝

我們看下一個先進封裝的關鍵概念——晶圓級封裝(Wafer Level Package,WLP)。

傳統封裝,是先切割晶圓,再封裝。

而晶圓級封裝的核心邏輯,是在晶圓上直接進行封裝,然后再切割,變成芯片。

舉個例子:傳統封裝,是先把大面團切成一塊塊,然后分別烘烤成蛋糕,分給大家吃。而晶圓級封裝,是先烤一個大蛋糕,然后切成一塊塊,分給大家吃。

從更廣泛的意義上講,任何在晶圓這一層級進行全部或部分加工的封裝,都可以被認為是晶圓級封裝。

晶圓級封裝出現于2000年左右,是半導體產業追求更高效率、更低成本的產物。

在晶圓上進行封裝過程,能夠帶來以下好處:

1、由于側面未涂覆封裝材料,因此封裝后的芯片尺寸較小。晶圓上,晶粒的密度更高,平均成本更低。

2、方便批量生產制造芯片,縮短工期,總體成本也比較低。

3、芯片設計和封裝設計可以統一考慮,提升設計效率,降低設計成本。

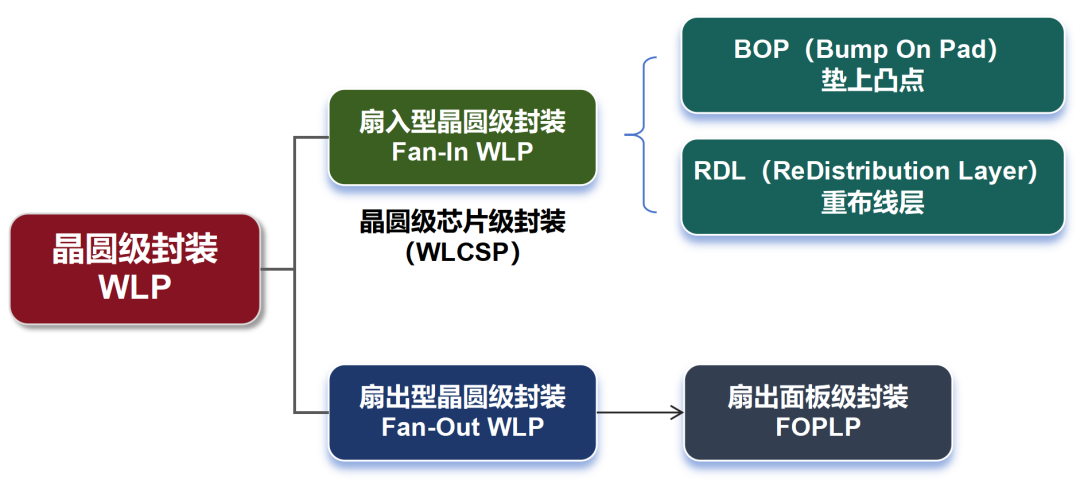

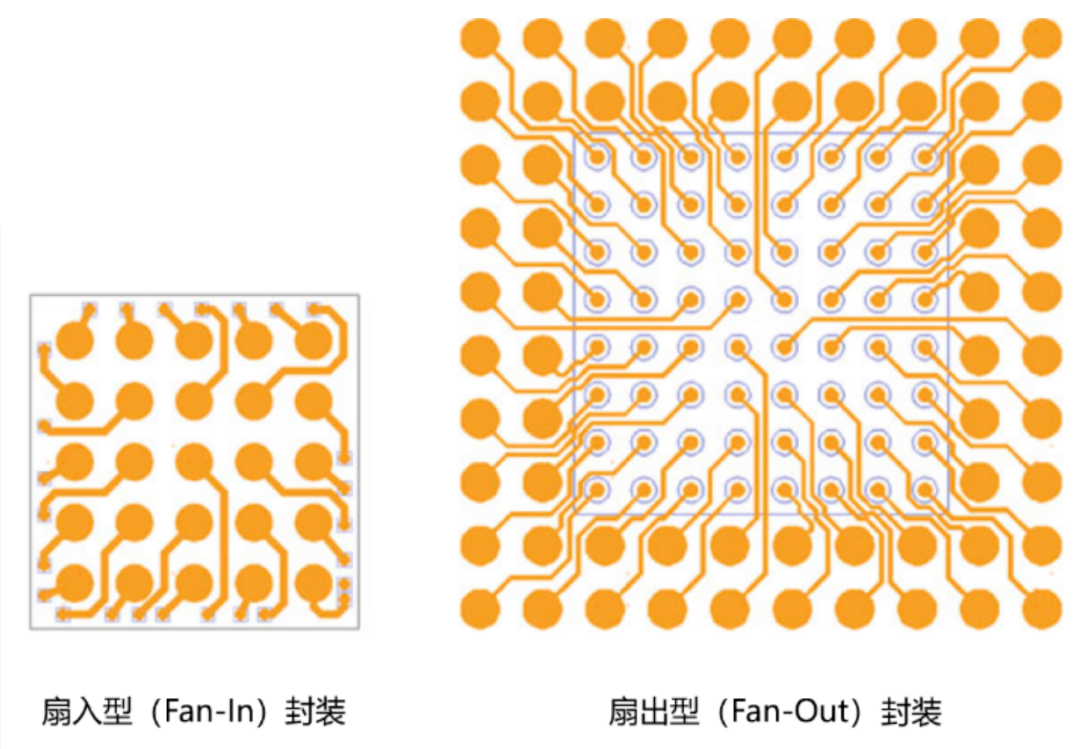

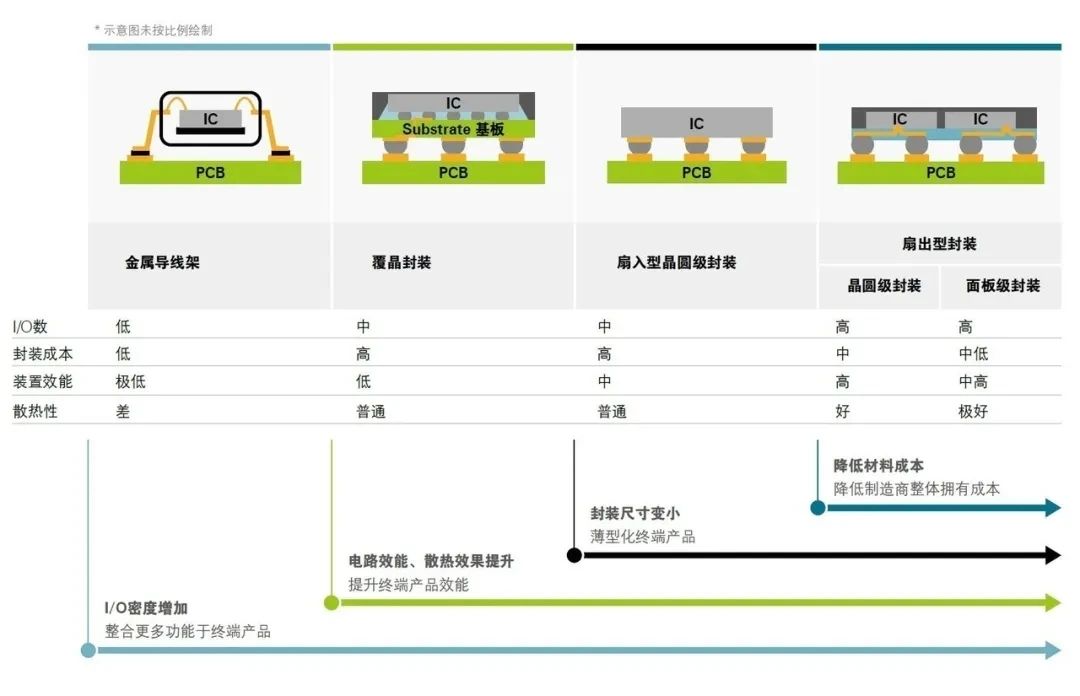

晶圓級封裝,可以分為:扇入型晶圓級封裝(Fan-In WLP)和扇出型晶圓級封裝(Fan-Out WLP)。

這里的“扇(Fan)”,指的是芯片的尺寸。

我們分別來介紹。

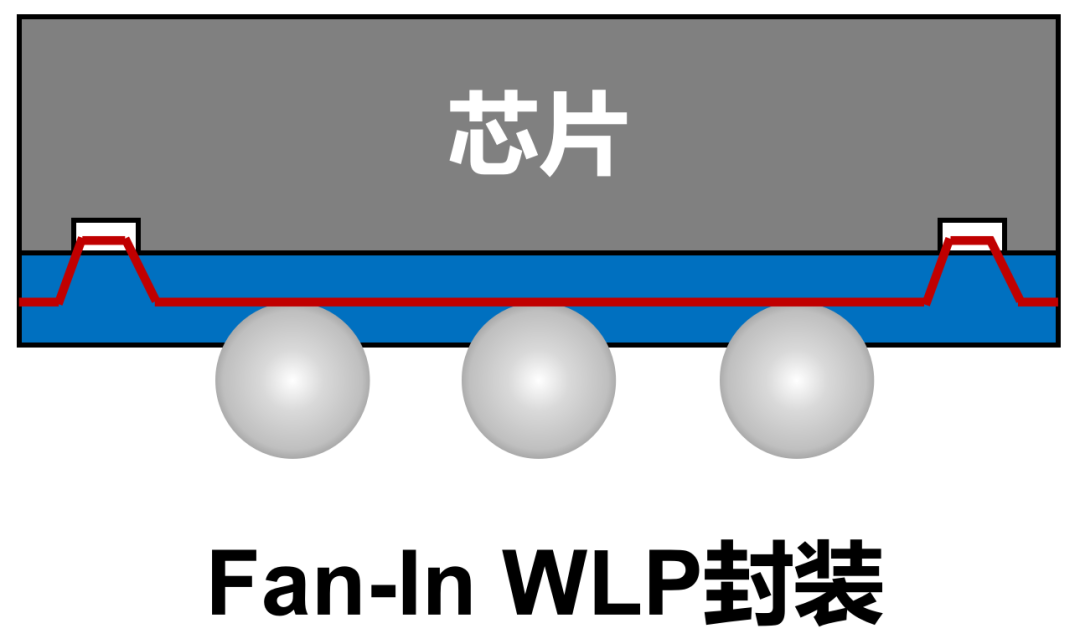

· 扇入型WLP(FIWLP)

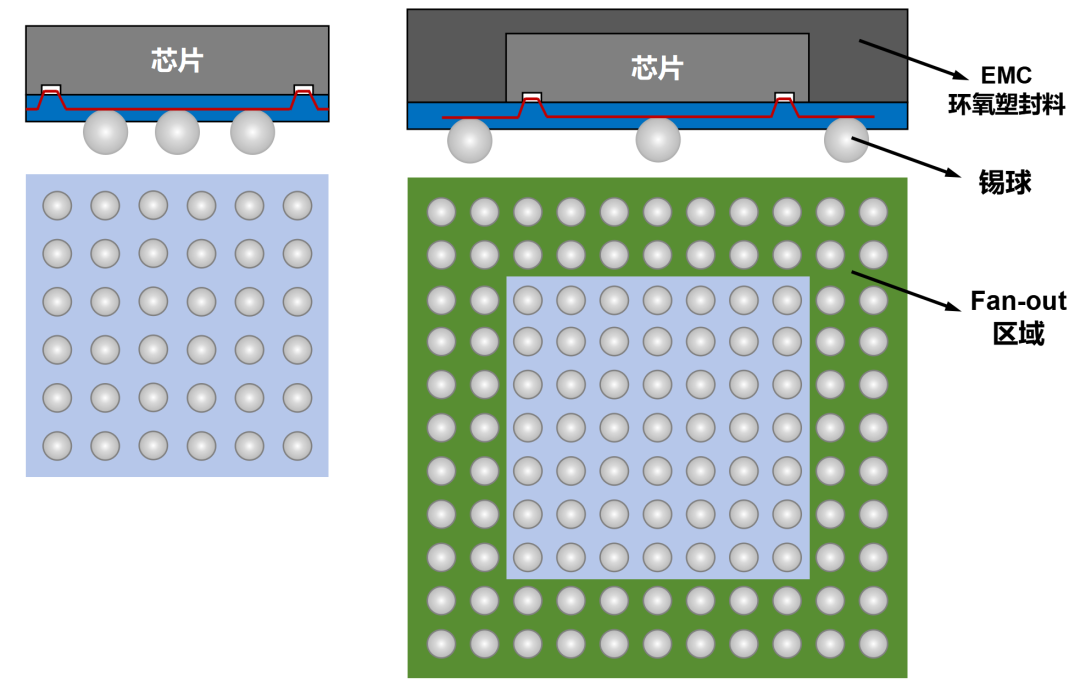

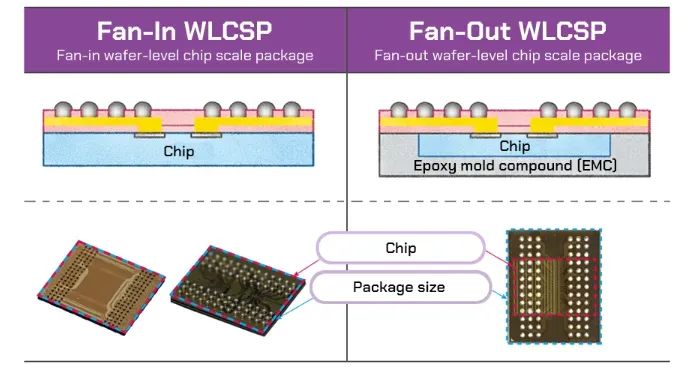

早期的WLP,多采用扇入型。扇入型的封裝布線、絕緣層以及錫球,都位于晶圓的頂部。封裝后的尺寸,和芯片尺寸是相同的。

芯片面積與封裝面積之比超過1:1.14的封裝,是CSP(芯片級封裝)。扇入型WLP都1:1了,顯然也屬于CSP。所以,由扇入型晶圓級封裝技術制成的封裝,也稱為晶圓級芯片級封裝(WLCSP)。

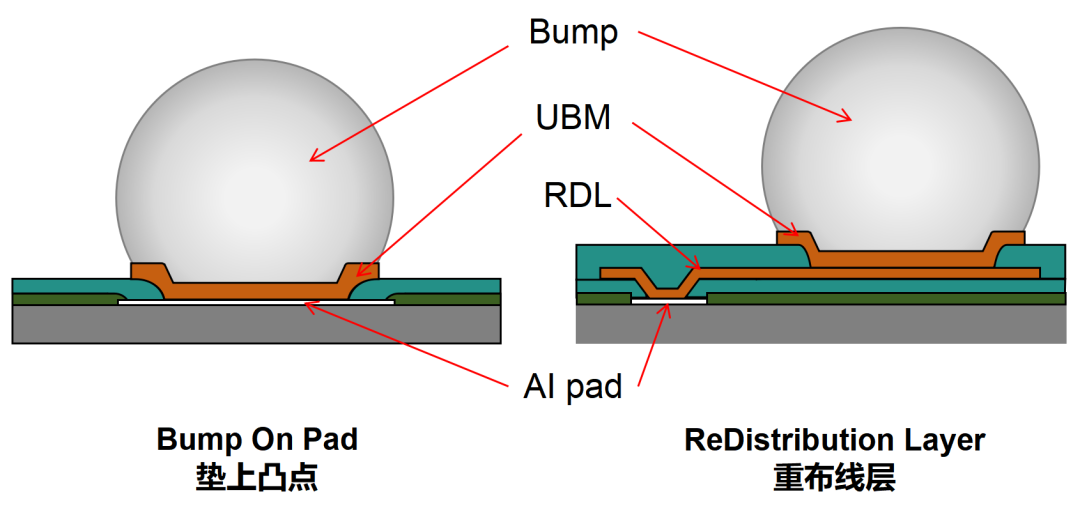

扇入型WLP,通常可以分為BOP(Bump On Pad,墊上凸點)和RDL(ReDistribution Layer,重布線層)兩種方式。

BOP封裝的結構非常簡單,Bump(凸點)直接構建在Al pad(鋁襯板)的上面。如果Bump的位置遠離Al pad,那么,就需要通過借助RDL技術,將Bump與Al pad進行連接。

大名鼎鼎的RDL,終于出現了。

我們需要單開一節,專門介紹一下它。

· RDL

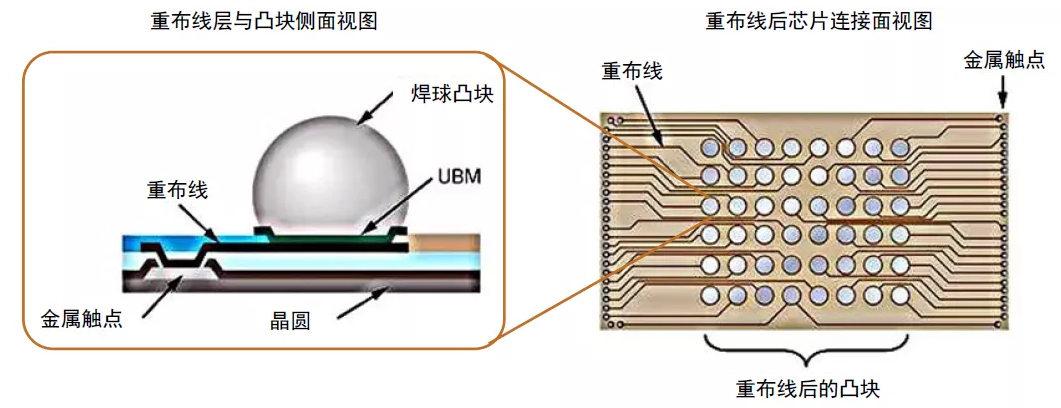

RDL的全稱,是ReDistribution Layer(重布線層)。

RDL是晶圓級封裝(WLP)的核心技術,也是后面2.5D/3D立體封裝的核心技術。在先進封裝里,它占有重要地位。

它是在晶粒下面的中介層上進行重新布線,實現I/O端口的重新布局。

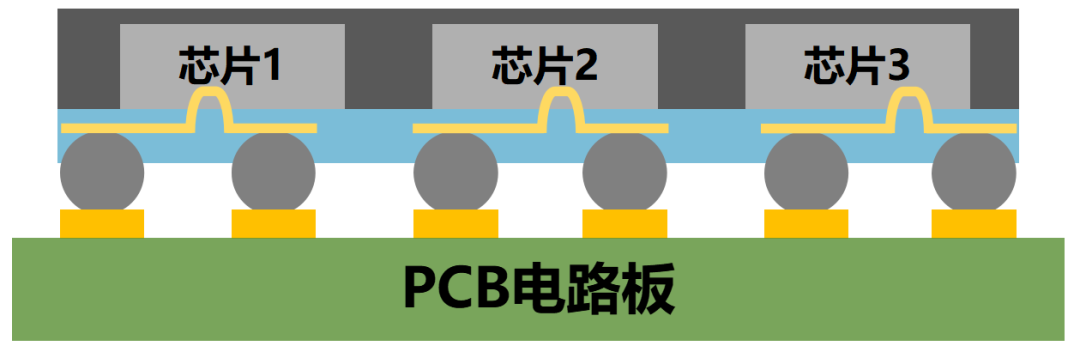

簡單來說,它就像我們平時看到的PCB電路板。只不過,真正的PCB板是在芯片的外面,把各個成品芯片和元器件連起來。

而RDL,是封裝內部的“PCB板”,方便了XY平面(橫向平面)的電氣延伸和互聯。它提升了封裝內部電氣連接的靈活性,能夠讓芯片內部布局更合理、更緊湊。

基于RDL,晶圓芯片上的“細間距”外圍陣列,可以變成“更大間距”陣列。

基于之前晶圓制造的文章,大家會發現,RDL很像晶粒內部的金屬連線(立交橋)。

晶粒內的金屬沉積

是的,RDL的工藝,和晶圓制作流程中的“蓋樓”流程差不多(可以參考晶圓制作的那期),主要就是光刻、涂膠顯影、刻蝕、濺射沉積、電鍍銅等工藝。

RDL也屬于將晶圓制造(前道)工藝降維到封裝(后道)中使用。和凸點一樣,也是中道工序。

目前,主流的RDL工藝有兩種:

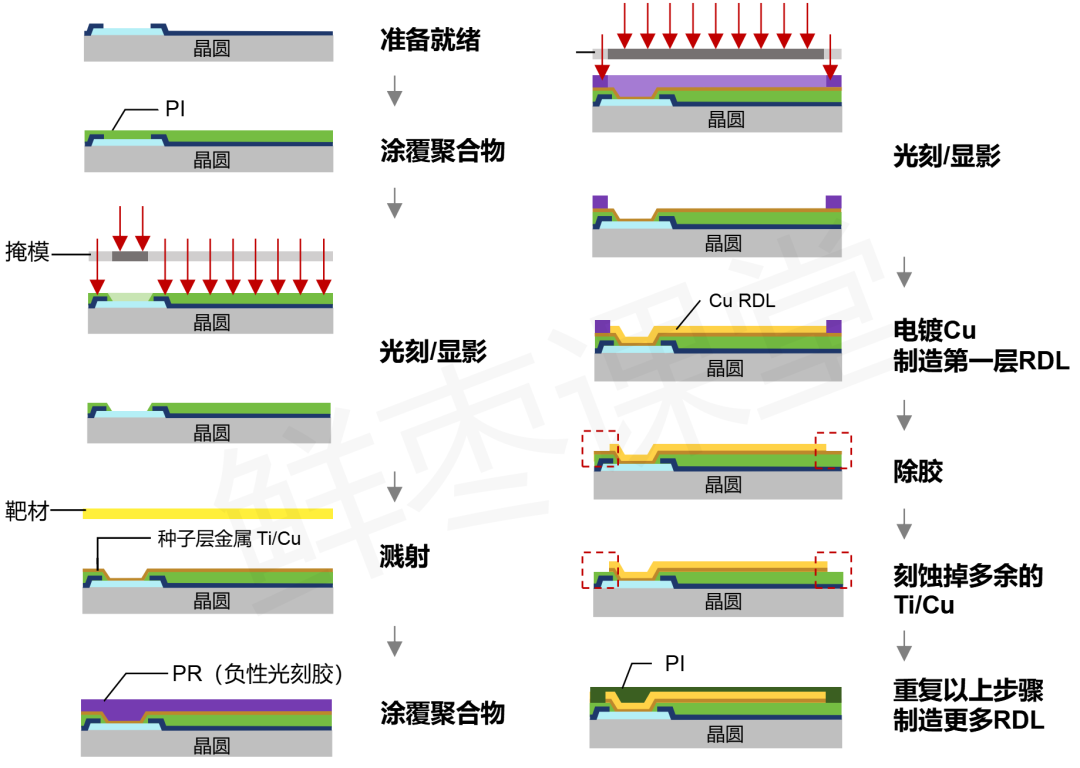

第一種,是基于感光高分子聚合物,并結合電鍍銅與刻蝕工藝實現。

1、在晶圓表面涂覆一層聚合物薄膜,可選的聚合物材料包括光敏聚酰亞胺(PI)、苯并環丁烯(BCB)以及聚苯并惡唑(PBO)。這是為了增強芯片的鈍化層并起到應力緩沖的作用。

2、加熱固化后,使用光刻工藝在所需位置進行開孔,之后進行刻蝕。

3、通過物理氣相沉積工藝(PVD),濺射Ti(鈦)與Cu(銅),分別作為阻擋層與種子層。

4、再來一波光刻、刻蝕工藝,把RDL層的空間給挖出來。

5、通過電鍍Cu工藝,在暴露出的Ti/Cu層上制造第一層RDL。(注意,電鍍是將電解質溶液中的金屬離子還原為金屬并沉積在晶圓表面。)

6、去除掉光刻膠,并刻蝕掉多余的Ti/Cu。

7、涂覆第二層聚合物薄膜,使圓片表面平坦化并保護RDL層。

8、重復上述步驟,制作多層RDL結構。

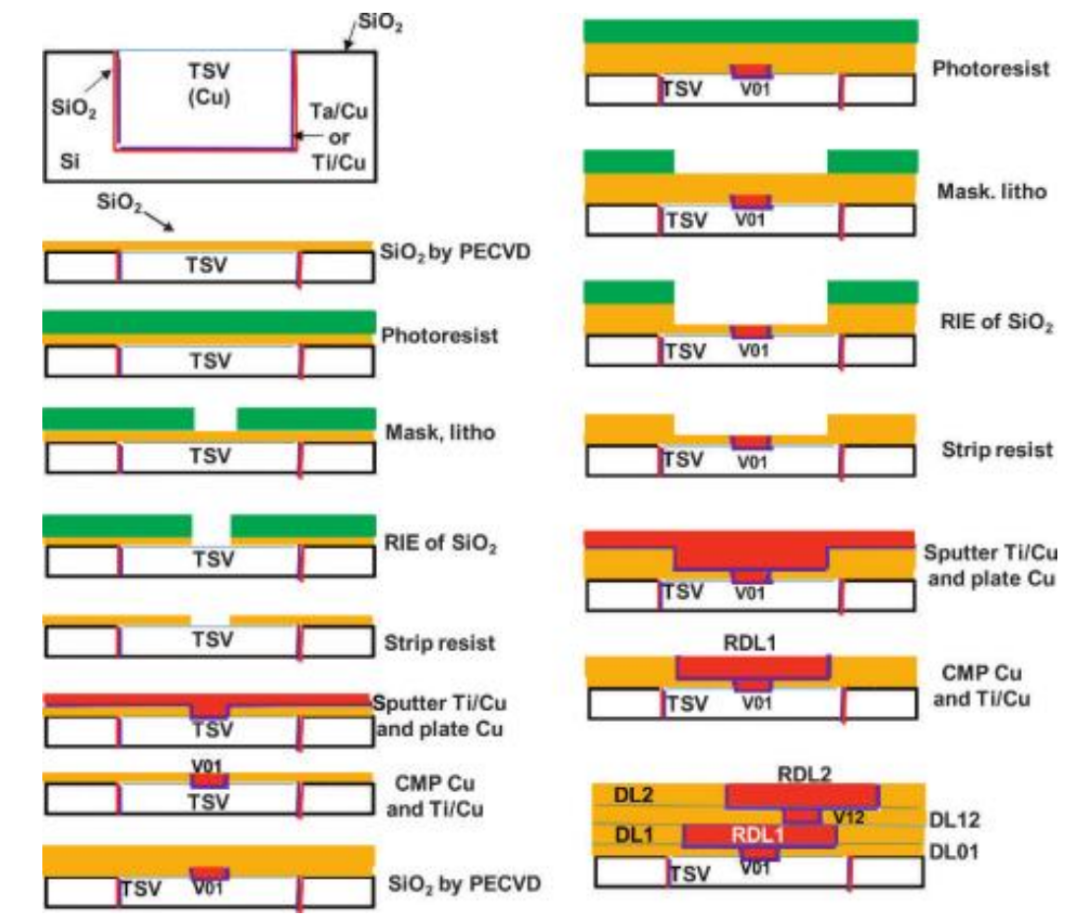

另一種工藝,是采用Cu大馬士革工藝結合PECVD與CMP工藝實現。

大致流程:

1、先采用PECVD工藝,沉積SiO2或Si3N4,作為絕緣層。

2、利用光刻與反應離子刻蝕,在絕緣層上形成窗口。

3、分別濺射Ti/Cu的阻擋/種子層以及導體銅,和剛才工藝一樣。

4、采用CMP(化學機械研磨,之前介紹過的)工藝,將導體層減薄至所需厚度,形成了一層RDL或通孔層。

5、重復上述步驟,制作多層RDL結構。

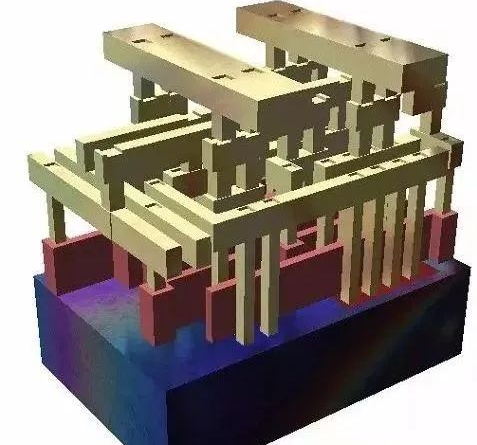

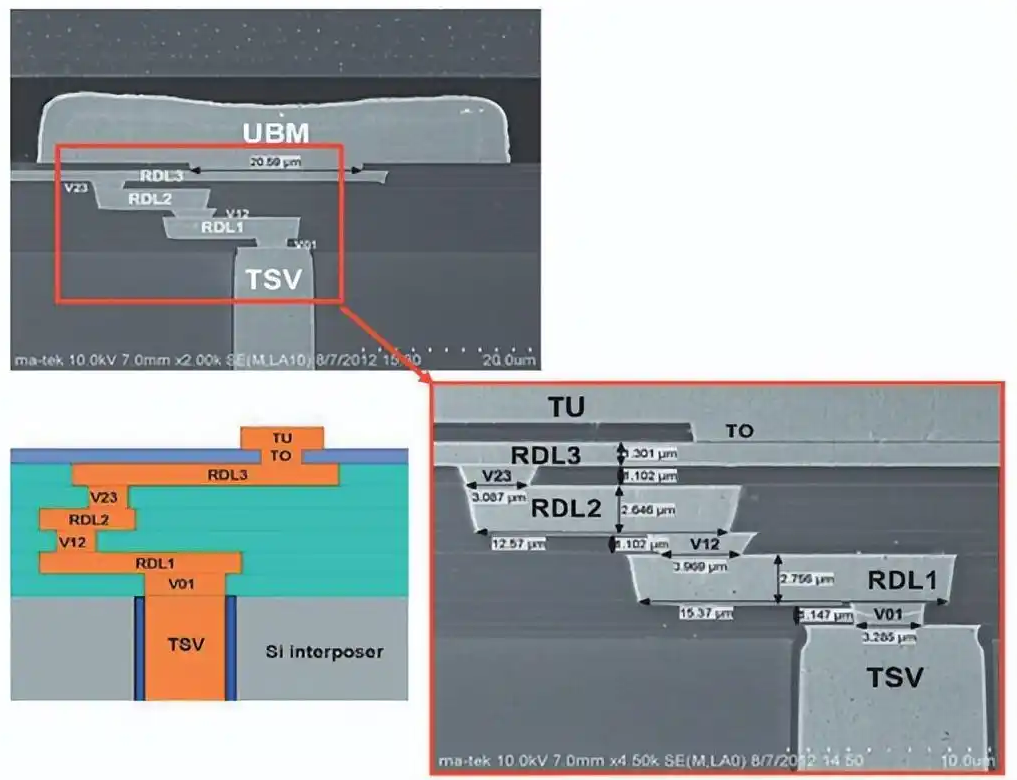

基于大馬士革工藝制作的多層RDL內部構架

第二種工藝需要采用CMP,制造成本比第一種高。在行業里,第一種用得比較多。

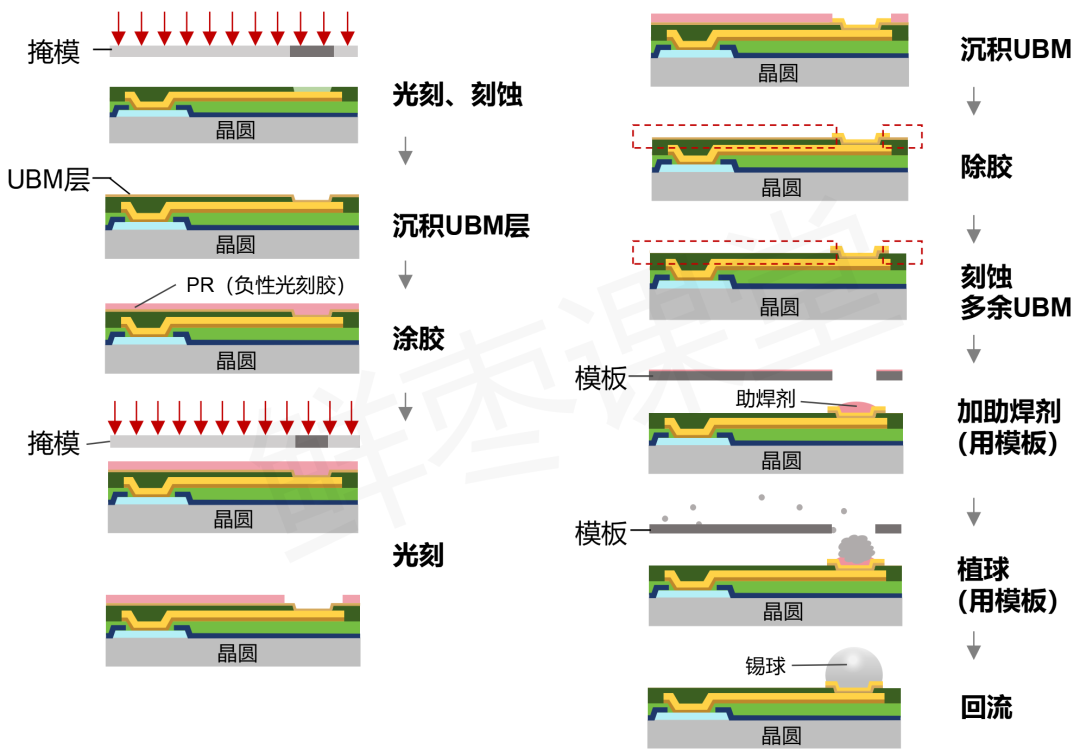

制作完RDL之后,是制作UBM(凸點下金屬層),工藝和RDL相似。

制作完UBM之后,通過掩膜板準確定位焊膏和焊料球,并將其放置于UBM上。

隨后,進行回流,使焊料與UBM形成良好的浸潤結合,從而確保達到理想的焊接效果。

綜合以上步驟,扇入型WLP的大致工藝流程如下:

1、完成RDL布線,方便將I/O引出至方便焊接的位置。

2、對晶圓進行減薄加工。

3、在RDL層所連接的金屬焊盤上,進行植球。

4、對晶圓進行切割,得到獨立的芯片。

5、完成FT測試,出廠。

過去的20多年,扇入型WLP廣泛應用于移動、便攜式和消費類產品。特別是低I/O引腳數(≤200)、小芯片尺寸(≤ 6mm x 6 mm)、低成本、低端、薄型和大容量應用的半導體器件,使用這種封裝比較多。

· 扇出型WLP(FOWLP)

扇入型WLP雖然面積小,但是支持的I/O引腳數也少。隨著時間的推移,芯片的I/O引腳數逐漸增加,扇入型WLP無法滿足要求。于是,就有了扇出型WLP(FOWLP)。

Fan-In WLP與Fan-Out WLP

扇出型WLP中,RDL可以向外延伸布線。這樣一來,封裝的面積大于晶粒的面積,I/O引腳數可以更多,引腳間距也寬松。

扇出型WLP如果符合CSP的尺寸比例要求,就是扇出型WLCSP。

扇出型WLP最早于2006年由英飛凌最先提出。他們在手機基帶芯片封裝中實現了量產,并將其命名為嵌入式晶圓級球柵陣列(eWLB)。

后來,扇出型WLP并沒有獲得什么關注。

直到2016年,臺積電基于FOWLP,推出了集成扇出型(InFO)封裝,并成功應用于蘋果公司iPhone 7系列手機的A10處理器(AP)中,才讓扇出型WLP獲得了整個行業的高度關注。

憑借該項技術,臺積電成功包攬了蘋果公司之后每一代手機的AP芯片制造和封裝訂單。

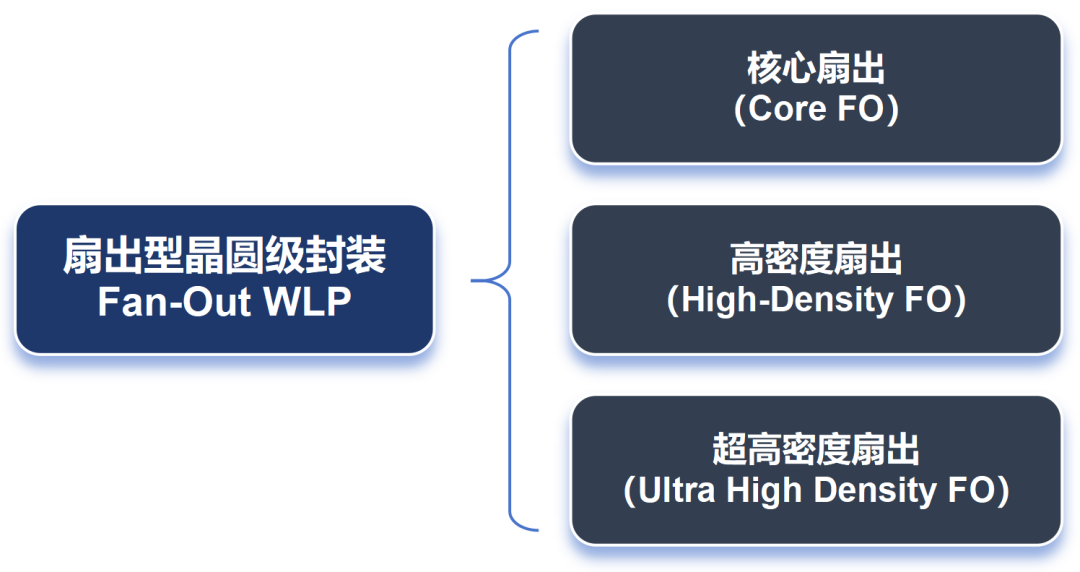

后來,FOWLP高速發展,衍生出多種變體,包括核心扇出(Core FO)、高密度扇出(High-Density FO)和超高密度扇出(Ultra High Density FO)等,可以應用于不同的需求場景。

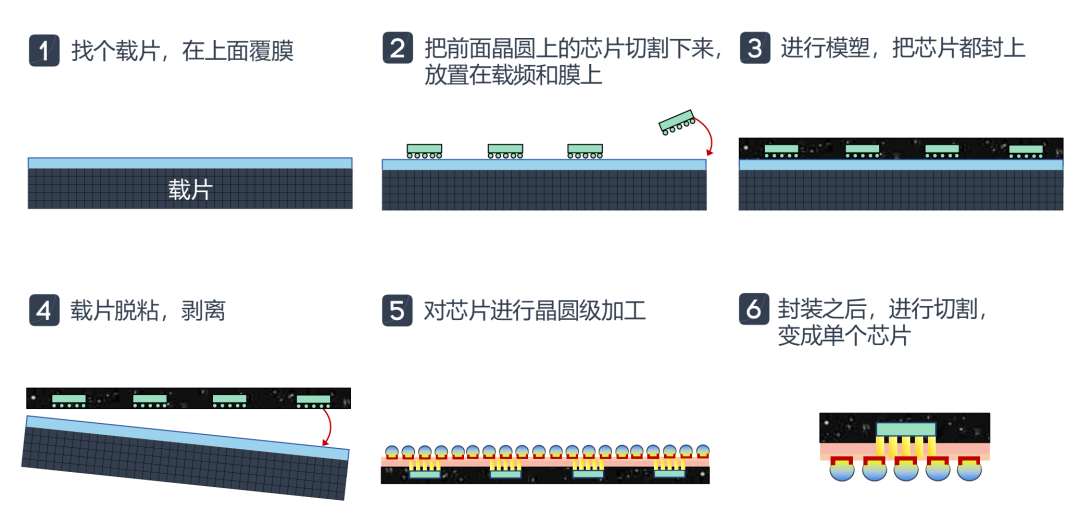

我們來看看FOWLP的工藝過程。

前面說WLP是先封裝,再切割。這句話其實不太適用于FOWLP。

FOWLP,是先切割,然后把芯片重新放置在人工載板上。接下來,再進行晶圓級封裝。封裝完,再次切割,變成最終的芯片。

Fan-Out WLCSP工藝流程

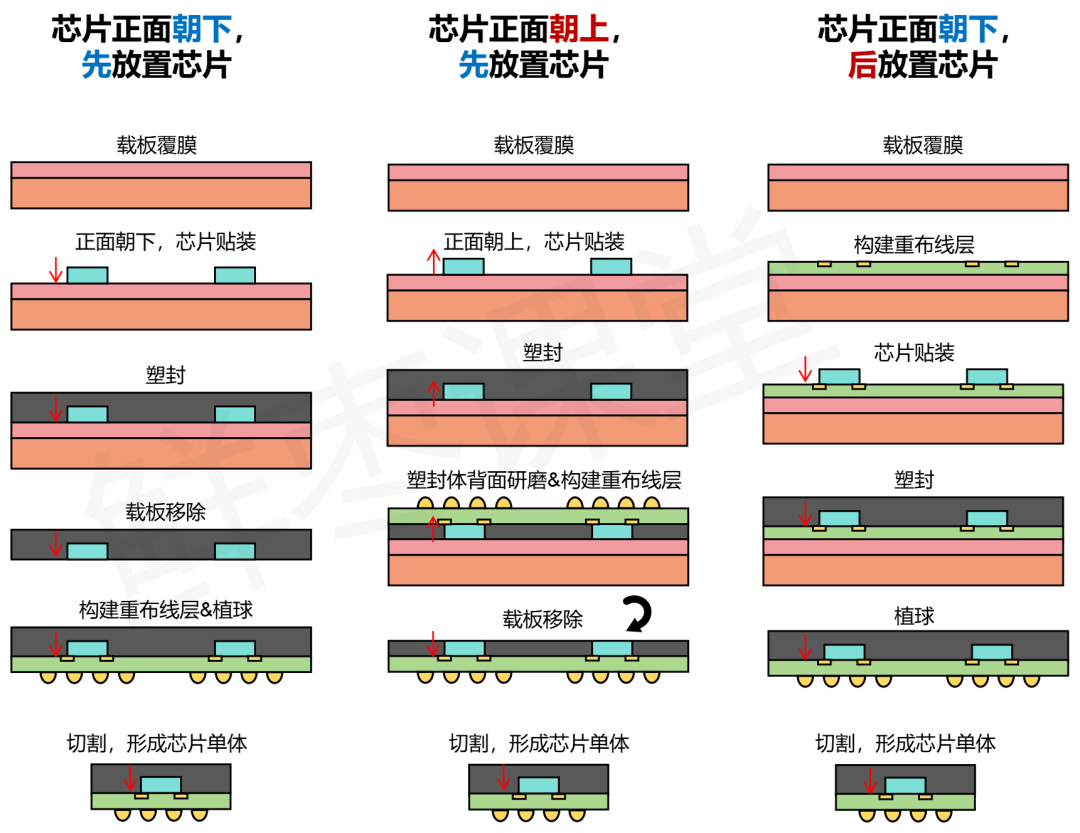

根據工藝過程,扇出式WLP可以分為芯片先裝(Die First)和芯片后裝(Die Last)。芯片先裝又分為面朝下(Face Down)、面朝上(Face Up)。

芯片先裝,簡單地說,就是先把芯片放上, 再做布線(RDL)。

芯片后裝,就是先做布線(RDL)。測試合格的單元,再把芯片放上去。

芯片后裝的優點,是可以提高合格芯片的利用率,以此提高成品率,降低成本。也有缺點,就是工藝相對復雜。

總結一下FOWLP的優點:

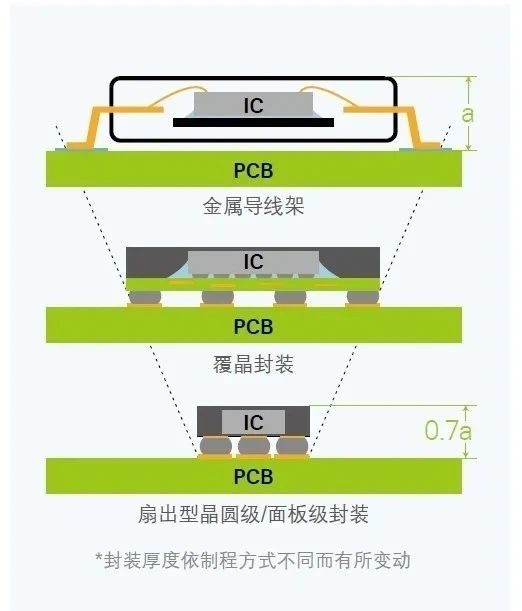

1、FOWLP是一種無載板(Substrate-less)的封裝方式,不需要封裝載板,更不用引線,可以大幅降低成本。

2、FOWLP沒有封裝載板,所以垂直高度更低,能夠提供額外的垂直空間,向上堆疊更多的元件。

3、FOWLP厚度較薄,縮短芯片與散熱片之間的距離,有利于散熱。

4、FOWLP可以將不同功能的芯片進行靈活集成,進而完成系統級封裝(SiP)。這是后摩爾時代非常重要的技術手段之一。

· 扇出面板級封裝(FOPLP)

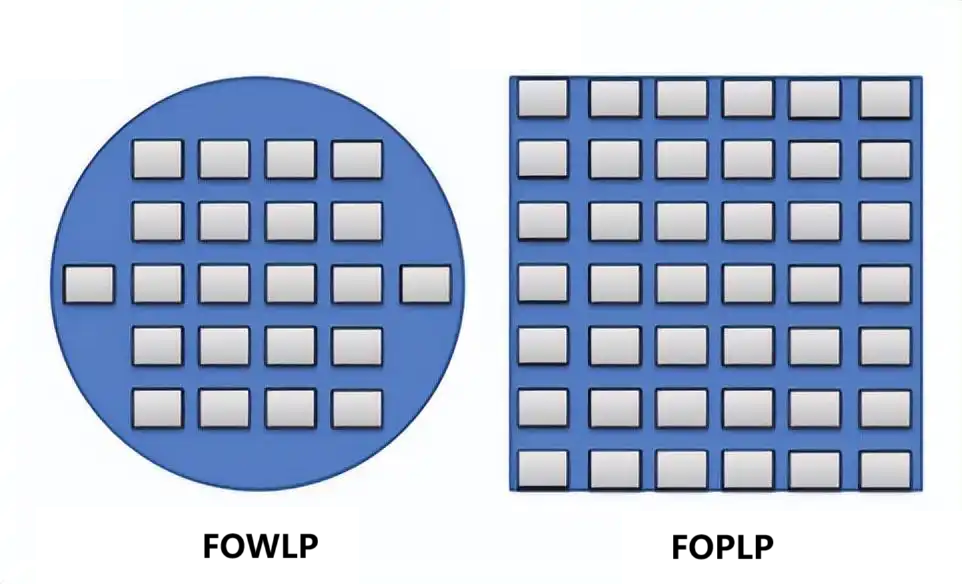

提到FOWLP,就肯定要提一下最近幾年特別火的FOPLP。

FOPLP(扇出面板級封裝),是扇出型封裝的一種,也基于重新布線層(RDL)工藝。

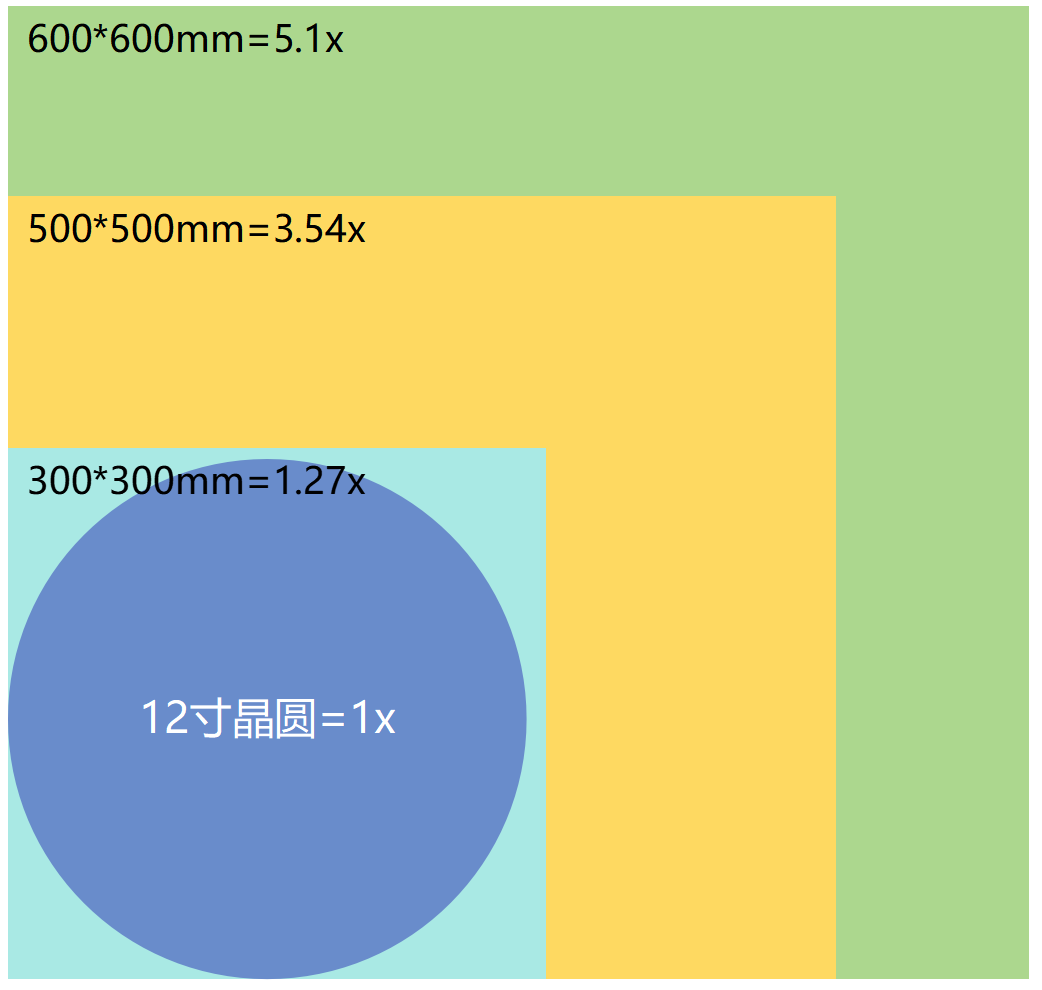

它和FOWLP非常類似,最大的區別在于:FOPLP使用的載板,不是8寸/12寸的晶圓,而是方形的大尺寸面板。

FOPLP具有以下優勢:

1、低成本。

FOPLP采用方形的大尺寸面板,不僅單片產出的芯片數量更多,而且面積利用率更高。根據國際權威研究機構Yole的數據,FOWLP技術面積使用率<85%,而FOPLP技術面積使用率>95%。

以600mmX600mm尺寸的面板為例,面積為12寸wafer carrier的5.1倍,單片產出數量大幅提升。

FOPLP可以大幅提高材料利用率和生產效率,進而降低生產成本。

例如,FOWLP采用旋轉涂布工藝,PI、PR等光敏材料(價格昂貴)的有效利用率只有20%。FOPLP采用狹縫涂布工藝,材料有效利用率達到85%以上。

2、高靈活性。

FOPLP的生產靈活性更高,適合大批量生產,生產周期更短。

例如,FOWLP封裝中,光罩的尺寸小,單次曝光面積有上限,需要通過拼接的方式曝光,效率低,良率低,影響產能。

而FOPLP封裝,單次曝光面積是FOWLP的4倍以上,效率高、良率高,大幅提升了產能。

3、優秀的熱管理。

通過優化封裝結構,以及選擇合適的材料,FOPLP可以有更好的散熱性能,降低芯片工作溫度,提高芯片的可靠性和壽命。

4、高集成度。

FOPLP在大面板上重新分布半導體芯片,能夠在單個封裝內集成多個芯片、無源元件和連接,可以實現更高的集成度,甚至更高的性能。

集成更多功能模塊,可以減少封裝步驟和材料消耗,也能降低成本。

5、高電氣性能。

FOPLP具有更低的電感和電容效應,電氣性能出色。

圖片來自亞智科技

當然,FOPLP也有缺點,包括面板尺寸和組裝工藝未能標準化、封裝密度較低(與FOWLP相比),以及芯片翹曲問題等。

目前,FOPLP板級封裝憑借剛才提到的優點,在射頻芯片、電源芯片、高頻芯片、傳感器芯片等領域展現了非常不錯的應用前景。

另外值得一提的,是FOPLP所使用的玻璃載板材料。

FOPLP載板的面積大,所以,在生產和處理的過程中,容易出現翹曲等問題。

所以,相比于傳統的硅材料,FOPLP的載板材料主要是金屬、玻璃或其它高分子聚合物材料。在這些材料之中,玻璃在機械、物理、光學等性能上具有明顯的優勢,現在已經成為行業關注的焦點。

玻璃基板的表面比塑料(有機材料)基板更光滑。在同樣面積下,能夠開孔(下期會提到的通孔)的數量也比塑料基板多。這極大提升了芯片之間的互連密度,有利于實現更復雜的設計,更有效地利用空間。

在熱學性能、物理穩定度方面,玻璃基板也表現出色,不容易因為溫度高而發生翹曲或變形。

玻璃基板的電氣性能也突出,介電損耗更低,電氣連接更穩定、高效。

-

晶圓級封裝

+關注

關注

5文章

41瀏覽量

11658 -

先進封裝

+關注

關注

2文章

472瀏覽量

612

原文標題:一文看懂芯片的封裝工藝之晶圓級封裝

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

封裝工藝中的晶圓級封裝技術

封裝工藝中的晶圓級封裝技術

評論