印制電路板的抗干擾設計與具體電路有著密切的關系,這里僅就PCB抗干擾設計的幾項常用措施做一些說明。

1.電源線設計:

根據印制線路板電流的大小,盡量加租電源線寬度,減少環路電阻。同時、使電源線、地線的走向和數據傳遞的方向一致,這樣有助于增強抗噪聲能力。

2.地線設計的原則:

(1)數字地與模擬地分開。若線路板上既有邏輯電路又有線性電路,應使它們盡量分開。低頻電路的地應盡量采用單點并聯接地,實際布線有困難時可部分串聯后再并聯接地。高頻電路宜采用多點串聯接地,地線應短而租,高頻元件周圍盡量用柵格狀大面積地箔。

(2)接地線應盡量加粗。若接地線用很紉的線條,則接地電位隨電流的變化而變化,使抗噪性能降低。因此應將接地線加粗,使它能通過三倍于印制板上的允許電流。如有可能,接地線應在2~3mm以上。

(3)接地線構成閉環路。只由數字電路組成的印制板,其接地電路布成團環路大多能提高抗噪聲能力。

3.退藕電容配置:

PCB設計的常規做法之一是在印制板的各個關鍵部位配置適當的退藕電容。退藕電容的一般配置原則是:

(1)電源輸入端跨接10~100uf的電解電容器。如有可能,接100uF以上的更好。

(2)原則上每個集成電路芯片都應布置一個0.01pF的瓷片電容,如遇印制板空隙不夠,可每4~8個芯片布置一個1~10pF的鉭電容。

(3)對于抗噪能力弱、關斷時電源變化大的器件,如RAM、ROM存儲器件,應在芯片的電源線和地線之間直接接入退藕電容。

(4)電容引線不能太長,尤其是高頻旁路電容不能有引線。

(5)在印制板中有接觸器、繼電器、按鈕等元件時.操作它們時均會產生較大火花放電,必須采用RC電路來吸收放電電流。一般R取1~2K,C取2.2~47UF。

(6) CMOS的輸入阻抗很高,且易受感應,因此在使用時對不用端要接地或接正電源。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

相關推薦

問題,如:TAS5711PCB布局排版主意那些事項,PVCC電源干擾到PLL補償以及I2S輸入,怎樣調整LRC解決抗干擾問題,現象描述:當聲音斷斷續續時,撥下供電插頭關閉主負載LED燈

發表于 10-31 07:41

印制電路板(PCB)是電子產品中電路元件和器件的支撐件,提供電氣連接。隨著電子技術發展,PCB 密度越來越高,其設計好壞對抗干擾能力影響大。

![的頭像]() 發表于

發表于 10-07 14:32

?227次閱讀

主要分為兩個方面:電路板布局(layout)的優化和板上頻率器件的隔離處理。 電路板布局的優化 在電路板設計中,合理的布局是提高晶振抗干擾能力的關鍵。以下是一些實用的布局技巧: 包地處

![的頭像]() 發表于

發表于 09-10 16:51

?634次閱讀

在變頻器上安裝抗干擾磁環是提升設備電磁兼容性和穩定性的重要措施。以下將介紹如何正確安裝抗干擾磁環在變頻器上,包括選擇合適的磁環、安裝位置、安裝步驟及注意事項等方面。 一、選擇合適的抗干擾磁環

![的頭像]() 發表于

發表于 08-21 09:50

?1801次閱讀

引言 可控硅觸發電路是電力電子技術中的一種重要電路,廣泛應用于電力系統、工業控制、家用電器等領域。然而,由于可控硅觸發電路的抗干擾能力較差,容易受到外部

![的頭像]() 發表于

發表于 07-31 09:46

?809次閱讀

為了提高PLC系統的抗干擾能力,應從設計入手。在具體工程的抗干擾設計中,可選擇抗干擾能力強的產品,通過抑制干擾源、切斷或衰減電磁干擾的傳輸路

![的頭像]() 發表于

發表于 07-19 08:50

?573次閱讀

stm32f105主控作為傳感器信號采集器,精度和抗干擾怎樣。。。。?模擬采樣的時候,外圍如何處理比較得當。。

現在做個東西,用INA128U 采集壓力傳感器0-50mV信號,

然后放大 ,LM258做信號跟隨,在用ad口采用 。。。

不知道這樣精度和穩定度

發表于 05-11 08:08

各位,有沒有用STM32做個大功率電源 ?最近要做個逆變器,以前的方案是用MICROCHIP做的,抗干擾和穩定性沒話說,就是有點貴。后來看到ST有個STM32F334,資源還不錯,價格也比較劃算

發表于 04-25 06:15

ZR執行器的抗干擾能力:穩定運行的關鍵-速程精密 在工業自動化領域,ZR執行器作為一種重要的終端設備,其性能的穩定性對于整個自動化系統的運行至關重要。而抗干擾能力作為ZR執行器穩定運行的關鍵因素之一

![的頭像]() 發表于

發表于 03-15 18:00

?516次閱讀

電磁干擾(EMI)問題日益成為影響單片機穩定性與可靠性的主要障礙。因此,探討和實施有效的抗干擾措施對于提高單片機系統的性能至關重要。下面為大家簡單介紹一種單片機抗干擾措施

![的頭像]() 發表于

發表于 03-15 16:36

?2586次閱讀

抗干擾磁環的原理及應用 為什么要設置抗干擾磁環?抗干擾磁環使用方法? 抗干擾磁環的原理及應用 1. 抗干擾磁環的原理:

![的頭像]() 發表于

發表于 03-14 15:46

?4367次閱讀

隨著CAN總線在電動汽車、充電樁、電力電子、軌道交通等電磁環境比較惡劣的場合應用越來越多,信號干擾的問題已經嚴重影響到使用者對CAN總線的信任。究竟如何才能抗干擾?本文展示了致遠電子CAN總線抗干擾

![的頭像]() 發表于

發表于 03-05 08:24

?1424次閱讀

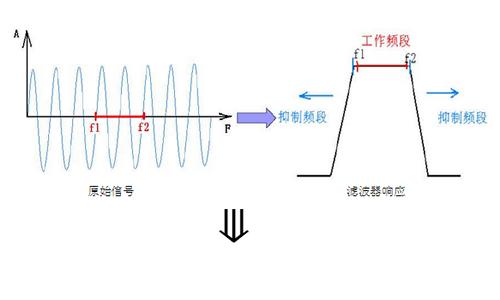

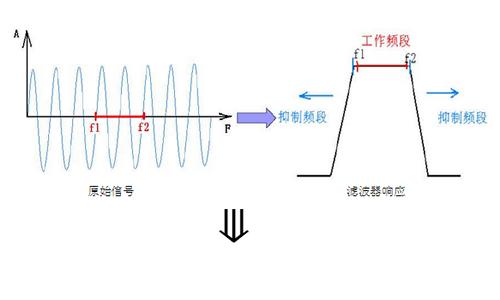

抗干擾濾波器主要用于電磁環境復雜情況下的干擾,防止多信道共址工作時的互調、交調干擾,

![的頭像]() 發表于

發表于 02-22 15:50

?2049次閱讀

壓力傳感器的接口電路中做好抗干擾性的設計方案,凡是壓力傳感器接口電路都存在小信號處理問題,因為傳感器的輸出一般都是小信號,將其放大到所需要的信號(如0~5),并能達到所需要的技術指標,就必須注意到

![的頭像]() 發表于

發表于 02-05 17:33

?737次閱讀

來自一位客戶的咨詢,麻煩幫忙解答,越詳細越好,有圖有真相,可以適當提供一些英飛凌解決方案和產品推薦。

現如今無線通信設備這么多,怎樣才能驗證ADAS功能的抗干擾能力?

發表于 02-02 07:20

pcb電路怎樣抗干擾

pcb電路怎樣抗干擾

評論