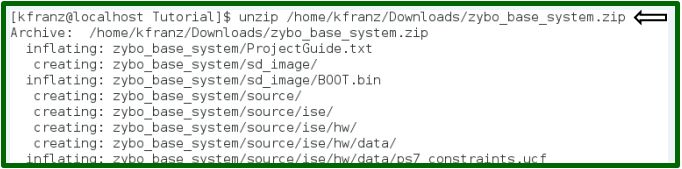

第1步:下載基本系統(tǒng)

從網(wǎng)站上下載Zybo基本系統(tǒng)設(shè)計(jì)并將其解壓縮到我們的工作目錄中(在本教程中,我們的工作目錄稱為教程)。有關(guān)硬件設(shè)計(jì)的更多信息,請(qǐng)參閱doc文件夾下的Project Guide。

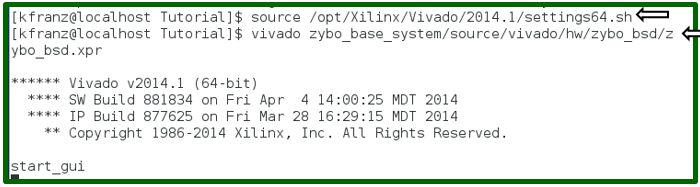

步驟2:打開(kāi)基本系統(tǒng)設(shè)計(jì)

獲取Vivado 2014.1設(shè)置并使用Vivado Design Suite(vivado)打開(kāi)設(shè)計(jì)。您將看到Vivado窗口彈出。

注意:Vivado工具集中有四個(gè)可用的設(shè)置文件:settings64.sh,可用于具有bash的64位計(jì)算機(jī); settings32.sh,可在帶有bash的32位計(jì)算機(jī)上使用; settings32.csh,用于在具有C Shell的32位計(jì)算機(jī)上使用;和設(shè)置64.csh,可在具有C Shell的64位計(jì)算機(jī)上使用。

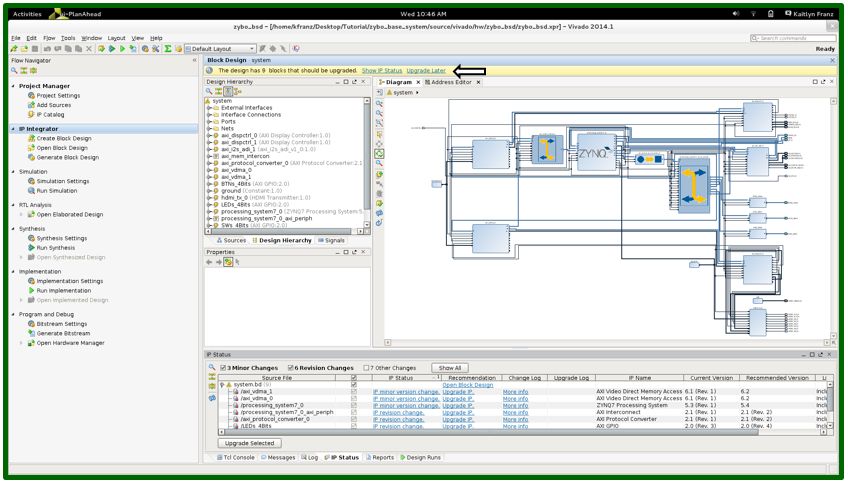

步驟3:刪除現(xiàn)有的LED內(nèi)核

我們將首先從PS中的GPIO內(nèi)核分離LED。因此,我們需要單擊IP集成器并打開(kāi)此步驟中第一張圖所示的框圖。然后,我們需要?jiǎng)h除第二個(gè)圖像中所示的當(dāng)前LED IP。我們將在后續(xù)步驟中處理外部引腳位置配置(xdc文件)的修改。

注意:在圖4中,有一個(gè)黃色欄表示需要升級(jí)。要升級(jí)熱門節(jié)目的顯示IP狀態(tài),請(qǐng)確保所有內(nèi)容均已選中,然后點(diǎn)擊“升級(jí)所選內(nèi)容”。

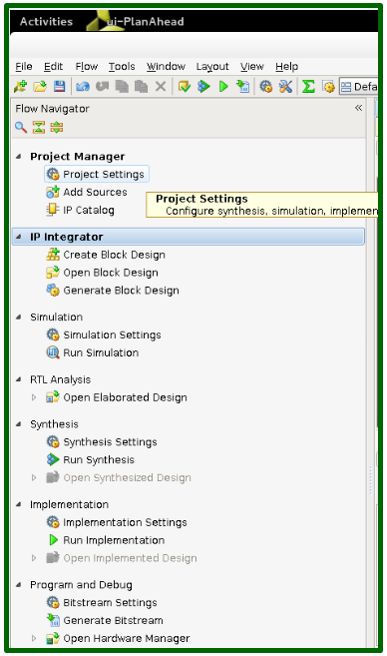

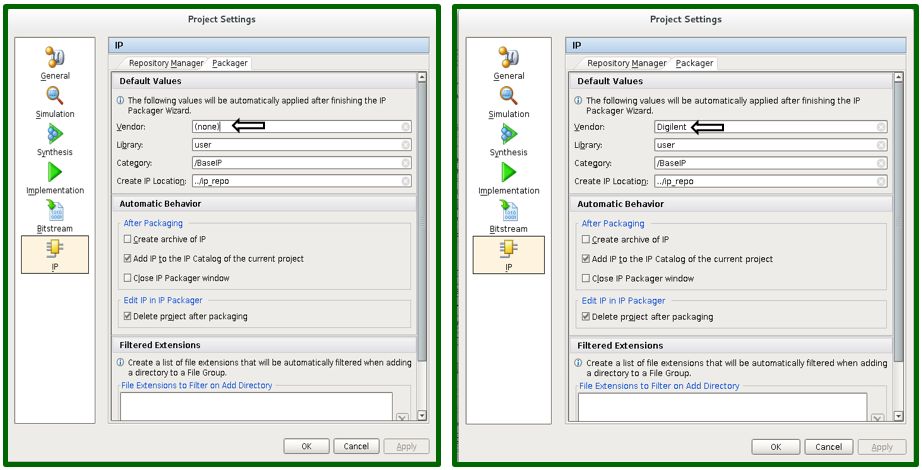

步驟4:命名供應(yīng)商

在開(kāi)始實(shí)施myLed IP內(nèi)核之前,我們需要命名將自動(dòng)應(yīng)用于IP打包程序中的供應(yīng)商。在Vivado 2014.1中,不會(huì)自動(dòng)為您完成此操作。為此,請(qǐng)首先轉(zhuǎn)到窗口左側(cè)項(xiàng)目管理器下的項(xiàng)目設(shè)置(圖1),然后將彈出項(xiàng)目設(shè)置窗口。在“項(xiàng)目設(shè)置”窗口中,選擇IP(圖像2)。請(qǐng)注意,將供應(yīng)商選擇為(無(wú)),這將導(dǎo)致Vivado內(nèi)部異常。您可以隨意命名供應(yīng)商(圖3)。

步驟5:創(chuàng)建MyLed IP

《現(xiàn)在,我們可以開(kāi)始實(shí)施myLed IP內(nèi)核了。從菜單中單擊工具-》創(chuàng)建和打包IP…(圖像1)。將彈出“創(chuàng)建并打包新IP”窗口(圖2),單擊“下一步”。在下一個(gè)窗口中為新IP命名,然后再次單擊下一步(圖像3)。

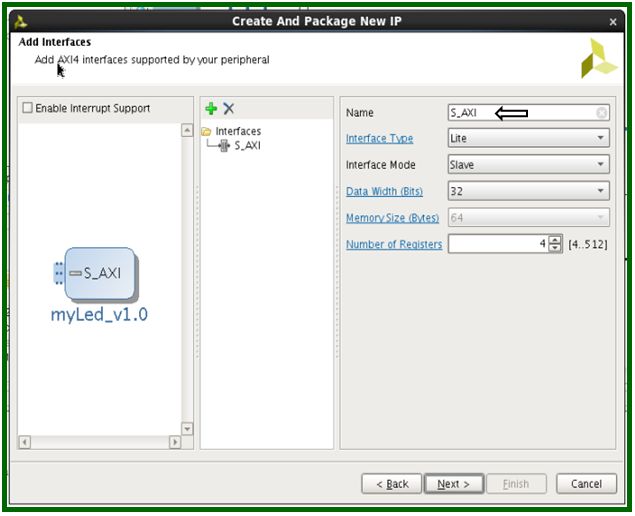

步驟6:添加接口

下一個(gè)窗口將是“添加接口”窗口。這將為myLed外設(shè)創(chuàng)建AX14接口。確保接口類型為L(zhǎng)ite,模式為Slave,數(shù)據(jù)寬度為32位,寄存器數(shù)量為4。將名稱更改為S_AXI而不是S00_AXI。我們只需要1個(gè)寄存器,但是我們可以選擇的最小值是4。然后單擊下一步。

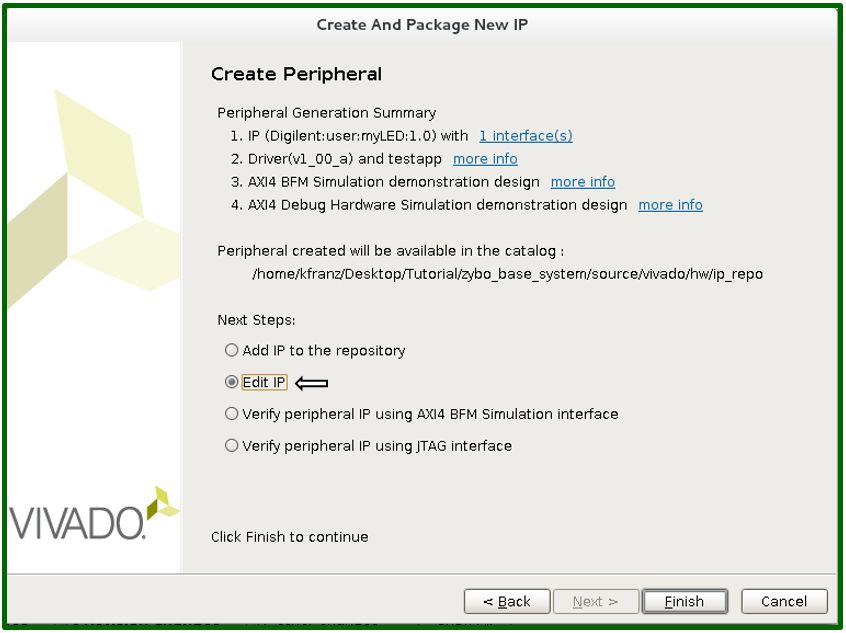

步驟7:編輯IP

下一個(gè)窗口將提示您完成創(chuàng)建IP的后續(xù)步驟。更改單選按鈕以選擇“編輯IP,然后單擊完成”。我們需要向IP添加用戶邏輯,以便我們的從設(shè)備連接到LED輸出。

步驟8:

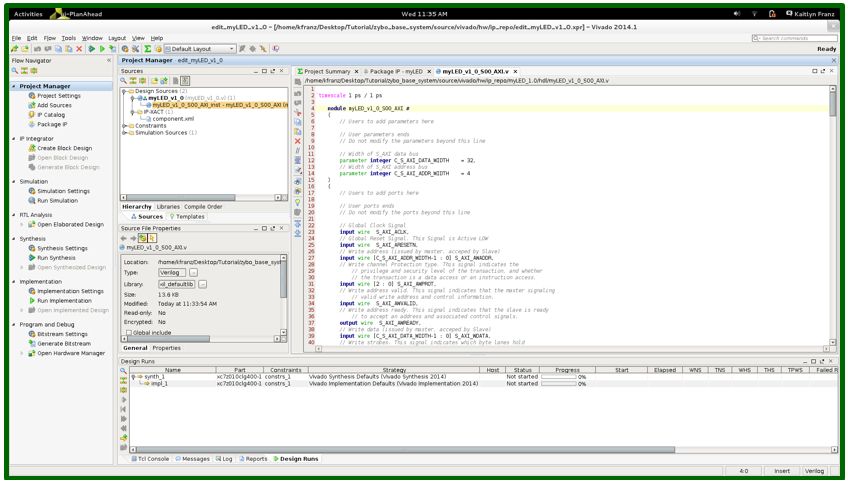

選擇完成后,“創(chuàng)建和打包IP”窗口將消失,您將看到的下一個(gè)窗口是edit_myLed窗口。這是我們將添加用戶邏輯的地方。

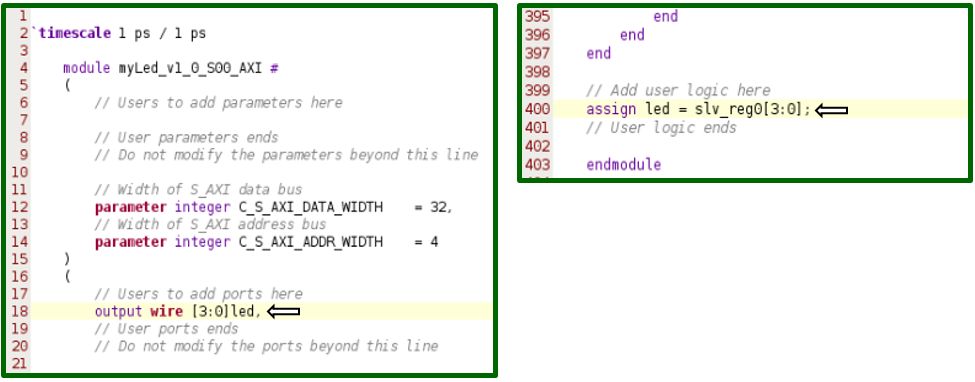

步驟9:MyLed_v1_0_S_AXI

在項(xiàng)目中管理員,點(diǎn)擊myLed_v1_0旁邊的圓圈,然后突出顯示myLed_v1_0_S_AXI(圖1)。這包含myLed IP內(nèi)部的用戶邏輯。我們需要添加兩行代碼來(lái)完成該模塊的用戶邏輯。首先,我們需要?jiǎng)?chuàng)建一個(gè)名為led的用戶端口(圖2)。接下來(lái),我們需要將內(nèi)部從設(shè)備連接到該用戶端口。我們將連接slv_reg0 [3:0],因?yàn)槲覀冇兴膫€(gè)LED(圖像3)。

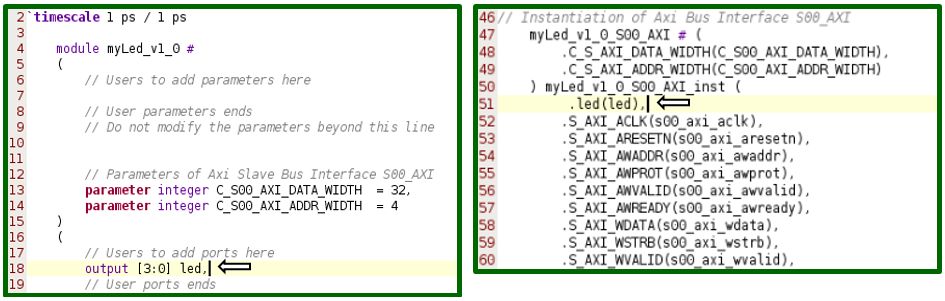

步驟10:MyLed_v_0

接下來(lái),我們需要將用戶邏輯連接到myLed。在項(xiàng)目管理器中,選擇文件myLed_v_0。要完成IP,我們需要在此文件中添加兩行代碼。在“用戶在此處添加端口”的注釋下,為L(zhǎng)ED添加一個(gè)端口(圖1)。將前一個(gè)包含用戶邏輯的文件的led輸出連接到myLed(圖像2)。

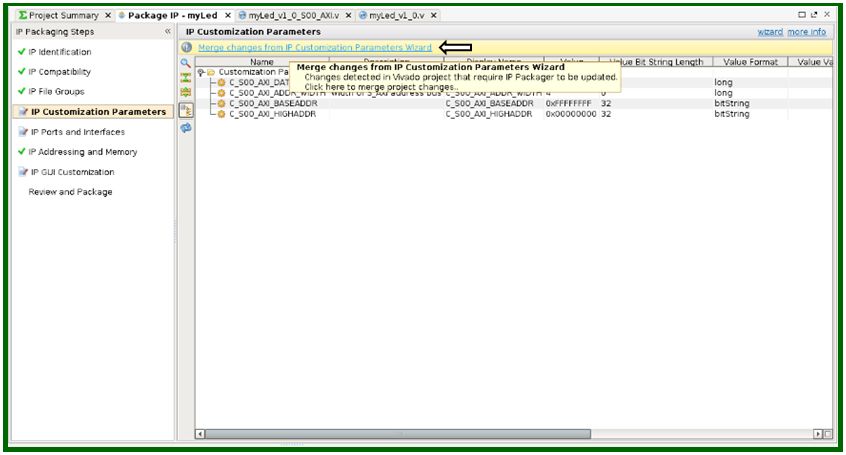

步驟11:程序包IP

現(xiàn)在,我們已經(jīng)創(chuàng)建了IP,并定義了用戶邏輯,我們需要打包IP。在窗口左側(cè)的“項(xiàng)目管理器”下,選擇“包IP”。將打開(kāi)一個(gè)新的選項(xiàng)卡,稱為“程序包IP”。在此水龍頭的左側(cè)有一系列標(biāo)簽。我們需要完成沒(méi)有綠色復(fù)選標(biāo)記的內(nèi)容。

首先選擇IP自定義參數(shù)。在該窗口的頂部,選擇“從IP自定義參數(shù)向?qū)е泻喜⒏摹钡倪x項(xiàng)。

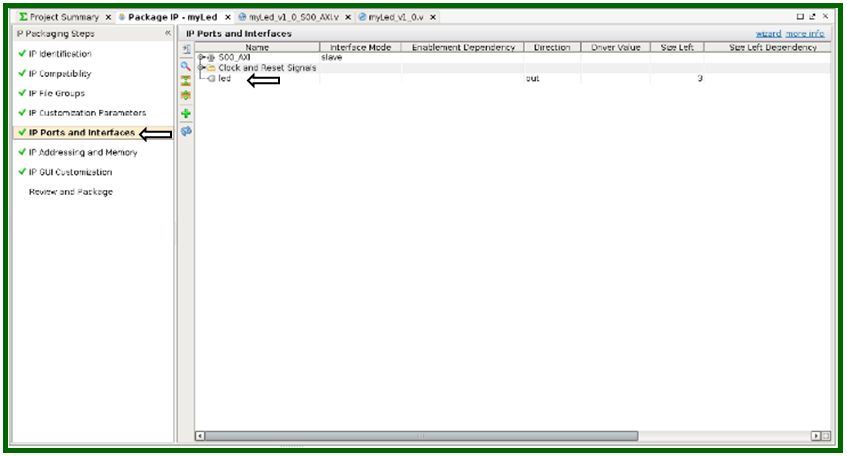

步驟12:端口和接口

下一步選擇IP端口和接口。請(qǐng)注意,您的新LED IP在那里。

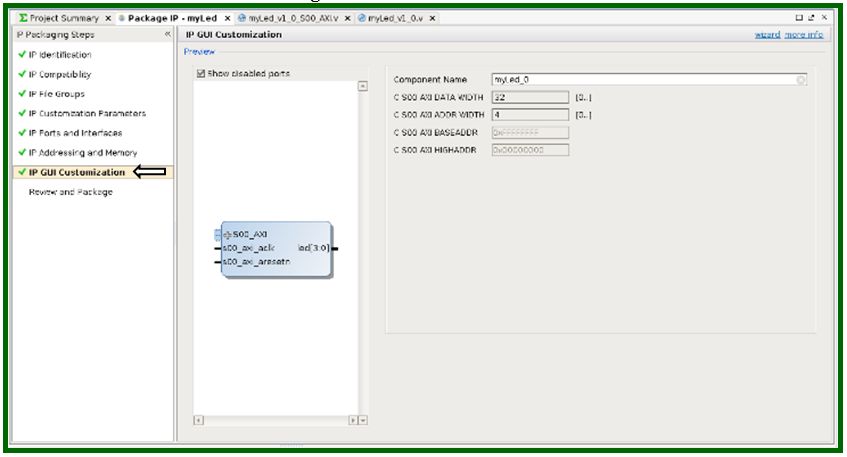

步驟13:IP GUI自定義

下一步選擇IP GUI自定義。我們的IP GUI很好,因此我們?cè)谶@里不會(huì)進(jìn)行任何更改。

現(xiàn)在,我們可以查看和打包myLed IP。選擇查看并打包IP,然后按重新打包IP按鈕。我們的IP現(xiàn)在已完成并打包。

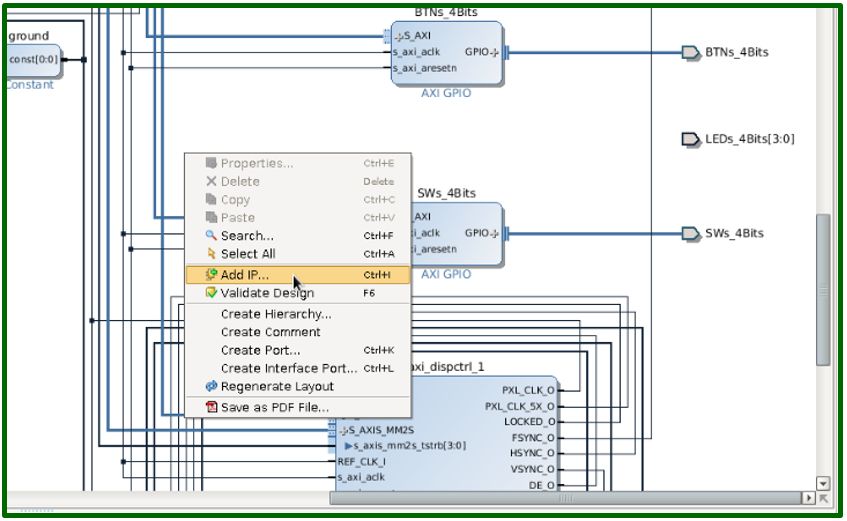

步驟14:添加MyLed IP

將我們的IP添加到我們的設(shè)計(jì)中。右鍵單擊模塊設(shè)計(jì)上的任意位置,然后單擊添加IP(圖1)。選擇正確的IP myLed_v1.0,然后按Enter鍵(圖像2)。

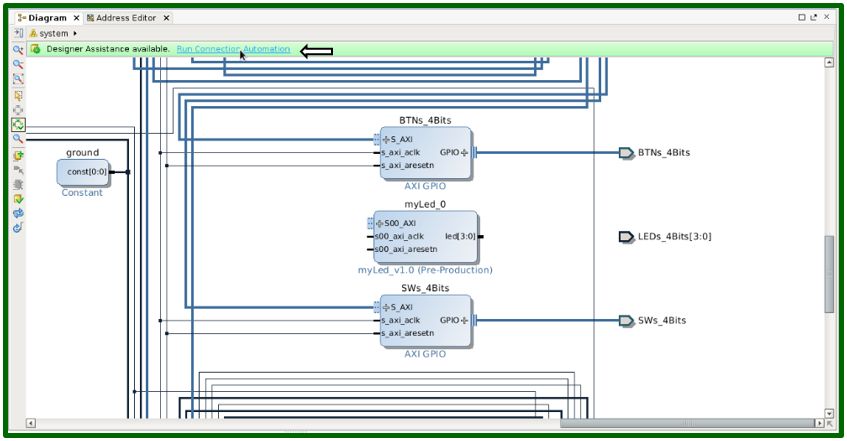

步驟15:運(yùn)行連接自動(dòng)化

myLed IP Core的AXI4-Lite總線需要連接到處理系統(tǒng)。在窗口頂部,單擊顯示運(yùn)行連接自動(dòng)化的藍(lán)色文本。這將連接myLed IP內(nèi)核的輸入。您應(yīng)該看到S_AXI現(xiàn)在已連接到AXI互連的第一個(gè)輸出。

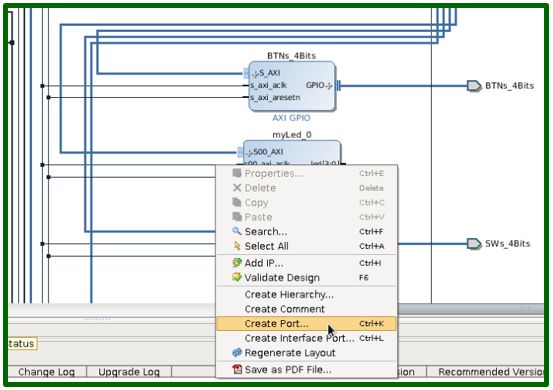

步驟16:創(chuàng)建LED端口

接下來(lái),我們需要將myLed IP連接到外部端口。我們實(shí)現(xiàn)的myLed IP內(nèi)核不會(huì)連接到現(xiàn)有的LEDs_4Bits端口,因此我們需要?jiǎng)?chuàng)建一個(gè)名為led的新外部端口。單擊現(xiàn)有的LED端口,然后按Delete鍵。要?jiǎng)?chuàng)建新端口,請(qǐng)右鍵單擊并選擇創(chuàng)建端口。命名端口,選擇輸出,選擇向量[3:0],然后按Enter。

步驟17:連接LED端口

下一步,通過(guò)單擊端口并將led連接拖到myLed上,將led端口連接到myLed IP。

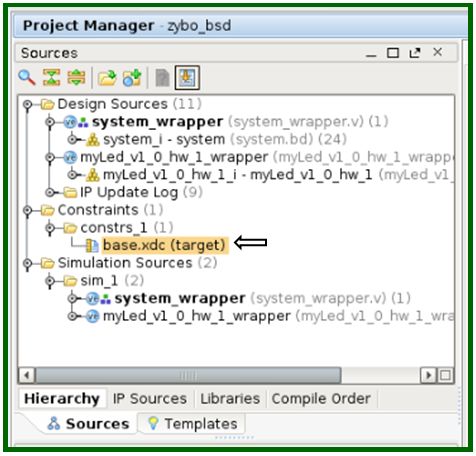

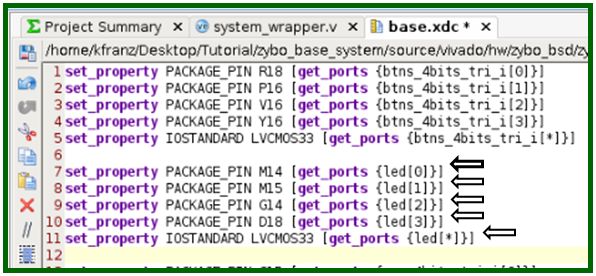

步驟18:修改XDC

最后一步是指定myled_0_LED_pin的引腳號(hào),以將我們定制的IP內(nèi)核物理連接到板載LED。在項(xiàng)目管理器中,展開(kāi)“約束”部分,然后選擇base.xdc文件(圖1)。在該文件中,更改外部LED引腳的名稱,以使其與我們的外部LED端口的名稱匹配(圖像2)。

步驟19:生成比特流

通過(guò)單擊窗口左側(cè)“程序和調(diào)試”下的“生成比特流”,為硬件設(shè)計(jì)重新生成比特流。

步驟20:U-Boot源代碼

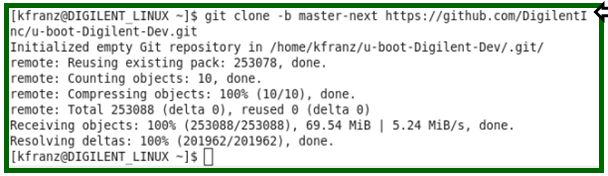

**注:使用主分支-下一分支直到另行通知

獲取Digilent git存儲(chǔ)庫(kù)中U-Boot的源代碼。有兩種方法可以檢索源代碼:

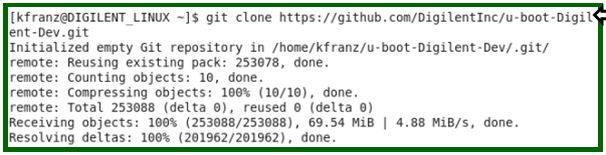

使用git命令:

如果您的發(fā)行版中安裝了git,則可以通過(guò)命令git clone https將存儲(chǔ)庫(kù)克隆到計(jì)算機(jī)上。 ://github.com/Digilent/u-boot-Digilent-Dev.g 。..整個(gè)Git存儲(chǔ)庫(kù)約為55MB,如圖1所示。如果您想獲得一個(gè)單獨(dú)的分支,例如下一個(gè)分支圖2.下一個(gè)包含尚未發(fā)布的u-boot。上面引用的克隆URL可以在Digilent git-hub頁(yè)面上找到,如圖3所示。

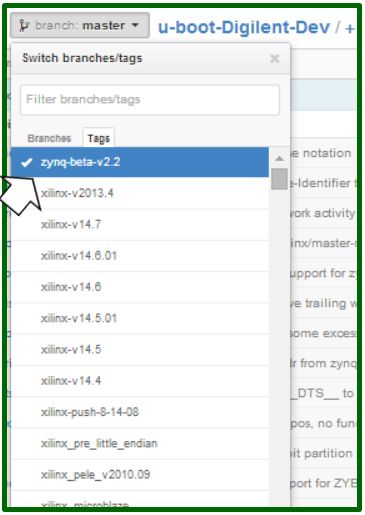

下載壓縮包:

如果只想使用一次u-boot如果不想跟蹤更新,也可以從github.com下載壓縮包:https://github.com/Digilent/u-boot-digilent。轉(zhuǎn)到顯示分支的下拉框,然后選擇標(biāo)簽。最新標(biāo)簽是zynq-beta-v2.2。 (圖4)。

如果下載了tar.gz,則可以使用命令

tar zxvf u-boot-digilent-2012.04-digilent-13.01.tar.gz解壓縮

如果下載了zip文件,則可以使用命令

unzip u-boot-digilent-2012.04-digilent-13.01.zip

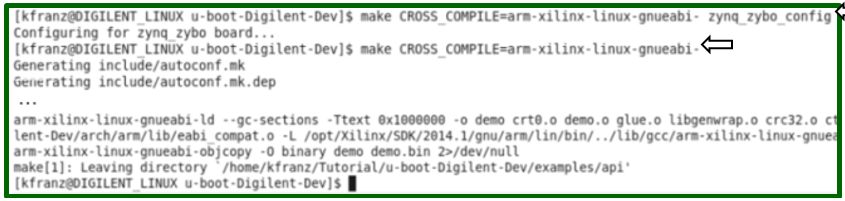

步驟21:編譯U-Boot

要編譯U-Boot,我們需要Vivado 2014.1提供的交叉編譯工具。這些工具在GCC工具鏈的標(biāo)準(zhǔn)名稱前有一個(gè)前綴arm-xilinx-linux-gnueabi-。前綴引用所使用的平臺(tái)。 Zybo板有兩個(gè)臂芯,因此我們參考了臂。為了使用跨平臺(tái)編譯器,請(qǐng)確保已獲取Vivado 2014.1設(shè)置。如果沒(méi)有,請(qǐng)參考步驟2。要為Zybo配置和構(gòu)建U-Boot,請(qǐng)遵循此步驟附帶的映像。

步驟22:U-boot.elf

編譯后,

生成的ELF(可執(zhí)行和可鏈接文件)被稱為u-boot。我們需要在文件名中添加.elf擴(kuò)展名,以便Xilinx SDK可以讀取文件布局并生成BOOT.BIN。在本教程中,我們將把u-boot.elf移到sd_image文件夾,并替換Zybo基本系統(tǒng)設(shè)計(jì)包隨附的u-boot.elf。

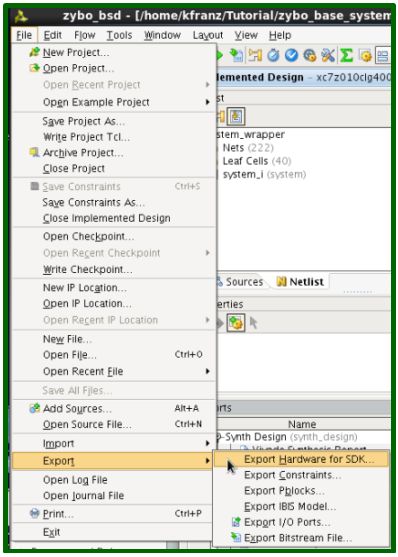

步驟23:導(dǎo)出SDK的硬件

通過(guò)單擊文件-》導(dǎo)出-》導(dǎo)出,將硬件設(shè)計(jì)(步驟I-16之后)導(dǎo)出到Xilinx SDK。 SDK的硬件…,如第一幅圖所示。

將工作區(qū)保留為。確保已選中Launch SDK,然后單擊“確定”,如第二幅圖像所示。

注意:您可能必須導(dǎo)出兩次。

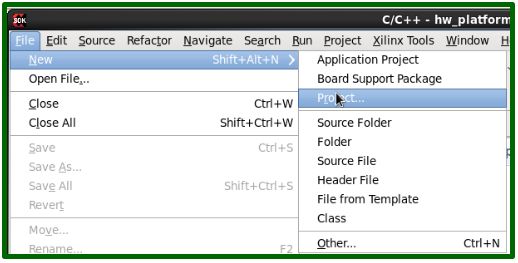

步驟24:新建項(xiàng)目

SDK啟動(dòng)后,硬件平臺(tái)項(xiàng)目已經(jīng)出現(xiàn)在SDK主窗口左側(cè)的Project Explorer中,如圖1所示。現(xiàn)在,我們需要?jiǎng)?chuàng)建一個(gè)第一階段引導(dǎo)加載程序(FSBL)。單擊File-》 New-》 Project…,如圖2所示。

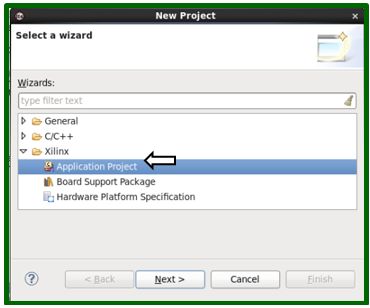

步驟25:應(yīng)用程序項(xiàng)目

在新建項(xiàng)目窗口,選擇Xilinx-》應(yīng)用程序項(xiàng)目,然后單擊下一步。

步驟26:將項(xiàng)目命名為FSBL

我們將項(xiàng)目命名為FSBL。為目標(biāo)硬件選擇hw_platform_0,因?yàn)樗俏覀儎倓倢?dǎo)出的硬件項(xiàng)目。為OS平臺(tái)選擇獨(dú)立。單擊下一步。

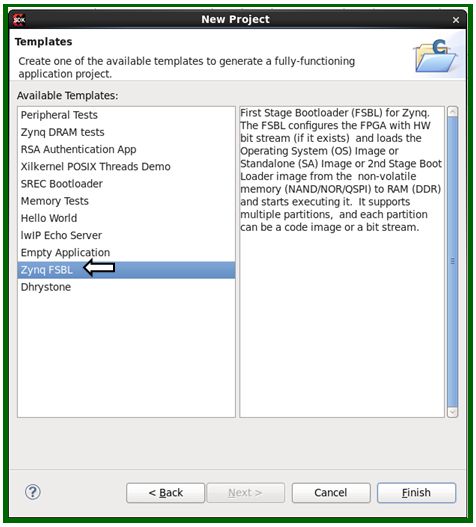

步驟27:創(chuàng)建Zynq FSBL模板

選擇Zynq FSBL作為模板,然后單擊完成。

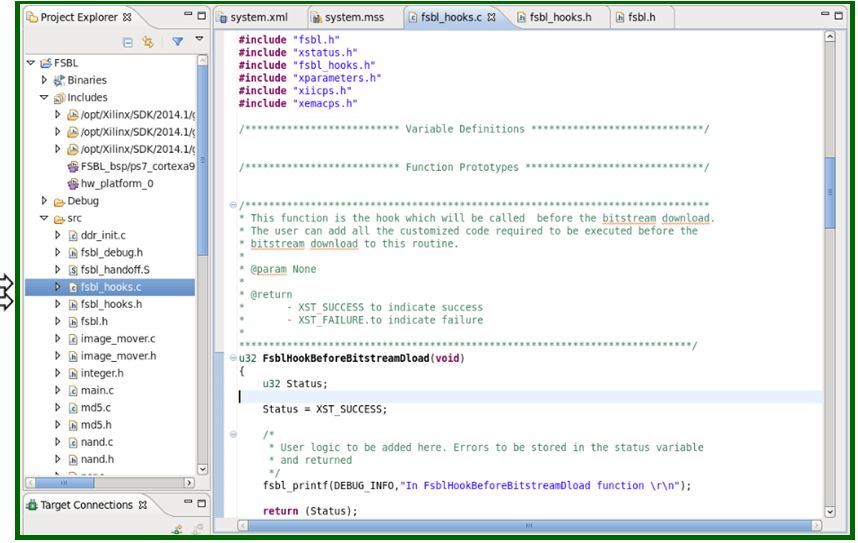

步驟28:FSBL掛鉤

對(duì)于Zybo,我們需要在fsbl掛鉤中設(shè)置以太網(wǎng)的mac地址。我們希望關(guān)閉和打開(kāi)Zybo板時(shí)以太網(wǎng)的mac地址保持不變。您可以將FSBL項(xiàng)目中的fsbl_hooks.c文件與Zybo基本系統(tǒng)設(shè)計(jì)中source/vivado/SDK/fsbl下的fsbl_hooks.c交換。

將更改保存到fsbl_hooks.c后,

該項(xiàng)目將自動(dòng)重建自身。如果不重建,請(qǐng)單擊Project-》 Clean清理項(xiàng)目文件,然后單擊Project-》 Build All重建所有項(xiàng)目。編譯的ELF文件位于zybo_base_system/source/vivado/hw/zybo_bsd.sdk/SDK/SDK_Export/FSBL/Debug

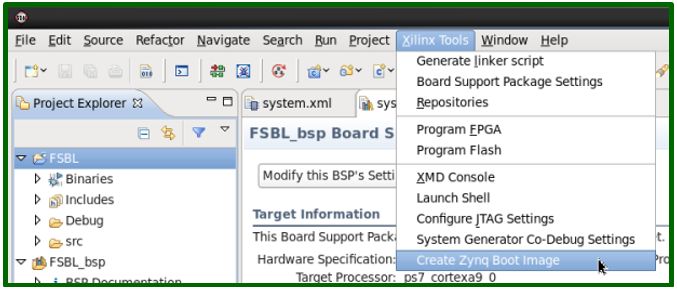

步驟29:創(chuàng)建啟動(dòng)映像

現(xiàn)在,我們已經(jīng)準(zhǔn)備好所有文件來(lái)創(chuàng)建BOOT.BIN。單擊Xilinx工具-》創(chuàng)建Zynq引導(dǎo)映像。

第30步:添加FSBL,System.bit和U-boot.elf

在“創(chuàng)建Zynq引導(dǎo)映像”窗口中,單擊“瀏覽”以設(shè)置FSBL elf的路徑。單擊添加以添加位于/zybo_base_system/source/vivado/hw/zybo_bsd/zybo_bsd.sdk/SDK/SDK_Export/hw_platform_0/的system.bit文件。單擊添加以添加位于zybo_base_system/sd_image/的u-boot.elf文件。 。按順序添加3個(gè)文件非常重要,否則FSBL將無(wú)法正常工作。將FSBL.elf設(shè)置為引導(dǎo)程序,將system.bit和u-boot.elf設(shè)置為數(shù)據(jù)文件也非常重要。在本教程中,sd_image文件夾被設(shè)置為BIN文件的輸出文件夾。單擊創(chuàng)建映像。

步驟31:Linux內(nèi)核源代碼

**注意:使用母版-Next分支直到另行通知

從Digilent git存儲(chǔ)庫(kù)獲取Linux內(nèi)核源代碼。有兩種方法可以檢索源代碼:

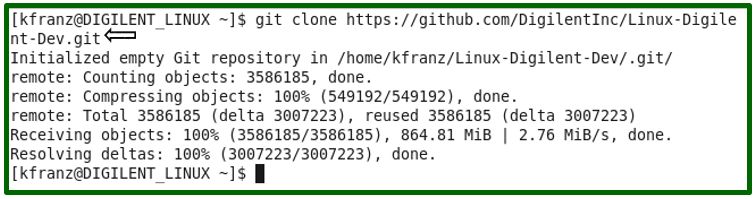

使用git命令:如果您的發(fā)行版中安裝了git,則可以通過(guò)命令git clone https://github.com/將存儲(chǔ)庫(kù)克隆到計(jì)算機(jī)上。 DigilentInc/Linux-Digilent-Dev 。..整個(gè)Git存儲(chǔ)庫(kù)約為850MB,如圖1所示。

下載壓縮包:如果您只想使用一次u-boot,并且不想要跟蹤更新,您還可以從github.com下載壓縮包:https://github.com/DigilentInc/Linux-Digilent-Dev。單擊頁(yè)面右上角的標(biāo)簽。最新標(biāo)簽是zynq-dt-for-3.14(圖2)。

如果下載了tar.gz,則可以使用命令

tar zxvf linux-digilent-v3.6-digilent-13.01.tar.gz

如果下載了zip文件,則可以使用命令將其解壓縮

解壓縮linux-digilent-v3.6-digilent-13.01.zip

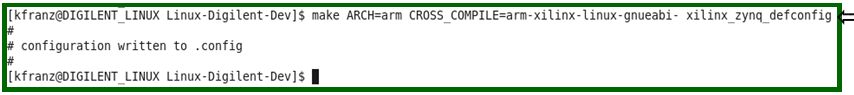

第32步:配置內(nèi)核

我們將開(kāi)始使用Zybo的默認(rèn)配置來(lái)配置內(nèi)核。該配置位于arch/arm/configs/xylinx_zynq_defconfig。要使用默認(rèn)配置,請(qǐng)遵循此步驟所附的圖像。

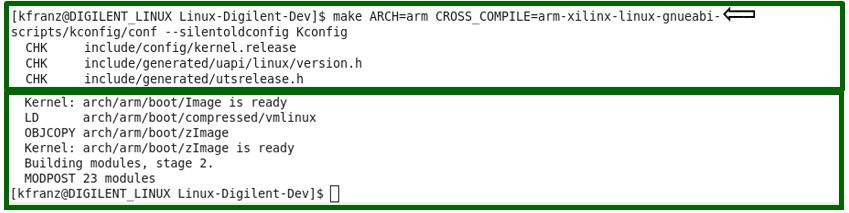

步驟33:編譯Linux內(nèi)核

按照示例進(jìn)行操作

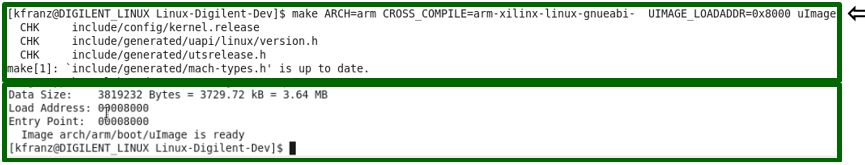

步驟34:制作Uimage

編譯后,內(nèi)核映像位于arch/arm/開(kāi)機(jī)/的zImage。但是,在這種情況下,內(nèi)核映像必須是uimage(解壓縮)而不是zimage。要使uimage跟隨此步驟中的圖像。

步驟35:可選的路徑更改

注意:取決于您的分布在Linux上,您可能會(huì)得到有關(guān)mkimage路徑的錯(cuò)誤。如果是這種情況,您可以在此步驟中更改圖像后的路徑。

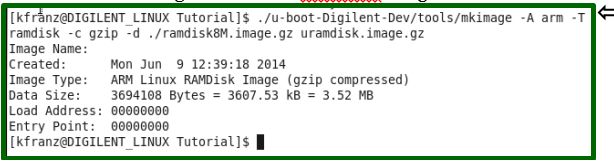

步驟36:制作Uramdisk

到在Zybo上啟動(dòng)Linux操作系統(tǒng),您需要BOOT.BIN,Linux內(nèi)核映像(uImage),設(shè)備樹(shù)blob(DTB文件)和文件系統(tǒng)。在第三節(jié)中創(chuàng)建了BOOT.BIN,在第四節(jié)中編譯了uImage。現(xiàn)在,我們將編譯DTB文件。默認(rèn)設(shè)備樹(shù)源文件位于Linux內(nèi)核源文件中的arch/arm/boot/dts/zynq-zybo.dts。

RAMDISK:對(duì)于zynq,只有虛擬磁盤映像必須包裝在u中-boot標(biāo)頭,以便u-boot用它引導(dǎo)。該步驟顯示在該圖像中。

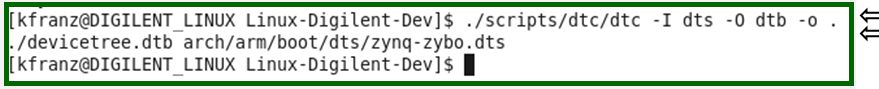

步驟37:生成DTB文件

按照?qǐng)D像中提供的示例進(jìn)行操作

步驟38:將文件映像復(fù)制到SD卡

RAMDISK)復(fù)制BOOT.BIN,將devicetree.dtb,uImage和uramdisk.image.gz移至SD卡的第一個(gè)分區(qū),如第一個(gè)映像– RamDisk中所示。

注意:SD卡的第一個(gè)分區(qū)已安裝到/media/ZYBO_BOOT

步驟39:從SD卡啟動(dòng)

將SD卡插入Zybo。要從SD卡引導(dǎo),需要按照Z(yǔ)ybo板上所示為USB配置跳線7,并且必須將跳線5連接到SD。使用微型USB電纜將UART端口連接到PC,并將PC上的UART端子設(shè)置為115200波特率,8個(gè)數(shù)據(jù)位,1個(gè)停止位,無(wú)奇偶校驗(yàn)和無(wú)流量控制。板上電后,如果使用RamDisk,則應(yīng)該在UART終端上看到控制臺(tái)。有關(guān)此文件系統(tǒng)的更多信息,請(qǐng)參見(jiàn)《嵌入式Linux ZedBoard入門》。

步驟40:創(chuàng)建驅(qū)動(dòng)程序目錄

在Tutorial文件夾中創(chuàng)建一個(gè)名為drivers的目錄,如本步驟中的圖像所示。在drivers目錄中,我們將構(gòu)成myLed控制器的驅(qū)動(dòng)程序。

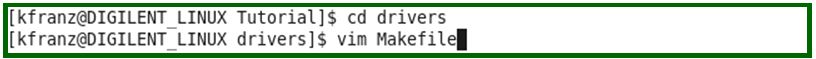

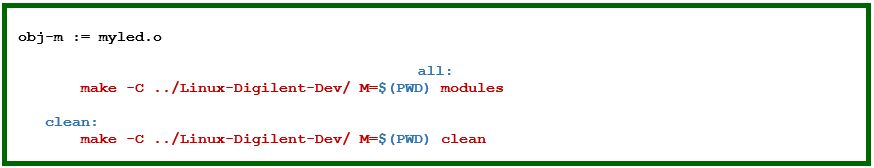

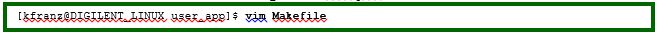

步驟41:創(chuàng)建Makefile

我們需要一個(gè)Makefile,以便我們可以編譯驅(qū)動(dòng)程序。 Makefile在圖像1中創(chuàng)建。

創(chuàng)建文件后,單擊I更改為插入模式,然后在圖像2中插入以下文本。請(qǐng)確保在適當(dāng)?shù)牡胤绞褂弥票矸?/p>

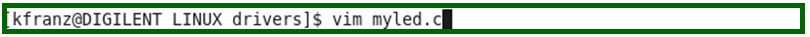

步驟42:創(chuàng)建Myled.c

我們將從一個(gè)簡(jiǎn)單的驅(qū)動(dòng)程序開(kāi)始,該驅(qū)動(dòng)程序在Linux/proc文件系統(tǒng)下創(chuàng)建一個(gè)名為myled的文件。可以通過(guò)在文件中寫入數(shù)字來(lái)更改板載LED的狀態(tài)。驅(qū)動(dòng)程序被編碼在最后四個(gè)圖像中,并被附加

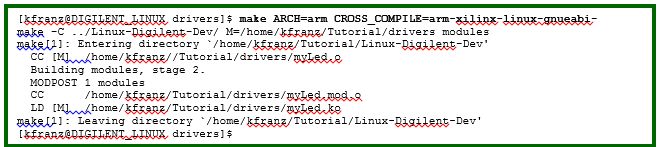

步驟43:編譯驅(qū)動(dòng)程序

編譯并生成驅(qū)動(dòng)程序模塊使用make。不要忘記來(lái)源Vivado設(shè)置。

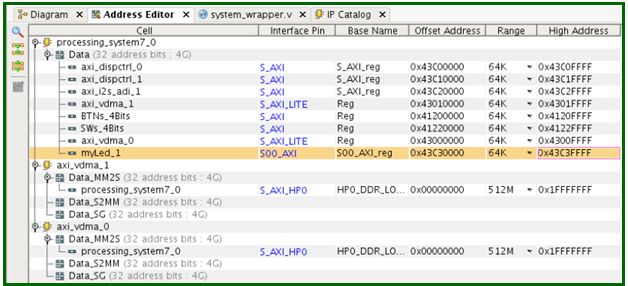

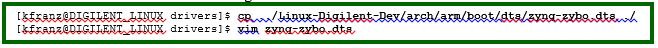

步驟44:將Myled添加到設(shè)備樹(shù)

我們需要將myLed設(shè)備節(jié)點(diǎn)添加到設(shè)備樹(shù)中。

在drivers文件夾中復(fù)制默認(rèn)設(shè)備樹(shù)源,然后根據(jù)第二個(gè)圖像對(duì)其進(jìn)行修改。節(jié)點(diǎn)的兼容性字符串與我們?cè)隍?qū)動(dòng)程序源代碼中定義的字符串相同(myled.c:第182行)。 reg屬性定義節(jié)點(diǎn)的物理地址和大小。如上圖所示,此處的地址應(yīng)與Vivado設(shè)計(jì)的地址編輯器選項(xiàng)卡中的myLed IP內(nèi)核的地址匹配。

步驟45:重新編譯設(shè)備樹(shù)Blob

重新編譯設(shè)備樹(shù)blob,如所附映像所示。

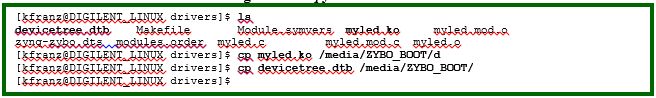

步驟46:將驅(qū)動(dòng)程序和修改后的設(shè)備樹(shù)復(fù)制到SD卡

將這兩個(gè)文件復(fù)制到SD的第一個(gè)分區(qū)卡,如該步驟中的圖像所示。我們現(xiàn)在就可以在板上測(cè)試驅(qū)動(dòng)程序了。

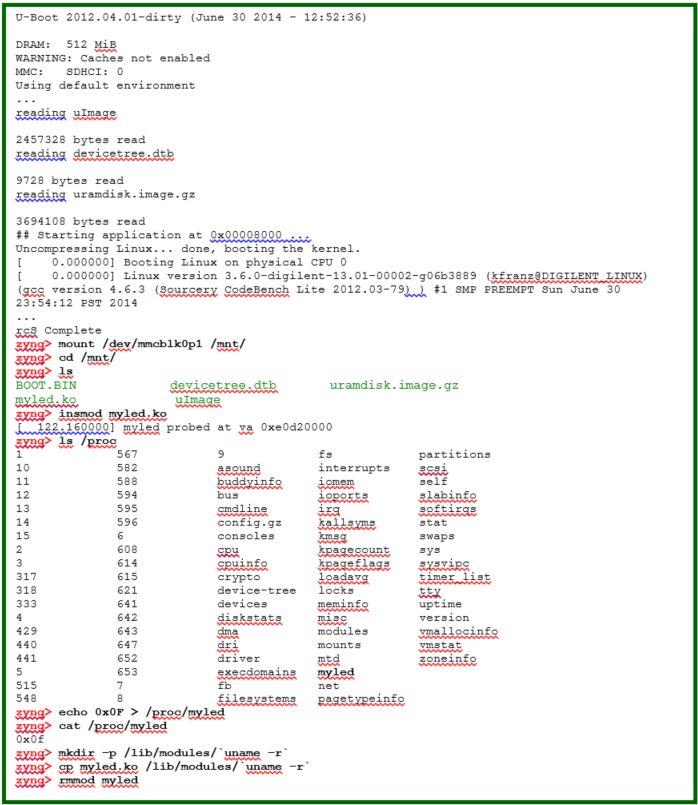

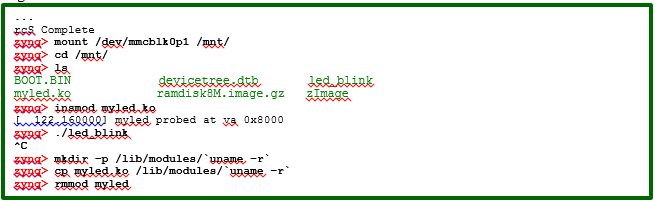

步驟47:從SD卡啟動(dòng)

插入SD卡進(jìn)入Zybo,我們就可以開(kāi)始測(cè)試驅(qū)動(dòng)程序了。使用insmod命令將驅(qū)動(dòng)程序模塊安裝到內(nèi)核中。安裝驅(qū)動(dòng)程序后,將在/proc文件系統(tǒng)下創(chuàng)建一個(gè)名為myled的條目。將0x0F寫入/proc/myled將點(diǎn)亮LED 0?3。您可以使用rmmod命令刪除驅(qū)動(dòng)程序,也可以通過(guò)poweroff命令關(guān)閉系統(tǒng)電源。在這兩種情況下,所有LED都將關(guān)閉,如圖69和70所示。有關(guān)將終端與Zybo一起使用的說(shuō)明。請(qǐng)參閱嵌入式Linux入門– ZedBoard中的步驟V-4或從SD引導(dǎo)部分。

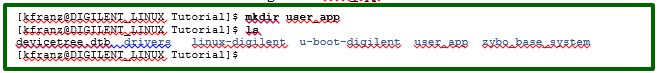

步驟48:用戶應(yīng)用程序:Led_blink

在本節(jié)中,我們將編寫一個(gè)用戶應(yīng)用程序,該應(yīng)用程序通過(guò)寫入/proc/myled來(lái)使LED閃爍

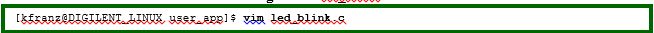

。如第一個(gè)圖像所示,在Tutorial文件夾中創(chuàng)建一個(gè)名為user_app的目錄。在user_app目錄中,我們將組成led_blink.c,如第二和第三張圖所示。

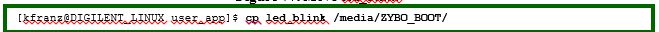

步驟49:創(chuàng)建Makefile并編譯Led_blink

組成一個(gè)Makefile并將led_blink.c編譯為led_blink.o,如本步驟中的三個(gè)圖像所示。

步驟50:

將SD卡插入計(jì)算機(jī),然后將二進(jìn)制文件led_blink復(fù)制到SD卡的第一個(gè)分區(qū)。

步驟51:運(yùn)行Led_blink

將SD卡插入ZYBO。使用insmod命令將驅(qū)動(dòng)程序模塊安裝到內(nèi)核中。運(yùn)行l(wèi)ed_blink,LED會(huì)開(kāi)始閃爍。

責(zé)任編輯:wv

-

Linux

+關(guān)注

關(guān)注

87文章

11469瀏覽量

212903 -

軟件

+關(guān)注

關(guān)注

69文章

5124瀏覽量

88979

發(fā)布評(píng)論請(qǐng)先 登錄

FX3為什么無(wú)法在Windows中使用Gstreamer?

不借助Linux系統(tǒng),在Windows下如何搭建ZMC900E交叉編譯環(huán)境

如何實(shí)現(xiàn)MC33774IC在Simulink環(huán)境中使用基于模型的設(shè)計(jì)?

Linux環(huán)境下的軟件包下載指令是什么呢?

Xilinx_Vivado_SDK的安裝教程

每次Vivado編譯的結(jié)果都一樣嗎

Linux應(yīng)用編程的基本概念

Linux環(huán)境變量配置方法

在綠色或便攜式環(huán)境中使用bq3285/7E

聚徽-工業(yè)一體機(jī)可以在怎樣的環(huán)境中使用

在反向電流應(yīng)用中使用比較器

在設(shè)計(jì)中使用MOSFET安全工作區(qū)曲線

怎樣在Linux環(huán)境中使用Vivado 2014.1 Webpack

怎樣在Linux環(huán)境中使用Vivado 2014.1 Webpack

評(píng)論