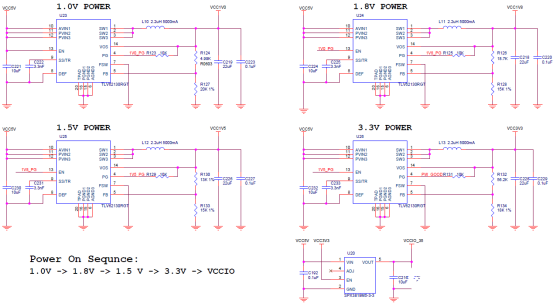

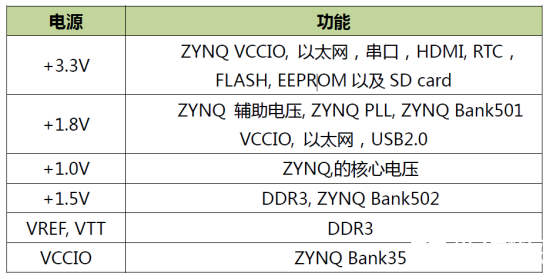

因?yàn)閆YNQ 的PS 和PL 部分的電源有上電順序的要求,在電路設(shè)計(jì)中,按照ZYQN 的電源要求設(shè)計(jì),上電依次為1.0V -> 1.8V -> 1.5 V -> 3.3V -> VCCIO,下圖為電源的電路設(shè)計(jì):

ZYNQ芯片的電源分PS系統(tǒng)部分和PL邏輯部分,兩部分的電源分別是獨(dú)立工作。PS系統(tǒng)部分的電源和PL邏輯部分的電源都有上電順序,不正常的上電順序可能會(huì)導(dǎo)致ARM系統(tǒng)和FPGA系統(tǒng)無法正常工作。

PS部分的電源有VCCPINT、VCCPAUX、VCCPLL和PS VCCO。

VCCPINT為PS內(nèi)核供電引腳,接1.0V;

VCCPAUX為PS系統(tǒng)輔助供電引腳,接1.8V;

VCCPLL為PS的內(nèi)部時(shí)鐘PLL的電源供電引腳,也接1.8V;

PS VCCO為BANK的電壓,包含VCCO_MIO0,VCCO_MIO1和VCCO_DDR,根據(jù)連接的外設(shè)不同,連接的電源電源也會(huì)不同,VCC_MIO0連接3.3V,VCCO_MIO1連接1.8V,VCCO_DDR連接1.5V。PS系統(tǒng)要求上電順序分別為先VCCPINT供電,然后VCCPAUX和VCCPLL,最后為PS VCCO。斷電的順序則相反。

PL部分的電源有VCCINT, VCCBRAM, VCCAUX和 VCCO。

VCCPINT為FPGA內(nèi)核供電引腳,接1.0V;

VCCBRAM為FPGA Block RAM的供電引腳;接1.0V;

VCCAUX為FPGA輔助供電引腳, 接1.8V;

VCCO為PL的各個(gè)BANK的電壓,包含BANK13,BANK34,BANK35,BANK的電壓連接3.3V。PL系統(tǒng)要求上電順序分別為先VCCINT供電,再是VCCBRAM, 然后是VCCAUX,最后為VCCO。如果VCCINT和VCCBRAM的電壓一樣,可以同時(shí)上電。斷電的順序則相反。

-

電源

+關(guān)注

關(guān)注

185文章

18329瀏覽量

255661 -

FPGA

+關(guān)注

關(guān)注

1644文章

22009瀏覽量

616579 -

Zynq

+關(guān)注

關(guān)注

10文章

614瀏覽量

48131

發(fā)布評(píng)論請先 登錄

Zynq的電源上電順序

Zynq的電源上電順序

評(píng)論