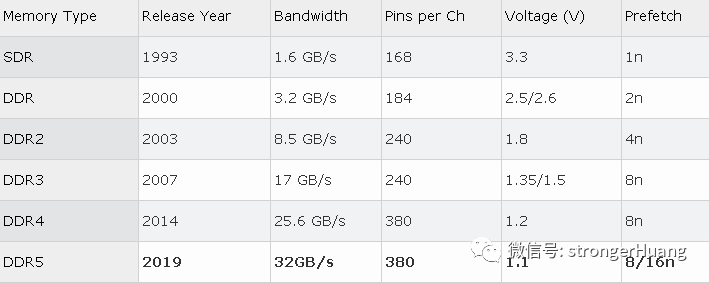

第五代雙倍數據率同步動態隨機存取存儲器(英語:double data rate fifth-generation synchronous dynamic random-access memory,縮寫DDR5 SDRAM)是一種正在開發的高帶寬電腦存儲器規格。它屬于SDRAM家族的存儲器產品。 一、DDR5發展歷史

2017年6月,負責計算機內存技術標準的組織JEDEC宣稱,下一代內存標準DDR5將亮相,并預計在2018年完成最終的標準制定。

2017年9月22日,Rambus宣布在實驗室中實現完整功能的DDR5 DIMM芯片,預期將在2019年開始量產。

2018年10月,Cadence和鎂光公布了自己的DDR5內存研發進度,兩家廠商已經開始研發16GB DDR5產品,并計劃在2019年年底之前實現量產目標。

二、DDR5的特性

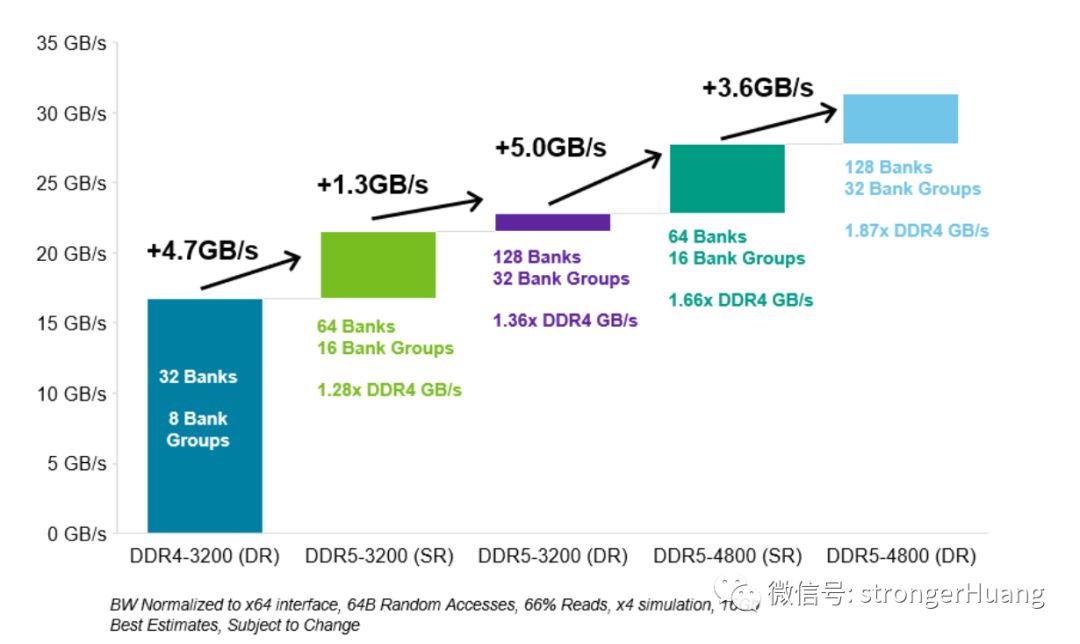

1.性能改進

2. 更省電

DDR5從DDR4 1.2V進一步降低到1.1V,可以更加省電。

3.更大容量

DDR5內存將從8GB容量起步,最高可達單條32GB。

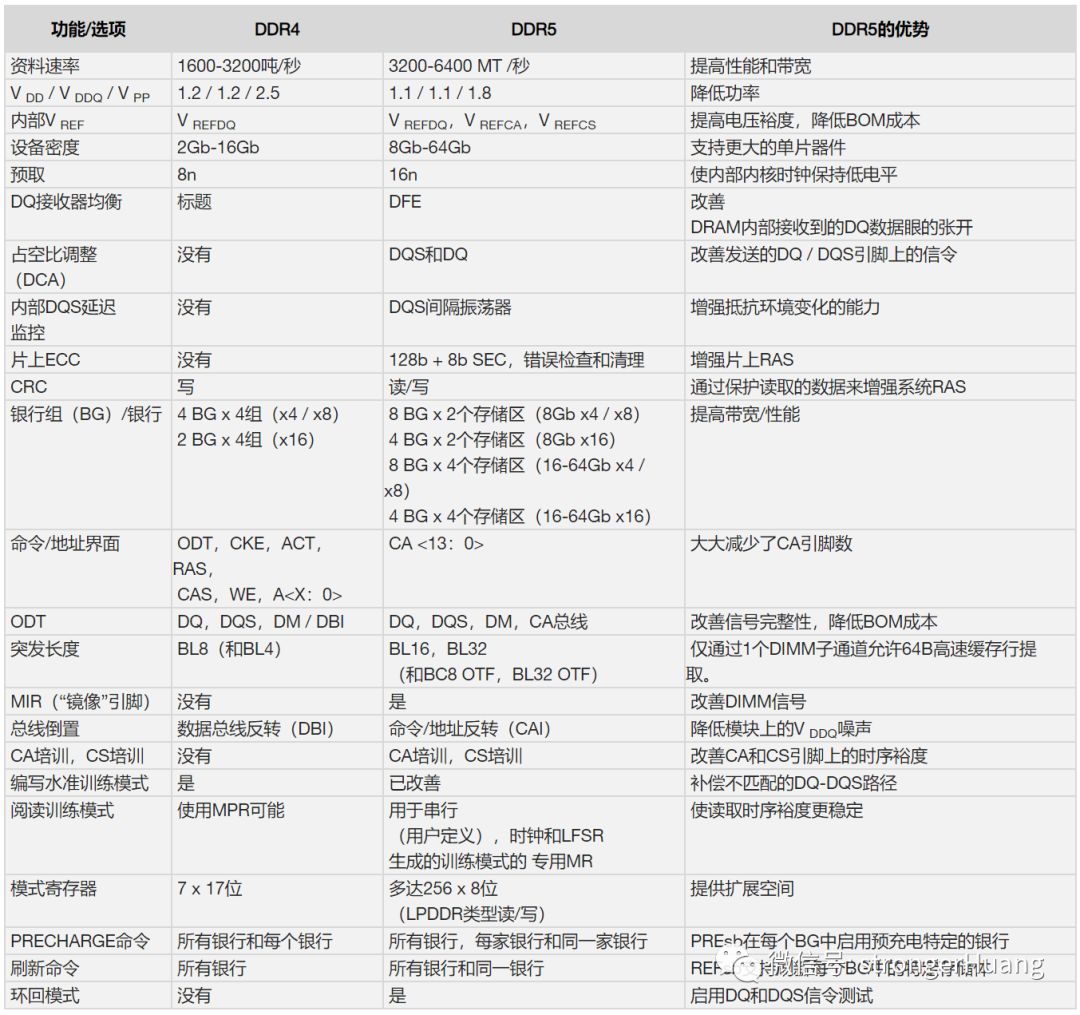

三、DDR5和DDR4對比DDR5是DRAM的下一步發展,帶來了一系列旨在增強可靠性,可用性和可維護性(RAS)的新功能。降低功率;并大大提高性能。DDR4和DDR5之間的一些關鍵功能差異如下:

-

DDR4

+關注

關注

12文章

333瀏覽量

41767 -

隨機存取存儲器

+關注

關注

0文章

45瀏覽量

9117 -

DDR5

+關注

關注

1文章

447瀏覽量

24902

發布評論請先 登錄

DDR4價格瘋漲!現貨市場狂飆!

漲價!部分DDR4與DDR5價差已達一倍!

上海貝嶺推出全新DDR5 SPD芯片BL5118

DDR5比較DDR4有什么新特性?

DDR5比較DDR4有什么新特性?

評論