何謂 I2C?

在本文中,您將了解有關內部集成電路總線(I2C 或 IIC)的基礎知識以及將此協議總線應用于短距離通信的方法。 I2C 屬于串行通信協議,供雙線接口用于連接 EEPROM、傳感器、RTC、ADC/DAC 等低速器件以及嵌入式系統中的其它兼容 I/O 接口。

I2C 簡介

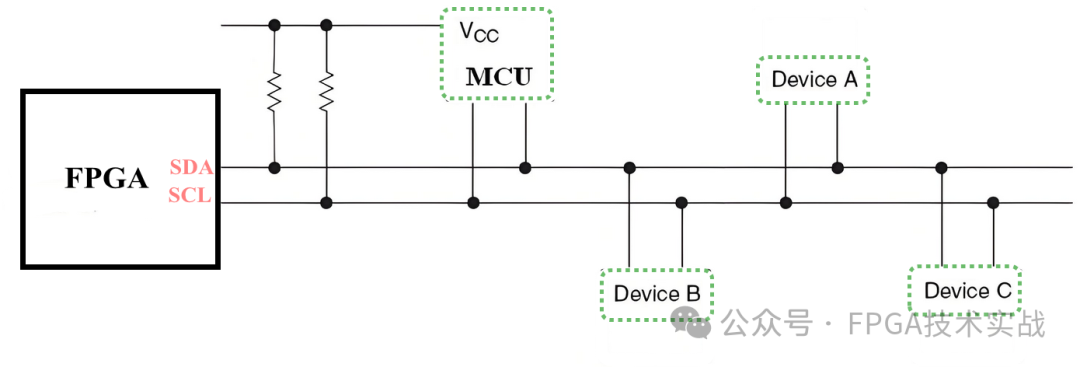

I2C 包含 2 條線路:1 條為 SCL(串行時鐘),另 1 條為 SDA(串行數據)。這 2 條線路都必須通過電阻上拉到 Vcc。借助使用 I2C 多路復用器可訪問各條通道以連接外設,還可通過電平移位器來轉換這 2 條 I2C 線路/信號上的電壓電平。

注:SCL 為時鐘信號,SDA 為數據信號。

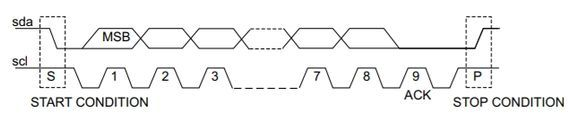

I2C 的數據傳輸格式如下所述。

單次數據傳輸包含 9 個時鐘脈沖,用于驅動 8 位數據和 1 位 ACK/NACK。

數據傳輸幀包含 1 個 START 和 1 個 STOP 條件。

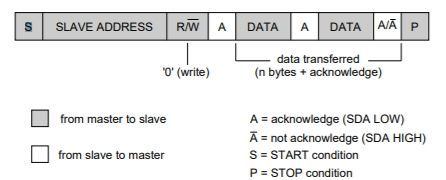

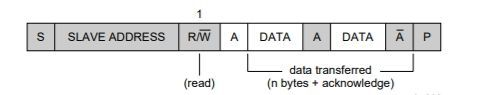

地址類型傳輸的啟動順序為:1 個 START 條件,后接 1 個 7 位/10 位地址、1 個 1 位 R/~W 和 1 個 1 位 ACK/NACK。隨后,數據類型傳輸包含 8 位數據和 1 位 ACK/NACK。

I2C 總線條件

啟動 (Start) 條件 - 在 SDA 上執行從高到低轉換時,SCL 線路應處于高位。

停止 (Stop) 條件 - 在 SDA 上執行從低到高轉換時,SCL 線路應處于高位。

數據有效性 - 當 SCL 處于高位狀態時,SDA 線路上的數據有效。

數據變更 - 當 SCL 處于低位狀態時,在 SDA 線路上發生數據變更。

總線繁忙 - 處于 START 與 STOP 條件之間時,總線處于繁忙狀態。

ACK - 在 SCL 的第 9 次時鐘脈沖時,SDA 應處于低位

NACK - 在 SCL 處于第 9 次時鐘脈沖時,SDA 應處于高位

1 主器件寫 (Master Write) 傳輸 Master Write 操作從 START 條件開始,后接 7 位/10 位從器件地址和 1 位寫操作(等于 0)。成功的從器件尋址應由從器件應答 (ACK)。之后,主器件啟動到從器件的數據寫入,從器件將在響應中提供 N-1 字節的 ACK。當 N-1 字節完成傳輸后,主器件會在第 N 字節傳輸上發送 Not Acknowledged (NACK) 以生成 STOP 條件。 主器件執行的從器件尋址操作失敗將導致總線上出現 NACK,故而將不啟動數據傳輸,并生成 STOP 條件。

2 主器件讀 (Master Read) 傳輸 Master Read 操作從 START 條件開始,后接 7 位/10 位從器件地址和 1 位讀操作(等于 1)。成功的從器件尋址應由從器件應答 (ACK)。后續,從器件會向主器件發送數據,主器件將在響應中提供 N-1 字節的 ACK。當主器件收到 N-1 字節后,它會在第 N 字節傳輸上發送 NACK 以生成 STOP 條件。 主器件執行的從器件尋址操作失敗將導致總線上出現 NACK,故而將不啟動數據讀取,并生成 STOP 條件。

3 時鐘拉伸 (Clock Stretching)

SCL 由處于活動狀態的總線主器件生成。從器件有時可強制時鐘處于低位以延遲主器件發送更多數據(或者在主器件嘗試切斷從器件時鐘前,從器件需要更多時間來準備數據)。這稱為時鐘拉伸或時鐘降頻。欲知詳情,請參閱https://learn.sparkfun.com/tutorials/i2c/all 的協議頁面

4 動態編程序列 使用如下示例中所示偽操作步驟并將其與您所看到的行為進行比較可便于您理解賽靈思 AXI IIC 仿真中的協議行為。 請保留以下步驟的副本,以便您后續在自己的設計中對其進行編輯,如省略或追加步驟。 或者,只需填入適用于的測試案例的任意內容即可。

5 初始化

1. 將 RX_FIFO 深度設置為最大值:設置 RX_FIFO_PIRQ = 0x _ _

2. 將 TX_FIFO 復位為 0x_ _

3. 啟用 AXI IIC、移除 TX_FIFO 復位,并禁用通用調用

6 從 IIC 器件地址0x_ _讀字節數據 1. 讀取狀態 (Status) 寄存器以檢查確認所有 FIFO 均為空,并且總線未處于繁忙狀態

2. 將 0x___ 寫入 TX_FIFO(設置啟動位,器件地址設置為 0x__,讀權限)

3. 將 0x___ 寫入 TX_FIFO(設置停止位,4 字節,將由 AXI IIC 接收)

4. 等待至 RX_FIFO 不為空為止。 a) 讀取 RX_FIFO 字節。 b) 如果讀取的是最后一個字節,則退出;否則,只要 RX_FIFO 不為空,則繼續檢查。

7 對IIC 從器件地址0x_ _寫byte數據 將數據置于從器件地址 0x__: 1. 讀取 SR 以檢查確認所有 FIFO 均為空,并且總線未處于繁忙狀態

2. 將 0x___ 寫入 TX_FIFO(設置啟動位,器件地址,寫權限)

3. 將 0x__ 寫入 TX_FIFO(數據的從地址)

4. 將 0x__ 寫入 TX_FIFO(字節 1)

5. 將 0x__ 寫入 TX_FIFO(字節 2)

6. 將 0x__ 寫入 TX_FIFO(停止位,字節 x)

8 從 IIC 器件地址0x_ _讀字節數據 數據位于從地址 0x _ _。 首先,需要寫權限才能設置從器件地址,然后讀權限之后執行重復啟動。 1. 讀取狀態 (Status) 寄存器以檢查確認所有 FIFO 均為空,并且總線未處于繁忙狀態。

2. 將 0x_ _ _ 寫入 TX_FIFO(設置啟動位,器件地址設置為 0x__,寫權限)。

3. 將 0x__ 寫入 TX_FIFO(數據的從地址)。

4. 將 0x___ 寫入 TX_FIFO(設置重復啟動的啟動位,器件地址設置為 0x_ _,讀權限)。

5. 將 0x___ 寫入 TX_FIFO(設置停止位,4 字節,將由 AXI IIC 接收)。

6. 等待至 RX_FIFO 不為空為止。 a) 讀取 RX_FIFO 字節。 b) 如果讀取的是最后一個字節,則退出;否則,只要 RX_FIFO 不為空,則繼續檢查。

AXI IIC 仿真

本文隨附了一個在 Vivado 2018.1 工程中經過修改的仿真測試平臺。 請將所提供的測試平臺與 AXI IIC IP 配合使用。它已經過測試,可在 Vivado 環境中正常運行。 以下是根據 AXI IIC 產品指南(PG090)所提供的部分編程序列建議的示例。 以下提供了有關示例案例的說明:測試 1 - 建議的序列將數據置于從器件地址 0x6C(含 1 個數據字節)。 1. 讀取 SR 以檢查確認所有 FIFO 均為空,并且總線未處于繁忙狀態。 2. 將 0x1D8 寫入 TX_FIFO(設置啟動位,器件地址,寫權限)。

3. 將 0x212 寫入 TX_FIFO(停止位,最后一個字節)

測試 2 - 建議的序列將數據置于從器件地址 0x6C(含 2 個數據字節)。 1. 讀取 SR 以檢查確認所有 FIFO 均為空,并且總線未處于繁忙狀態。

2. 將 0x1D8 寫入 TX_FIFO(設置啟動位,器件地址,寫權限)。

3. 將 0x011 寫入 TX_FIFO(字節 1)。

4. 將 0x012 寫入 TX_FIFO(字節 2)。

5. 將 0x2EF 寫入 TX_FIFO(停止位,最后一個字節)

測試 3 - 建議的序列將數據置于從器件地址 0x6C(含 2 個數據字節)。使用錯誤的從器件地址重新啟動。 1. 讀取 SR 檢查總線未處于繁忙狀態并且確認所有 FIFO 均為空。

2. 將 0x1D8 寫入 TX_FIFO(設置啟動位,器件地址,寫權限)。

3. 將 0x011 寫入 TX_FIFO(字節 1)。

4. 將 0x012 寫入 TX_FIFO(字節 2)。

5. 將 0x2EF 寫入 TX_FIFO(停止位,最后一個字節)

6. 將 TX FIFO 復位

7. 將錯誤的地址 0x108 寫入 TX_FIFO(設置啟動位,器件地址,寫權限)。

測試 4 - 不建議 將數據置于從器件地址 0x6C(含 1 個數據字節以及 START 位和 STOP 位): 1. 讀取 SR 以檢查總線未處于繁忙狀態并確認所有 FIFO 均為空。

2. 將 0x3D8 寫入 TX_FIFO(設置啟動位,停止位,器件地址,寫權限)。 由于該字節為停止位,故將被視為最后一個字節。 對其將不會生成 TX FIFO 空中斷傳輸,因此它將產生總線不繁忙中斷。 根據 IIC 協議,我們不建議在任一字節中同時包含啟動位和停止位。 請參閱如下有關此行為的示例:

建議遵循測試案例 1、2 和 3 進行操作,但不建議使用測試案例 4。 這也將有助于您遵循編程序列來進行操作。 注釋: 1) 請留意 ISR interrupt(4) 而不是 interrupt(2),以檢測最后一個字節的結束位置。在 interrupt(2) 上會將監測到的最后一個字節前發生的中斷判定為正常。 2) 根據 IIC 協議,請勿將啟動位和停止位與數據/地址字節置于一處。

-

集成電路

+關注

關注

5420文章

11971瀏覽量

367372 -

I2C

+關注

關注

28文章

1537瀏覽量

127147

原文標題:【干貨分享】IIC 協議與編程序列

文章出處:【微信號:FPGA-EETrend,微信公眾號:FPGA開發圈】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

I2C總線通信原理 如何設計I2C總線電路

I2C總線的優缺點分析

I2C總線與Arduino的接口示例

I2C總線的工作模式介紹

I2C總線協議詳細解析

I2C總線故障排除技巧

TMS320C6000 DSP內部集成電路(I2C)模塊參考指南

TMS320VC5501/5502/5503/5507/5509 DSP內部集成電路(I2C)模塊參考指南

TMS320x280x、2801x、2804x內部集成電路(I2C)參考指南

有關內部集成電路總線(I2C或IIC)的基礎知識

有關內部集成電路總線(I2C或IIC)的基礎知識

評論