從1月份到現在,全球都被這個病毒鬧的不安生,地球村背景下,能獨善其身?都是環環相扣,一個一個的在封,然后一堆材料開始告急,特別是一個小國家,這一鬧,怎么弄?天朝,產生鏈算完整的,但一些關鍵元器件國外在把持著,根本無貨。

今天跟兄弟們聊聊時鐘。

大部分的技術資料都會告訴你,EMC設計重要點關注時鐘

為什么?因為是時鐘是EMC三要素中重要的騷擾源,所以要重點對待。

圖示是標準理論方波的時域和頻域波形,我們根據波形的頻譜來做具體的設計。大部分情況下,我們時鐘都是奇次諧波能量高,理論上偶次諧波為0,但事實上做不到。所以就單端時鐘而言,設計主要集中在奇次諧波上。

(1)你可以在時域內衰減幅度A,從而降低各諧波的幅度,實現頻域內的降低

(2)你可以通過加旁路電容,減緩上升沿,吸收雜波。

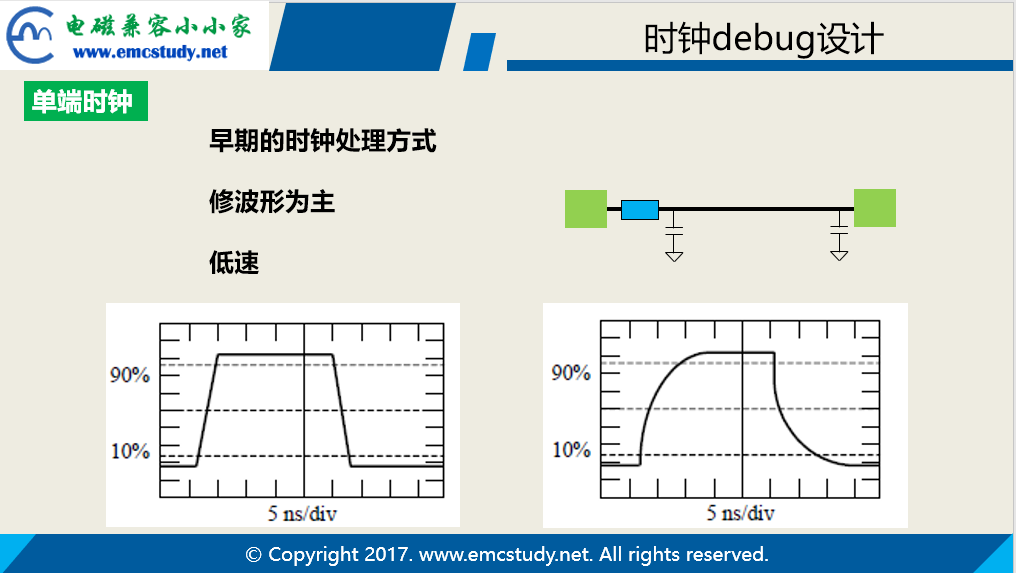

這是騷擾源能量降低基本的手法,也是最省心的,所以許多兄弟看到時鐘就一頓猛操作,遠場一看有點效果,都非常的開心,有時候為了達到某個裕量,揍的有點狠,比如電容加個100PF,電阻串上100ohm,甚至更大。當速率比較低的時候,系統是勉為其難的在工作,時間長了,系統工作是非常不穩定的。

你修的圖時域波形可能就像上圖一樣,已經快變形了,速率慢的時候負載端能正常識別,到了一定程度,基本就掛了,所以整改時悠著點。

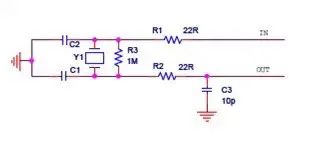

圖示是晶體的基本原理圖,除了原理上需要的R3、C1和C2之外,R1、 R2和C3組成了基本的EMC電路,大部分情況下還會多一個C4給R1(沒找到圖,懶得重新畫)。大部分兄弟都會盯著這四個器件一頓狂揍,某些時候效果很明顯,你可能就差哪幾個db,然后就沒有然后了。

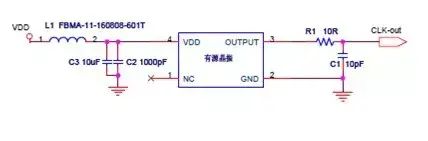

上圖是晶振的基本原理圖,電源VDD大部分情況下會做成圖示的那樣,LC濾波,但我們建議你最好做成PAI型濾波,去耦和旁路同時去做,電容從高到低都配上(高頻、中頻和低頻都配上)。輸出端的RC是標配,兄弟們都會根據自己的測試結果來調整。

上面的內容是不是都懂,都會,好像不用我太多說。

咳咳

以我個人多年的經驗,這兩個源做基本的衰減和濾波足矣,不必過頭。

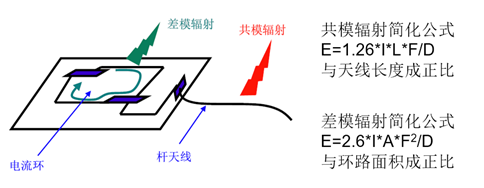

先回憶一下楊老師的經典公式

公式中差模輻射因其跟信號整個環路相關,如果你的電路都是短距離傳輸的,比如我們上面討論的驅動時鐘,都離IC很近,那么其差模分量還是很小的。盡管能量不高,但我們還是很注重在PCB設計時控制其環路面積,所以大部分的guideline都會要求你盡量靠近IC。共模輻射與天線長度成正比,大部分兄弟都會忽略這一點,因為在實際電路中并沒有明顯異常的天線在。

但是大部分的EMI問題都是因為多次串擾耦合的問題,這句話是不是耳熟,因為我講課時常說,老工程師也這么說。其中重要的原理就是時鐘電路周圍存在許多未知的L,因為共地和共電源的問題,這些能量會多次串擾找到一個合適的L發射出去。

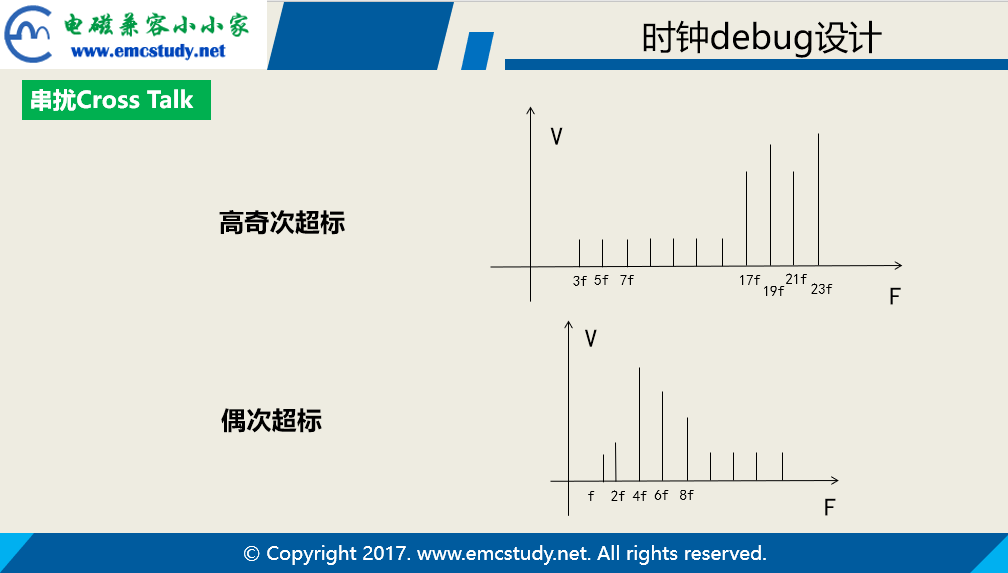

然后就出現了類似上圖的現象,是不是常見,這種情況,你把時鐘揍死了,看到的效果都一般般。然后有兄弟感慨,為啥我處理半天時鐘咋沒反應呢,我的時鐘明明就對應著他呀。老工程師會心一笑,too young。

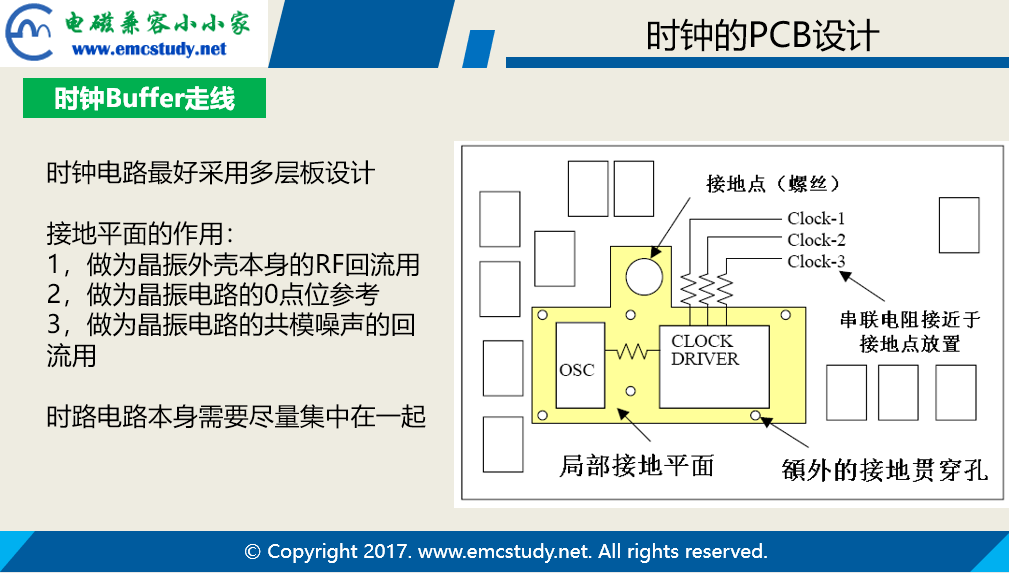

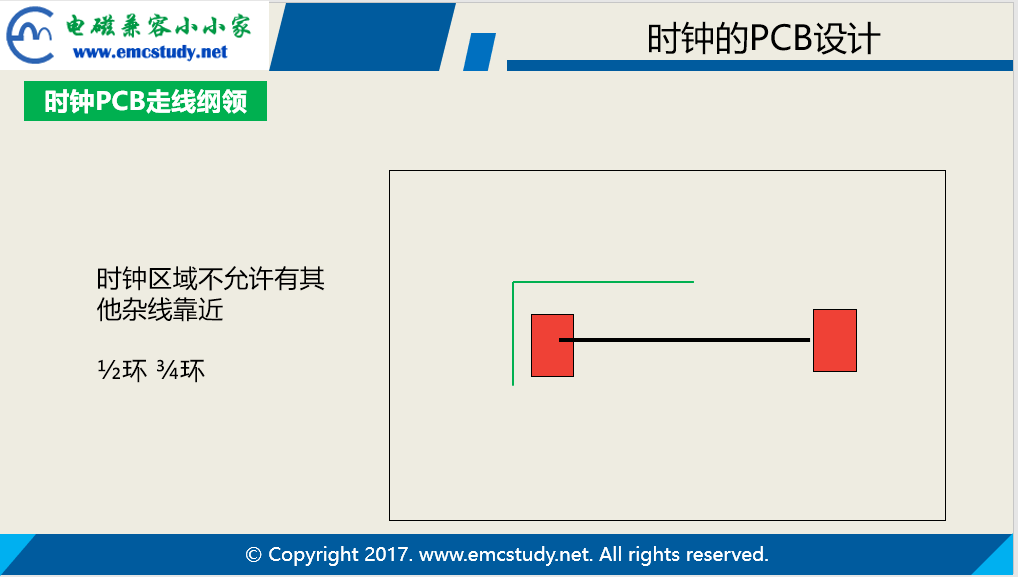

為了減小后期一些莫名其妙的串擾,所以會對時鐘電路周圍做一些規則限制。上面是另一經典的圖,許多老師都會引用,結合我們上面說的原理,這時候理解這個圖是不是輕松多了。為了降低時鐘電路能量可能的串擾,首先需要多層GND平面盡量多拾取時鐘電路產生的能量(自行腦補這部分電路產生的電力線和磁力線分布圖),這部分能量盡量少往空中耦合,必要的時候可以采用局部屏蔽(示意圖中有BUFFER)。其次盡量將時鐘線走到內層(原理同樣是控制電力線和磁力線在空中的分布)。

上述的要求,相對來說容易做到,基本沒有歧義,但這還是屬于騷擾源設計范疇。

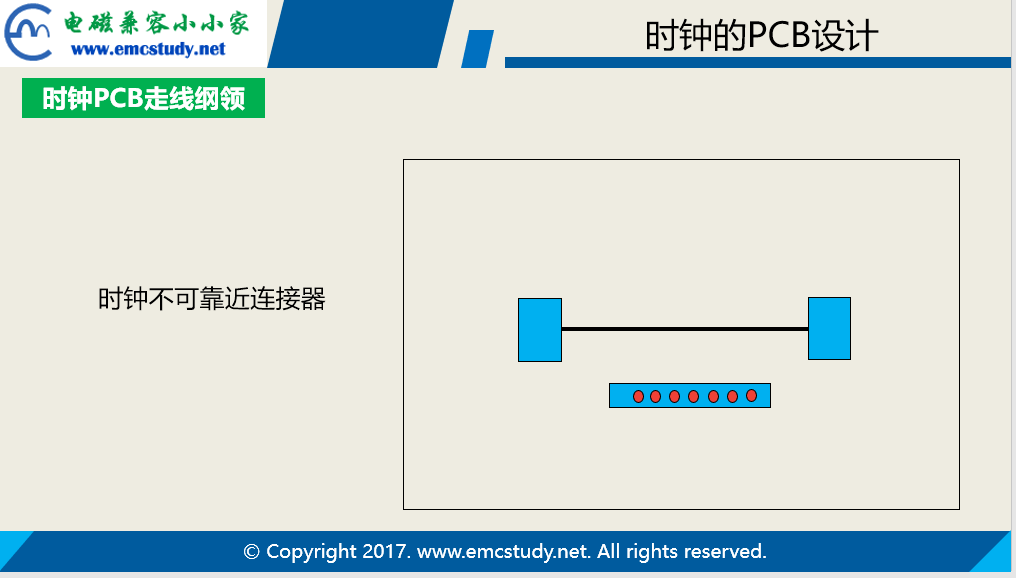

當時鐘電路有連接器時,就會出現主動拾取干擾會二次耦合發射的問題,這個相對容易發現,原理上做濾波,破壞天線效應即可,然后就能看到,連接器的pin上加了一堆的濾波電容。

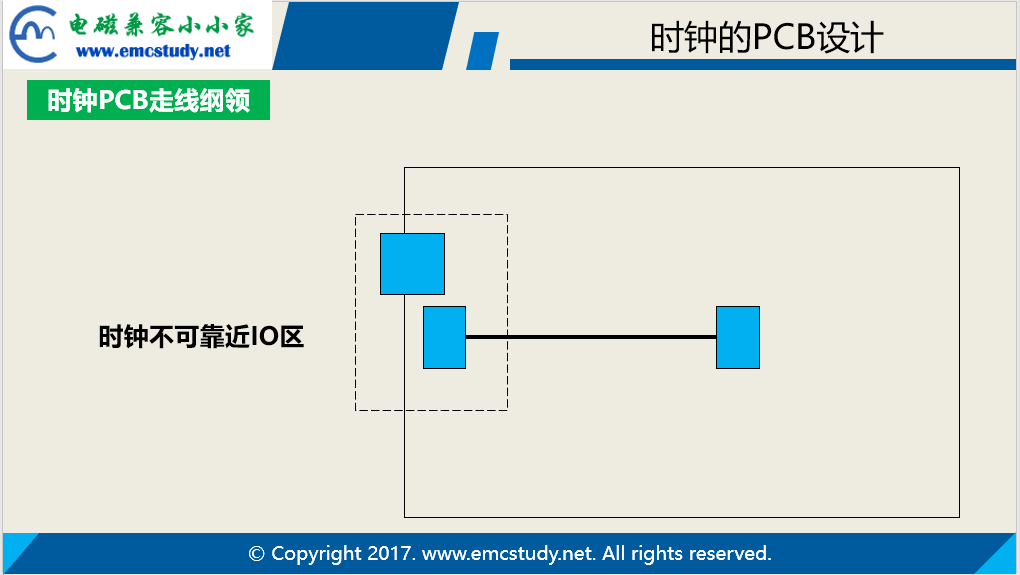

時鐘電路如果靠近IO,這個天線效應同樣容易理解,但是因為線纜較長,會帶來其他的問題。

這個大部分人很難處理,大部分的借口是板子密度太高,但是這是我們工程上見到的最多的隱藏天線,這時候你會發現我們時鐘線走在內層是多么的明智。

這些雜線在PCB設計時就是重中之重了。

(1) 內層走線,且與時鐘不同層

(2) 3W法則(10W或更高)。

難就難在很難全部做到,有時候這么做了,卻是過設計,但你不這么做,可能是隱患。這種一次側的耦合相對容易發現,現實中因為低層板設計,將EMI設計提高了好幾個難度等級。越是這樣,后期的對策越難做。

所以,在設計之初,盡量多做一些規則檢查,即使做不全,后期排查時也會做到心中有數。

最后,我依然十分誠懇的建議兄弟們,把注意力多放在串擾耦合中,多年的高速設計(通信行業中25GHz這樣的高速)經驗會告訴我們,串擾是EMI設計第一殺手。

-

電路

+關注

關注

173文章

6028瀏覽量

175109 -

旁路電容

+關注

關注

7文章

179瀏覽量

25291 -

EMC設計

+關注

關注

6文章

266瀏覽量

40095

原文標題:聊聊EMC設計中的時鐘設計

文章出處:【微信號:EMCSTUDY,微信公眾號:電磁兼容小小家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

EMC設計—PCB高級EMC設計

EMC電路基礎知識

EMC外圍電路常用器件

時鐘電路的組成與設計要點介紹

EMC 時鐘信號的噪聲源頭是什么?

硬核干貨 - 講EMC說接地

直播預告 I 講EMC說接地

靈活多元的EMC學習方案

時鐘信號的驅動是什么

綜述板級EMC設計關鍵要點及應用策略

EMC設計重要點關注時鐘

EMC設計重要點關注時鐘

評論