在數字電路設計中,時鐘信號扮演著至關重要的角色。理想的時鐘信號是一串無限連續的脈沖序列,除了電平要求外,其邊沿應非常陡峭,有些系統還要求時鐘具有50%的占空比。從電磁兼容性(EMC)的角度來看,理想的時鐘信號是一個輻射源,會產生很強的EMC干擾。

在交換機系統中,周期性地重復傳輸固定碼(例如54H碼)實際上也會產生EMC干擾,并對相鄰信號線產生嚴重干擾。因此,對時鐘信號進行單獨討論是因為在數字系統中,整個系統的工作都以時鐘信號為參考,時鐘信號的質量直接關系到系統的工作質量。然而,當時鐘信號從時鐘源出發、經過驅動、線路傳輸,最后到達負載端時,很難保持其在時鐘源時的模樣。

在負載端看到的時鐘信號可能會發生上升、下降沿的改變,也可能發生占空比的變化,還可能有到達不同負載的時間發生改變(相位變化)的問題等。

為了確保時鐘到達不同負載的相位相同,僅采用專用時鐘驅動器件是不夠的,還需要考慮匹配、線長、負載等因素。以下是一些可以采取的措施來控制:

注意驅動器的傳輸延遲:選擇合適的驅動器可以減少傳輸延遲對時鐘信號的影響。

在時鐘的傳輸路徑上使用相同的驅動器:這樣可以確保各個路徑上的驅動器具有相似的性能和特性。

平衡各路徑的線路延遲:通過調整線路長度或使用延遲補償技術來平衡各個路徑上的線路延遲。

使用相同的線路匹配方法:確保各個路徑上的線路匹配方法一致,以減少反射和信號失真。

平衡各路徑的負載:有時可能需要在負載處增加電容來達到平衡負載的目的。

-

驅動

+關注

關注

12文章

1908瀏覽量

86621 -

數字電路

+關注

關注

193文章

1637瀏覽量

81654 -

時鐘信號

+關注

關注

4文章

466瀏覽量

29115

發布評論請先 登錄

在ADS1281的數據手冊當中沒有時鐘引腳CLK的等效輸入電容,其多片ADC會對時鐘源信號產生影響嗎?

使用時鐘信號驅動FF的CE引腳并啟用FIFO的線路

為什么寫入閃存會擾亂時鐘頻率?

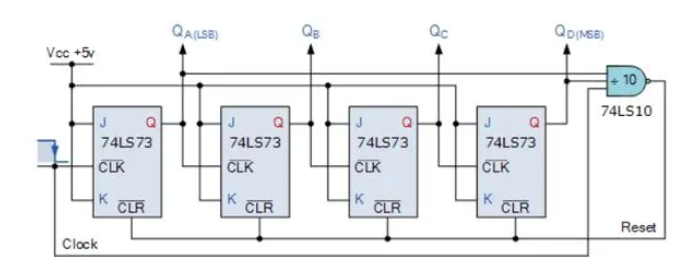

數字鐘實驗電路的設計與仿真

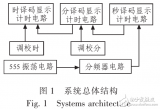

基于FPGA的數字集成時鐘電路設計方案詳解

基于Multisim10軟件的數字鐘電路的設計與仿真

FPGA設計的7項原則介紹

FPGA中的晶振大小多少比較合適?為什么會用到兩個晶振?

什么是同步邏輯和異步邏輯?同步電路與異步電路有何區別?

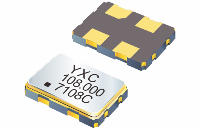

YXC可編程晶振,頻點100MHz,封裝5032,應用于AI服務器

了解反饋振蕩器,看這篇文章就夠了

時鐘信號的驅動是什么

時鐘信號的驅動是什么

評論