之前看到有評論讓我談?wù)刵oise。我絞盡腦汁想了很久,好像按照KT/C的那套講下去,我也想不出什么有趣的角度讓讀者能夠印象深刻。畢竟,有些時(shí)候,靈光一現(xiàn)的idea確實(shí)是可遇不可求……

閑扯了這么多,還是回歸正題,我想隨便談?wù)?a href="http://m.xsypw.cn/analog/" target="_blank">模擬電路里面的一些技術(shù)。說是講“術(shù)”,其實(shí)我想講“道”。畢竟,萬法歸一,我們的最終目的還是“道”。

從noise開始談?wù)劇?/p>

早上我問王道長,“你說怎么設(shè)計(jì)low noise的電路?”王道長隨手扔過來他身邊Razavi那本RF的書:“看LNA design!比如……”他給我看了section 5.3.6那個電路。我們先不看具體的電路實(shí)現(xiàn),就談?wù)勂渲械南敕ā?/p>

1. Correlated Double Sampling

提到noise,大家會想到怎么對付它?假如我是個萌新,什么都不太會,我會怎么想才能去掉這種非理想的東西?好吧,打個比方,你上次考試錯了一道題,為了避免下次考試再錯,你會怎么辦?弄個錯題本,把錯題記在上面,好好研究一下,下次就不太容易錯了。

OK,這樣子,可以引入Correlated Double Sampling (CDS)的概念了。也就是說,第一步,我先瀟灑的犧牲一段時(shí)間,專門拿來sample offset。(對應(yīng)于:我可以允許月考做錯,因?yàn)椴幌敫呖甲鲥e嘛!)

(在我看來,offset就是low frequency noise,所以大部分offset cancellation都是可以用來對付1/f noise的)

然后,第二步,就是把包含著offset的信息去跟真正的電路功能(放大,積分,balabala)做減法,減去其中的非理想因素。換句話說,假設(shè)沒有第一步,只有第二步,電路的輸出受到了offset的影響,輸出是不對的。我現(xiàn)在多出來的第一步(錯題本上的錯題記錄),就是為了去抵消offset對電路的影響。

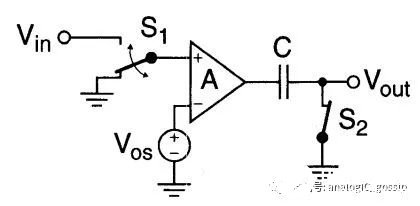

Fig. 1 最直觀的想法,把offset存在輸出的C上面

Fig.1 是簡單粗暴的辦法(對應(yīng)于: 我就記住這道錯題了,保證下次一定不錯!),直接在輸出端拿到offset,等著下一次工作的時(shí)候,直接從輸出減掉。

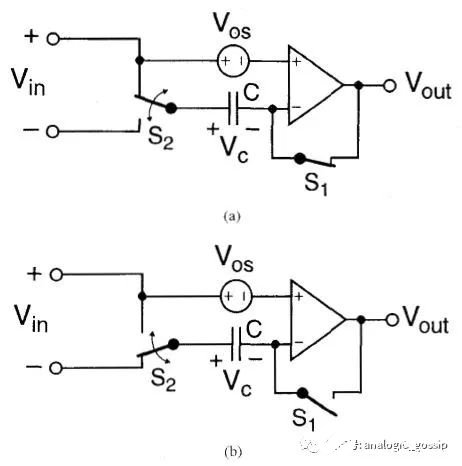

Fig. 2 把offset存在輸入端的C上面,(a) offset sampling phase, (b) normal operation phase

或者謹(jǐn)慎一點(diǎn)點(diǎn),因?yàn)橐话愕腶mplifier的增益很大,萬一offset直接讓輸出飽和了,豈不是玩完?那就還是放在輸入端,這樣在Fig.2 的C上面,存了一個大小等于Vos的電壓。(對應(yīng)于: 我跑去研究了這道錯題的知識點(diǎn),下次考這個知識點(diǎn)有關(guān)的題目,我都不會錯!)下次正常工作的時(shí)候,在輸出端就減去offset,豈不美滋滋?

上面CDS,(或者有人說叫auto-zeroing,我覺得是差不多的意思)能好好工作有個前提條件:你得專門騰出一點(diǎn)時(shí)間來給sample offset這一步。在傳統(tǒng)的switched capacitor電路里面,CDS非常普遍且好用。但是如果沒有clock呢?咋辦?

2. Feedback

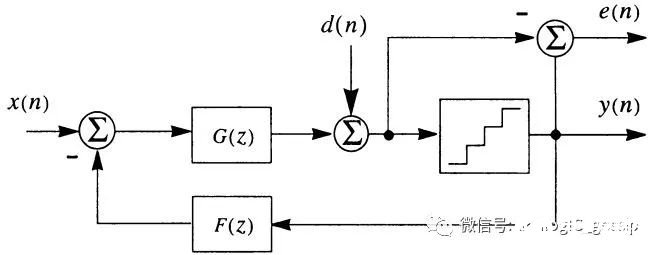

回到前面王道長提到的LNA設(shè)計(jì),Razavi那本書p300, 有個很直觀的圖:

Fig. 3 RF microelectronics / Behzad Razavi.—2nd ed. 2011, page 300

其實(shí)concept很簡單,就是我給你整出個輔助的支路Auxiliary Amplifier,讓noise可以剛好被這個feedback的支路給cancel掉。至于電路的具體實(shí)現(xiàn),大家可以去看書。當(dāng)然,必須指出的是,這個輔助電路要非常理想的工作,具體的一些參數(shù)匹配是需要做到很精確的。(畢竟需要實(shí)時(shí)的工作,不像CDS慢了半拍……) 對比前面提到的CDS技術(shù),其實(shí)是自己match自己的offset,匹配難度其實(shí)小很多。

再說遠(yuǎn)一些,大家記得Miller 電容的計(jì)算吧?實(shí)際電路設(shè)計(jì)中,那個Miller電阻其實(shí)還挺煩人的,大家選擇參數(shù)的時(shí)候,多跑跑Corner和MC,你會懂的。

再再扯遠(yuǎn)一點(diǎn),模擬電路里面,最最經(jīng)典的feedback結(jié)構(gòu)是啥?PLL啊!多么完美的loop,完全符合了工科美學(xué)的審美!就跟我們思考的時(shí)候,從來不會管我腦子里面哪塊區(qū)域的哪些腦細(xì)胞被激發(fā)了,我們不需要一步步follow PLL里面具體怎么feedback的。總之,只要loop設(shè)計(jì)得好,帶寬增益啥的都夠,我們的output就基本上可以跟我們設(shè)想的一樣。對比一些粗暴的調(diào)整loop參數(shù)的應(yīng)用,看什么看?我說的就是deep learning了……一個完美的feedback loop,設(shè)計(jì)完了,自適應(yīng)就好,還要調(diào)節(jié)參數(shù),呲呲,我們模擬電路比它們智能,嘿嘿!

3. Dithering

說了上面兩種方法,我們再談?wù)勔粋€特別有趣的idea:Dithering。為了去掉不可控的noise,人為加noise。

前面的辦法都是為了減小noise而迎難而上,dithering卻是個很有趣的辦法:為了減小quantization noise,spur或者deadzone,人為的增加noise,通常可以得到更好的dynamic range。維基百科說:Dither is an intentionally applied form of noise used to randomize quantization error。

其實(shí)說到底,有些非理想的因素,在頻域表現(xiàn)為單個頻段的干擾,比如quantization noise,嚴(yán)重的影響了最終的dynamic range。但是人為的加入類似于白噪聲一樣的dithering(一般用Pseudo Random Number Generator (PRNG)生成),等效于用白噪聲把這些毛刺給smooth抹平了。

責(zé)任編輯:pj

-

電阻

+關(guān)注

關(guān)注

87文章

5618瀏覽量

174634 -

電容

+關(guān)注

關(guān)注

100文章

6242瀏覽量

153697

發(fā)布評論請先 登錄

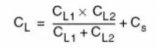

電源濾波電容大小計(jì)算

電腦主板中電容電阻的作用及品牌推薦

什么是阻抗?與電阻和電抗的區(qū)別詳解(上)

電阻器與電容器的區(qū)別

村田貼片電阻電容報(bào)價(jià)是多少

精密貼片電阻與普通貼片電阻的區(qū)別

淺談鉭電容和陶瓷電容的區(qū)別

直流電阻和交流電阻區(qū)別詳解

聚徽-電容屏跟電阻屏的區(qū)別

電容與電阻的計(jì)算區(qū)別

電容與電阻的計(jì)算區(qū)別

評論