DDS信號發生器采用直接數字頻率合成(Direct Digital Synthesis,簡稱DDS)技術,把信號發生器的頻率穩定度、準確度提高到與基準頻率相同的水平,并且可以在很寬的頻率范圍內進行精細的頻率調節。采用這種方法設計的信號源可工作于調制狀態,可對輸出電平進行調節,也可輸出各種波形。

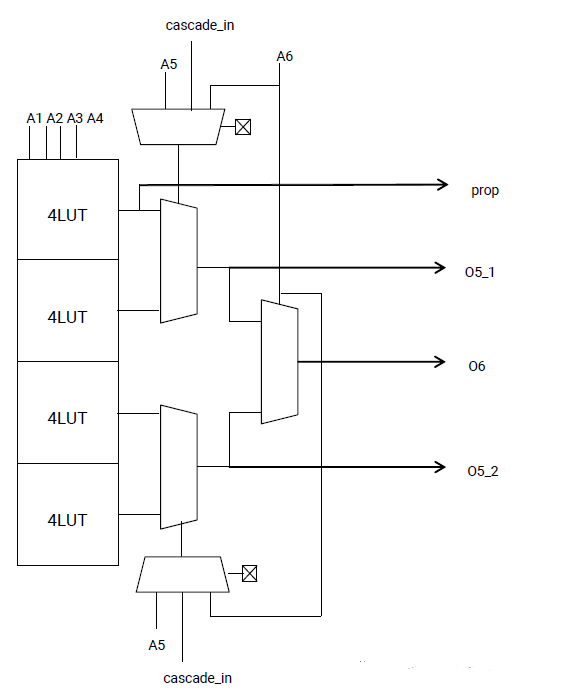

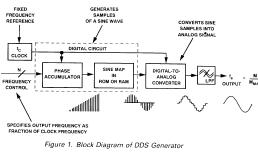

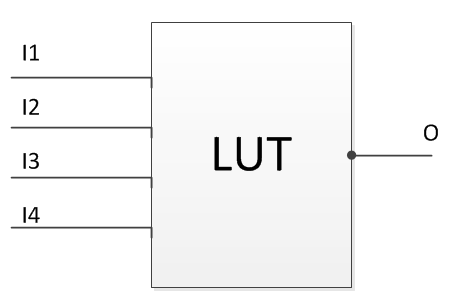

DDS(Direct Digital Synthesis)直接數字頻率合成技術由USA J.Tierncy首先提出。它是一種以數字信號處理理論為基礎,從相位概念出發直接合成所需波形的一種新的全數字技術的頻率合成方法。DDS主要出現在數字混頻系統中。在數字混頻中,通過DDS產生正交的本地振蕩信號即正、余弦信號與輸入信號相乘實現頻譜搬移,如通信系統的調制、解調。目前FPGA實現DDS有三種途徑:基于IIR濾波器的實現方法、基于查找表LUT的實現方法以及基于CORDIC算法的實現方法。其中采用LUT的方法較為通用且比較容易實現。

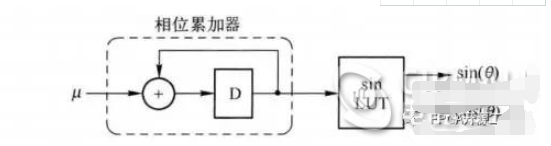

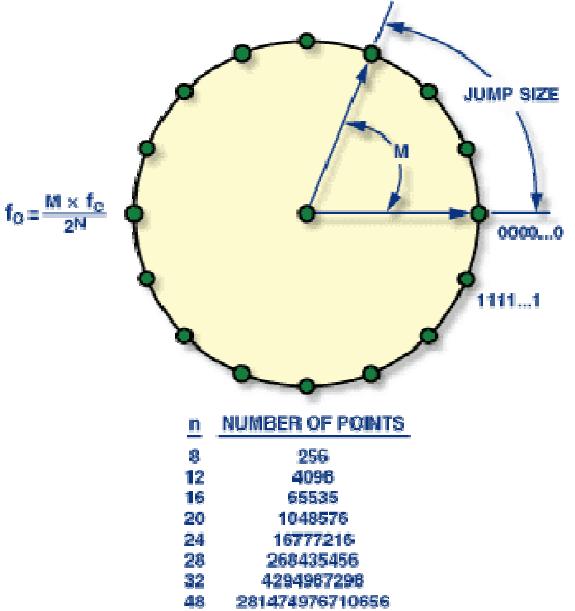

一個典型的基于LUT的DDS系統由相位累加器和波形存儲器兩部分構成,如圖1所示。圖中相位累加器的位寬為nbit,步進值為μ,LUT的深度N為2n,寬度為Lbit。LUT中依相位順序存儲一個周期的波形數據。

-

DDS

+關注

關注

22文章

672瀏覽量

154464 -

LUT

+關注

關注

0文章

50瀏覽量

12854

發布評論請先 登錄

初識FPGA CLB之LUT實現邏輯函數

使用的LUT觸發器對的數量與Slice Register和Slice LUT的關系是什么?

如何使用DDS IP核生成任意波形?

LUT名字的數字含義是什么?

DDS,什么是DDS,DDS的結構

DDS是什么意思,DDS結構,DDS原理是什么

LUT如何構成邏輯函數

物理可級聯的LUT的優勢在哪?

FPGA——LUT/FDRE/FDCE/FDSE/FDPE

MAX6828LUT+T PMIC - 監控器

基于LUT的DDS系統設計原理

基于LUT的DDS系統設計原理

評論